External Memory Interface (EMIF)

综述

General Description

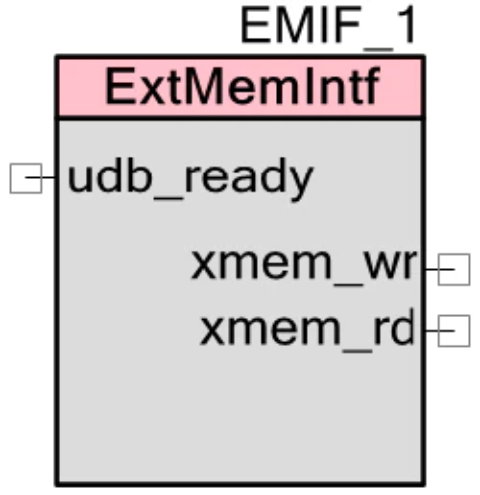

The EMIF component enables access by the CPU or DMA to memory ICs external to the PSoC™ 3/PSoC™ 5LP. It facilitates setup of the EMIF hardware, as well as UDBs and GPIOs as required. The EMIF can control synchronous and asynchronous memories without the need to configure any UDBs in synchronous and asynchronous modes. In UDB mode, UDBs must be configured to generate external memory control signals.

- 8-, 16-, 24-bit address bus width

- 8-, 16-bit data bus width

- Supports external synchronous memory

- Supports external asynchronous memory

- Supports custom interface for memory

- Supports a range of speeds of external memories (from 5 to 200 ns)

- Supports external memory power-down, sleep, and wakeup modes

支持