# **Errata Sheet**

Rel. 1.2, 17.01.2013

Device XC878CLM Series

Marking/Step AC

Package PG-LQFP-64

This Errata Sheet describes the deviations from the current user documentation. The module oriented classification and numbering system uses an ascending sequence over several derivatives, including already solved deviations. So gaps inside this enumeration can occur.

This Errata Sheet covers the following devices:

- XC878CM-13/16FF

- XC878CLM-13/16FF

#### Table 1 Current Documentation

| XC878CLM User's Manual | V1.1 | Apr 2009 |

|------------------------|------|----------|

| XC87xCLM Data Sheet    | V1.5 | Mar 2011 |

Each erratum identifier follows the pattern Module\_Arch.TypeNumber:

- Module: subsystem or peripheral affected by the erratum

- Arch: microcontroller architecture where the erratum was firstly detected.

- AI: Architecture Independent (detected on module level)

- CIC: Companion ICsTC: TriCore (32 bit)

- X: XC1xx / XC2000 (16 bit)

- XC8: XC800 (8 bit)none: C16x (16 bit)

- **Type**: none Functional Deviation; 'P' Parametric Deviation; 'H' Application Hint; 'D' Documentation Update

Number: ascending sequencial number within the three previous fields. As

this sequence is used over several derivatives, including already solved

deviations, gaps inside this enumeration can occur.

Note: Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only.

The specific test conditions for EES and ES are documented in a separate Status Sheet.

| Table 2 | History List |        |

|---------|--------------|--------|

| Version | Date         | Remark |

| 1.0     | 11.09.2009   |        |

| 1.1     | 26.05.2010   |        |

Table 3 Errata fixed in this step

| Errata        | Short Description                                   | Chg   |

|---------------|-----------------------------------------------------|-------|

| T2CCU_XC8.001 | External Trigger of ADC when CCT of T2CCU overflows | Fixed |

|               | Overnows                                            |       |

Table 4 Functional Deviations

| Functional Deviation | Short Description                                                     | Chg | Pg |

|----------------------|-----------------------------------------------------------------------|-----|----|

| BROM_XC8.006         | IRAM data is corrupted after any warm reset                           |     | 7  |

| CD_XC8.001           | Set and Clear of Error Bit in CORDIC Linear Vectoring Mode            |     | 7  |

| CD_XC8.002           | Data Fetch to CD_STATC Register may capture an incorrect error status |     | 8  |

| MultiCAN_AI.040      | Remote frame transmit acceptance filtering error                      |     | 8  |

| MultiCAN_AI.041      | Dealloc Last Obj                                                      |     | 9  |

Table 4 Functional Deviations (cont'd)

| Functional      | Short Description                                           | Chg | Pg        |

|-----------------|-------------------------------------------------------------|-----|-----------|

| Deviation       |                                                             |     |           |

| MultiCAN_AI.042 | Clear MSGVAL during transmit                                |     | 9         |

|                 | acceptance filtering                                        |     |           |

| MultiCAN_AI.043 | Dealloc Previous Obj                                        |     | 10        |

| MultiCAN_AI.044 | RxFIFO Base SDT                                             |     | 11        |

| MultiCAN_AI.045 | OVIE Unexpected Interrupt                                   |     | 11        |

| MultiCAN_AI.046 | Transmit FIFO base Object position                          |     | 11        |

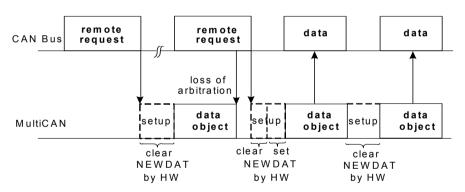

| MultiCAN_TC.025 | RXUPD behavior                                              |     | 12        |

| MultiCAN_TC.026 | MultiCAN Timestamp Function                                 |     | 12        |

| MultiCAN_TC.027 | MultiCAN Tx Filter Data Remote                              |     | 13        |

| MultiCAN_TC.028 | SDT behavior                                                |     | 13        |

| MultiCAN_TC.029 | Tx FIFO overflow interrupt not generated                    |     | 14        |

| MultiCAN_TC.030 | Wrong transmit order when CAN error at                      |     | 16        |

|                 | start of CRC transmission                                   |     |           |

| MultiCAN_TC.031 | List Object Error wrongly triggered                         |     | 16        |

| MultiCAN_TC.032 | MSGVAL wrongly cleared in SDT mode                          |     | 17        |

| MultiCAN_TC.035 | Different bit timing modes                                  |     | 17        |

| MultiCAN_TC.037 | Clear MSGVAL                                                |     | 19        |

| MultiCAN_TC.038 | Cancel TXRQ                                                 |     | 20        |

| SYS_XC8.001     | MOV (direct, direct) instruction might                      |     | 20        |

|                 | cause a wrong value to be written to the                    |     |           |

|                 | destination register                                        |     |           |

| SYS_XC8.003     | Brownout Reset                                              | New | <b>26</b> |

| T2CCU_XC8.003   | T2CCU Capture Functions                                     |     | 26        |

| UART_XC8.002    | Bits FDEN and FDM in UART1_FDCON                            |     | 26        |

|                 | SFR cannot be Written by Read-Modify-<br>Write Instructions |     |           |

Table 5 Deviations from Electrical- and Timing Specification

| AC/DC/ADC | Short Description | Chg | Pg |

|-----------|-------------------|-----|----|

| Deviation |                   |     |    |

Table 6 Application Hints

| Hint             | Short Description                                                       | Chg | Pg |

|------------------|-------------------------------------------------------------------------|-----|----|

| ADC_XC8.H001     | Arbitration mode when using external                                    |     | 29 |

|                  | trigger at the selected input line REQTR                                |     |    |

| BROM_XC8.H001    | SYSCON0.RMAP handling in ISR                                            |     | 29 |

| CCU6_XC8.H001    | Pin Configuration of CCU6 Functions                                     |     | 30 |

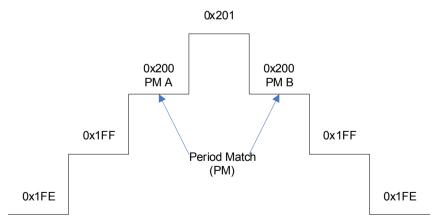

| CCU6_XC8.H002    | CCU6 PM event in center-aligned mode                                    |     | 30 |

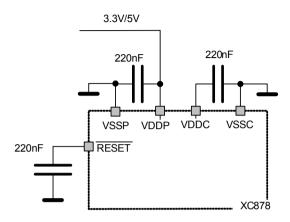

| EVR_XC8.H002     | Enhancement for Noise Immunity                                          |     | 31 |

| FLASH_XC8.H004   | Disable TRAP When Calling ROM Flash Routine                             |     | 32 |

| LIN_XC8.H001     | LIN BRK field detection logic                                           |     | 32 |

| MultiCAN_AI.H005 | TxD Pulse upon short disable request                                    |     | 33 |

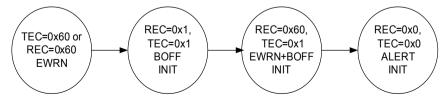

| MultiCAN_AI.H007 | Alert Interrupt Behavior in case of Bus-<br>Off                         | New | 33 |

| MultiCAN_TC.H002 | <b>Double Synchronization of receive input</b>                          |     | 34 |

| MultiCAN_TC.H003 | Message may be discarded before transmission in STT mode                |     | 34 |

| MultiCAN_TC.H004 | Double remote request                                                   |     | 35 |

| PIN_XC8.H001     | Current over GPIO pin must not source $V_{\text{DDP}}$ higher than 0.3V |     | 35 |

| PM_XC8.H001      | Clock source selection before entering power-down mode                  |     | 36 |

| PM_XC8.H002      | SAK product variant does not support power-down mode                    |     | 36 |

| SYS_XC8.H001     | Usage of the Bit Protection Scheme                                      |     | 36 |

Table 6 Application Hints (cont'd)

| Hint         | Short Description                                                                  | Chg | Pg |

|--------------|------------------------------------------------------------------------------------|-----|----|

| SYS_XC8.H002 | External Clock switching routine after a WDT reset                                 |     | 37 |

| SYS_XC8.H003 | Effective write for Read-Modify-Write instructions of two bytes, one machine cycle | New | 37 |

| T2_XC8.H003  | Accessing Timer 21 registers                                                       |     | 38 |

# 2 Functional Deviations

## BROM XC8.006 IRAM data is corrupted after any warm reset

After any warm reset (i.e. reset without powering off the device), boot up via User Mode affects certain IRAM data.

The affected IRAM address ranges are:

$(1) 00_{H} - 07_{H}$

#### Workaround

None

# <u>CD\_XC8.001</u> Set and Clear of Error Bit in CORDIC Linear Vectoring Mode

In linear vectoring mode, the Error bit of register CD\_STATC is set immediately on detecting overflow. When detected between iterations – the Error status is not held internally till the end of the calculation.

As the Error bit is defined such that it is cleared on any read access to the register (e.g. JB BSY), SW checking of the Error bit only at the end of calculation may miss to detect an overflow error condition.

#### Workaround

Especially in linear vectoring mode, if the error condition setting of Error bit must be detected, any read access should be done on the whole CD\_STATC register (e.g. MOV) and the Error bit checked in all read instances.

# <u>CD\_XC8.002</u> Data Fetch to CD\_STATC Register may capture an incorrect error status

The error bit CD\_STATC.ERROR is defined such that the bit is cleared on any read access to the register. Therefore, it is necessary to perform a data fetch on the register and check for the error bit in order not to lose the error status.

However, if CORDIC is clocked at two times PCLK and the execution time of the read instruction is more than one machine cycle, multiple read accesses will be performed on the CD\_STATC register and the error bit will be cleared by the time the CPU performs the final read. As a result, the CPU does not capture the correct error status.

There is no problem if the CORDIC is clocked at the same frequency as PCLK.

#### Workaround

The following workarounds can be used to avoid incorrect data fetching from the CD\_STATC register:

- The PUSH dir and POP dir instructions can be used to read the CD\_STATC register in all conditions;

- The following one-machine cycle MOV instruction can be used to read the CD\_STATC register when the CORDIC is clocked at two times of PCLK:

- MOV A, dir

# <u>MultiCAN\_AI.040</u> Remote frame transmit acceptance filtering error

#### Correct behaviour:

Assume the MultiCAN message object receives a remote frame that leads to a valid transmit request in the same message object (request of remote answer), then the MultiCAN module prepares for an immediate answer of the remote request. The answer message is arbitrated against the winner of transmit acceptance filtering (without the remote answer) with a respect to the priority class (MOARn.PRI).

Wrong behaviour:

Assume the MultiCAN message object receives a remote frame that leads to a valid transmit request in the same message object (request of remote answer), then the MultiCAN module prepares for an immediate answer of the remote request. The answer message is arbitrated against the winner of transmit acceptance filtering (without the remote answer) with a respect to the CAN arbitration rules and not taking the PRI values into account.

If the remote answer is not sent out immediately, then it is subject to further transmit acceptance filtering runs, which are performed correctly.

#### Workaround

Set  ${\tt MOFCRn.FRREN=1_B}$  and  ${\tt MOFGPRn.CUR}$  to this message object to disable the immediate remote answering.

## MultiCAN Al.041 Dealloc Last Obj

When the last message object is deallocated from a list, then a false list object error can be indicated.

#### Workaround

Ignore the list object error indication that occurs after the deallocation of the last message object.

or

Avoid deallocating the last message object of a list.

## MultiCAN\_AI.042 Clear MSGVAL during transmit acceptance filtering

Assume all CAN nodes are idle and no writes to <code>MOCTRn</code> of any other message object are performed. When bit <code>MOCTRn.MSGVAL</code> of a message object with valid transmit request is cleared by software, then MultiCAN may not start transmitting even if there are other message objects with valid request pending in the same list.

#### Workaround

Do not clear MOCTRn.MSGVAL of any message object during CAN operation. Use bits MOCTRn.RXEN, MOCTRn.TXENO instead to disable/reenable reception and transmission of message objects.

or

Take a dummy message object, that is not allocated to any CAN node.

Whenever a transmit request is cleared, set MOCTRM.TXRQ of the dummy message object thereafter. This retriggers the transmit acceptance filtering process.

## MultiCAN Al.043 Dealloc Previous Obj

Assume two message objects m and n (message object n = MOCTRm.PNEXT, i.e. n is the successor of object m in the list) are allocated. If message m is reallocated to another list or to another position while the transmit or receive acceptance filtering run is performed on the list, then message object n may not be taken into account during this acceptance filtering run. For the frame reception message object n may not receive the message because n is not taken into account for receive acceptance filtering. The message is then received by the second priority message object (in case of any other acceptance filtering match) or is lost when there is no other message object configured for this identifier. For the frame transmission message object n may not be selected for transmission, whereas the second highest priority message object is selected instead (if any). If there is no other message object in the list with valid transmit request, then no transmission is scheduled in this filtering round. If in addition the CAN bus is idle, then no further transmit acceptance filtering is issued unless another CAN node starts a transfer or one of the bits MSGVAL, TXRQ, TXENO, TXEN1 is set in the message object control register of any message object.

#### Workaround

After reallocating message object m, write the value one to one of the bits MSGVAL, TXRQ, TXENO, TXEN1 of the message object control register of any message object in order to retrigger transmit acceptance filtering.

For frame reception, make sure that there is another message object in the

list that can receive the message targeted to n in order to avoid data loss

(e.g. a message object with an acceptance mask=0<sub>D</sub> and PRI=3<sub>D</sub> as last

object of the list).

## MultiCAN Al.044 RxFIFO Base SDT

If a receive FIFO base object is located in that part of the list, that is used for the FIFO storage container (defined by the top and bottom pointer of this base object) and bit SDT is set in the base object (CUR pointer points to the base object), then MSGVAL of the base object is cleared after storage of a received frame in the base object without taking the setting of MOFGPRn.SEL into account.

#### Workaround

Take the FIFO base object out of the list segment of the FIFO slave objects, when using Single Data Transfer.

# MultiCAN Al.045 OVIE Unexpected Interrupt

When a gateway source object or a receive FIFO base object with MOFCRn.OVIE set transmits a CAN frame, then after the transmission an unexpected interrupt is generated on the interrupt line as given by MOIPRm.RXINP of the message object referenced by m=MOFGPRn.CUR.

#### Workaround

Do not transmit any CAN message by receive FIFO base objects or gateway source objects with bit MOFCRn.OVIE set.

# MultiCAN\_Al.046 Transmit FIFO base Object position

If a message object n is configured as transmit FIFO base object and is located in the list segment that is used for the FIFO storage container (defined by

MOFGPRn.BOT and MOFGPRn.TOP) but not at the list position given by MOFGPRn.BOT, then the MultiCAN uses incorrect pointer values for this transmit FIFO.

### Workaround

The transmit FIFO works properly when the transmit FIFO base object is either at the bottom position within the list segment of the FIFO (MOFGPRn.BOT=n) or outside of the list segment as described above.

#### MultiCAN TC.025 RXUPD behavior

When a CAN frame is stored in a message object, either directly from the CAN node or indirectly via receive FIFO or from a gateway source object, then bit MOCTR.RXUPD is set in the message object before the storage process and is automatically cleared after the storage process.

## **Problem description**

When a standard message object (MOFCR.MMC) receives a CAN frame from a CAN node, then it processes its own RXUPD as described above (correct).

In addition to that, it also sets and clears bit RXUPD in the message object referenced by pointer MOFGPR.CUR (wrong behavior).

#### Workaround

The "foreign" RXUPD pulse can be avoided by initializing MOFGPR. CUR with the message number of the object itself instead of another object (which would be message object 0 by default, because MOFGPR. CUR points to message object 0 after reset initialization of MultiCAN).

# MultiCAN\_TC.026 MultiCAN Timestamp Function

The timestamp functionality does not work correctly.

#### Workaround

Do not use timestamp.

### MultiCAN TC.027 MultiCAN Tx Filter Data Remote

Message objects of priority class 2 (MOAR.PRI = 2) are transmitted in the order as given by the CAN arbitration rules. This implies that for 2 message objects which have the same CAN identifier, but different DIR bit, the one with DIR = 1 (send data frame) shall be transmitted before the message object with DIR = 0, which sends a remote frame. The transmit filtering logic of the MultiCAN leads to a reverse order, i.e the remote frame is transmitted first. Message objects with different identifiers are handled correctly.

#### Workaround

None.

## MultiCAN TC.028 SDT behavior

#### Correct behavior

Standard message objects:

MultiCAN clears bit MOCTR.MSGVAL after the successful reception/transmission of a CAN frame if bit MOFCR.SDT is set.

Transmit Fifo slave object:

MultiCAN clears bit MOCTR.MSGVAL after the successful reception/transmission of a CAN frame if bit MOFCR.SDT is set. After a transmission, MultiCAN also looks at the respective transmit FIFO base object and clears bit MSGVAL in the base object if bit SDT is set in the base object and pointer MOFGPR.CUR points to MOFGPR.SEL (after the pointer update).

Gateway Destination/Fifo slave object:

MultiCAN clears bit MOCTR.MSGVAL after the storage of a CAN frame into the object (gateway/FIFO action) or after the successful transmission of a CAN frame if bit MOFCR.SDT is set. After a reception, MultiCAN also looks at the respective FIFO base/Gateway source object and clears bit MSGVAL in the base

object if bit SDT is set in the base object and pointer MOFGPR.CUR points to MOFGPR.SEL (after the pointer update).

## **Problem description**

Standard message objects:

After the successful transmission/reception of a CAN frame, MultiCAN also looks at message object given by MOFGPR.CUR. If bit SDT is set in the referenced message object, then bit MSGVAL is cleared in the message object CUR is pointing to.

Transmit FIFO slave object:

Same wrong behaviour as for standard message object. As for transmit FIFO slave objects CUR always points to the base object, the whole transmit FIFO is set invalid after the transmission of the first element instead after the base object CUR pointer has reached the predefined SEL limit value.

Gateway Destination/Fifo slave object:

Correct operation of the SDT feature.

#### Workaround

Standard message object:

Set pointer MOFGPR. CUR to the message number of the object itself.

Transmit FIFO:

Do not set bit MOFCR. SDT in the transmit FIFO base object. Then SDT works correctly with the slaves, but the FIFO deactivation feature by CUR reaching a predefined limit SEL is lost.

# MultiCAN\_TC.029 Tx FIFO overflow interrupt not generated

# Specified behaviour

After the successful transmission of a Tx FIFO element, a Tx overflow interrupt is generated if the FIFO base object fulfils these conditions:

- Bit MOFCR.OVIE=1, AND

- MOFGPR.CUR becomes equal to MOFGPR.SEL

#### Real behaviour

A Tx FIFO overflow interrupt will not be generated after the transmission of the Tx FIFO base object.

#### Workaround

If Tx FIFO overflow interrupt needed, take the FIFO base object out of the circular list of the Tx message objects. That is to say, just use the FIFO base object for FIFO control, but not to store a Tx message.

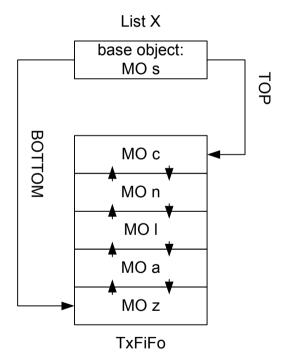

Figure 1 FIFO structure

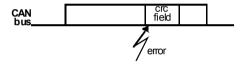

# <u>MultiCAN\_TC.030</u> Wrong transmit order when CAN error at start of CRC transmission

The priority order defined by acceptance filtering, specified in the message objects, define the sequential order in which these messages are sent on the CAN bus. If an error occurs on the CAN bus, the transmissions are delayed due to the destruction of the message on the bus, but the transmission order is kept. However, if a CAN error occurs when starting to transmit the CRC field, the arbitration order for the corresponding CAN node is disturbed, because the faulty message is not retransmitted directly, but after the next transmission of the CAN node.

Figure 2

#### Workaround

None.

# MultiCAN\_TC.031 List Object Error wrongly triggered

If the first list object in a list belonging to an active CAN node is deallocated from that list position during transmit/receive acceptance filtering (happening during message transfer on the bus), then a "list object" error may occur ( $NSRx.LOE=1_B$ ), which will cause that effectively no acceptance filtering is performed for this message by the affected CAN node.

#### As a result:

for the affected CAN node, the CAN message during which the error occurs will not be stored in a message object. This means that although the message is acknowledged on the CAN bus, its content will be ignored.

- the message handling of an ongoing transmission is not disturbed, but the transmission of the subsequent message will be delayed, because transmit acceptance filtering has to be started again.

- message objects with pending transmit request might not be transmitted at all due to failed transmit acceptance filtering.

#### Workaround

#### EITHER:

- Avoid deallocation of the first element on active CAN nodes. Dynamic reallocations on message objects behind the first element are allowed, OR

- Avoid list operations on a running node. Only perform list operations, if CAN node is not in use (e.g. when NCRx.INIT=1<sub>B</sub>)

## MultiCAN TC.032 MSGVAL wrongly cleared in SDT mode

When Single Data Transfer Mode is enabled (MOFCRn.SDT= $\mathbf{1}_B$ ), the bit MOCTRn.MSGVAL is cleared after the reception of a CAN frame, no matter if it is a data frame or a remote frame.

In case of a remote frame reception and with MOFCR.FRREN =  $0_B$ , the answer to the remote frame (data frame) is transmitted despite clearing of MOCTRN.MSGVAL (incorrect behaviour). If, however, the answer (data frame) does not win transmit acceptance filtering or fails on the CAN bus, then no further transmission attempt is made due to cleared MSGVAL (correct behaviour).

#### Workaround

To avoid a single trial of a remote answer in this case, set MOFCR.FRREN =

1<sub>B</sub> and MOFGPR.CUR = this object.

# MultiCAN TC.035 Different bit timing modes

Bit timing modes (NFCRx.CFMOD= $10_B$ ) do not conform to the specification.

When the modes  $001_B$ - $100_B$  are set in register NFCRx.CFSEL, the actual configured mode and behaviour is different than expected.

Table 7

| Table I                      | +                                             |                                                                                                                                                                                                        |

|------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit timing mode (NFCR.CFSEL) | Value to be written to NFCR.CFSEL             | Measurement                                                                                                                                                                                            |

| according to                 | instead                                       |                                                                                                                                                                                                        |

| •                            | iiisteau                                      |                                                                                                                                                                                                        |

| spec                         |                                               |                                                                                                                                                                                                        |

| 001 <sub>B</sub>             | Mode is missing (not implemented) in MultiCAN | Whenever a recessive edge (transition from 0 to 1) is monitored on the receive input the time (measured in clock cycles) between this edge and the most recent dominant edge is stored in CFC.         |

| 010 <sub>B</sub>             | 011 <sub>B</sub>                              | Whenever a dominant edge is received as a result of a transmitted dominant edge the time (clock cycles) between both edges is stored in CFC.                                                           |

| 011 <sub>B</sub>             | 100 <sub>B</sub>                              | Whenever a recessive edge is received as a result of a transmitted recessive edge the time (clock cycles) between both edges is stored in CFC.                                                         |

| 100 <sub>B</sub>             | 001 <sub>B</sub>                              | Whenever a dominant edge that qualifies for synchronization is monitored on the receive input the time (measured in clock cycles) between this edge and the most recent sample point is stored in CFC. |

## Workaround

None.

## MultiCAN TC.037 Clear MSGVAL

#### Correct behaviour:

When MSGVAL is cleared for a message object in any list, then this should not affect the other message objects in any way.

Message reception (wrong behaviour):

Assume that a received CAN message is about to be stored in a message object A, which can be a standard message object, FIFO base, FIFO slave, gateway source or gateway destination object.

If during of the storage action the user clears <code>MOCTR.MSGVAL</code> of message object B in any list, then the MultiCAN module may wrongly interpret this temporarily also as a clearing of <code>MSGVAL</code> of message object A. The result of this is that the message is not stored in message object A and is lost. Also no status update is performed on message object A (setting of <code>NEWDAT</code>, <code>MSGLST</code>, <code>RXPND</code>) and no message object receive interrupt is generated. Clearing of <code>MOCTR.MSGVAL</code> of message object B is performed correctly.

Message transmission (wrong behaviour):

Assume that MultiCAN is about to copy the message content of a message object A into the internal transmit buffer of the CAN node for transmission.

If during of the copy action the user clears <code>MOCTR.MSGVAL</code> of message object B in any list, then the MultiCAN module may wrongly interpret this also as a clearing of <code>MSGVAL</code> of message object A. The result of this is that the copy action for message A is not performed, bit <code>NEWDAT</code> is not cleared and no transmission takes place (clearing <code>MOCTR.MSGVAL</code> of message object B is performed correctly). In case of idle CAN bus and the user does not actively set the transmit request of any message object, this may lead to not transmitting any further message object, even if they have a valid transmit request set.

# Single data transfer feature:

When the MultiCAN module clears MSGVAL as a result of a single data transfer (MOFCR.SDT = 1 in the message object), then the problem does not occur. The problem only occurs if MSGVAL of a message object is cleared via CPU.

#### Workaround

Do not clear MOCTR.MSGVAL of any message object during CAN operation. Use bits MOCTR.RXEN, MOCTR.TXEN0 instead to disable/reenable reception and transmission of message objects.

### MultiCAN TC.038 Cancel TXRQ

When the transmit request of a message object that has won transmit acceptance filtering is cancelled (by clearing MSGVAL, TXRQ, TXENO or TXEN1), the CAN bus is idle and no writes to MOCTR of any message object are performed, then MultiCAN does not start the transmission even if there are message objects with valid transmit request pending.

#### Workaround

To avoid that the CAN node ignores the transmission:

take a dummy message object, that is not allocated to any CAN node.

Whenever a transmit request is cleared, set TXRQ of the dummy message object thereafter. This retriggers the transmit acceptance filtering process.

or:

whenever a transmit request is cleared, set one of the bits TXRQ, TXENO or TXEN1, which is already set, again in the message object for which the transmit request is cleared or in any other message object. This retriggers the transmit acceptance filtering process.

# <u>SYS\_XC8.001</u> MOV (direct, direct) instruction might cause a wrong value to be written to the destination register

The MOV (direct, direct) instruction (hex code  $85_H$ ) that access registers (direct address ranging from  $80_H$  to  $FF_H$ ), does not write the correct value of the source register to the destination register if the destination register is a register listed in the table below.

The source register can be any register from the direct address range  $80_{\rm H}$  to  ${\rm FF}_{\rm H}$ .

Table 8

| Module | Register                    | SFR             | RMA | Page | Products     |

|--------|-----------------------------|-----------------|-----|------|--------------|

|        |                             | Address         | Р   |      | Affected     |

| SCU    | IRCON0                      | B4 <sub>H</sub> | 0   | 0    | XC88x, XC878 |

|        | IRCON1                      | B5 <sub>H</sub> | 0   | 0    | XC88x, XC878 |

|        | IRCON2                      | B6 <sub>H</sub> | 0   | 0    | XC88x, XC878 |

|        | IRCON3                      | B4 <sub>H</sub> | 0   | 3    | All          |

|        | IRCON4                      | B5 <sub>H</sub> | 0   | 3    | All          |

|        | NMISR                       | BC <sub>H</sub> | 0   | 0    | XC88x, XC878 |

|        | FDCON                       | E9 <sub>H</sub> | 0   | 0    | XC88x, XC878 |

|        | PMCON0                      | B4 <sub>H</sub> | 0   | 1    | XC88x, XC878 |

|        | OSC_CON                     | B6 <sub>H</sub> | 0   | 1    | XC88x, XC878 |

|        | PLL_CON                     | B7 <sub>H</sub> | 0   | 1    | XC88x        |

|        | MISC_CON                    | E9 <sub>H</sub> | 0   | 1    | XC88x, XC878 |

| WDT    | WDTCON                      | BB <sub>H</sub> | 1   | -    | XC88x, XC878 |

| CORDIC | CD_STATC                    | A0 <sub>H</sub> | 1   | -    | XC88x, XC878 |

| MDU    | MDUSTAT                     | B0 <sub>H</sub> | 1   | -    | XC88x, XC878 |

| SSC    | CONH<br>(Operating<br>Mode) | AB <sub>H</sub> | 0   | -    | All          |

| UART1  | SCON                        | C8 <sub>H</sub> | 1   | -    | XC88x, XC878 |

|        | FDCON                       | CC <sub>H</sub> | 1   | -    | XC88x, XC878 |

| T2     | T2CON                       | C0 <sub>H</sub> | 0   | -    | All          |

| T21    | T2CON                       | C0 <sub>H</sub> | 1   | -    | XC88x, XC878 |

| OCDS   | MMCR2                       | E9 <sub>H</sub> | 1   | -    | All          |

|        | MMCR                        | F1 <sub>H</sub> | 1   | -    | All          |

|        | MMSR                        | F2 <sub>H</sub> | 1   | -    | All          |

|        | MMICR                       | F4 <sub>H</sub> | 1   | -    | All          |

Table 8

| Module | Register | SFR             | RMA | Page | Products |

|--------|----------|-----------------|-----|------|----------|

|        |          | Address         | Р   |      | Affected |

| T2CCU  | CCTCON   | C6 <sub>H</sub> | 0   | 1    | XC878    |

|        | COSHDW   | C0 <sub>H</sub> | 0   | 2    | XC878    |

|        | COCON    | C0 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC0L     | C1 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC0H     | C2 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC1L     | C3 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC1H     | C4 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC2L     | C5 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC2H     | C6 <sub>H</sub> | 0   | 2    | XC878    |

|        | CC3L     | C1 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC3H     | C2 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC4L     | C3 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC4H     | C4 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC5L     | C5 <sub>H</sub> | 0   | 3    | XC878    |

|        | CC5H     | C6 <sub>H</sub> | 0   | 3    | XC878    |

| CCU6   | CC63SRL  | 9A <sub>H</sub> | 0   | 0    | All      |

|        | CC63SRH  | 9B <sub>H</sub> | 0   | 0    | All      |

|        | MCMOUTSL | 9E <sub>H</sub> | 0   | 0    | All      |

|        | MCMOUTSH | 9F <sub>H</sub> | 0   | 0    | All      |

|        | CC60SRL  | FA <sub>H</sub> | 0   | 0    | All      |

|        | CC60SRH  | FB <sub>H</sub> | 0   | 0    | All      |

|        | CC61SRL  | FC <sub>H</sub> | 0   | 0    | All      |

| Module   | Register | SFR             | RMA | Page | Products |

|----------|----------|-----------------|-----|------|----------|

|          | 3.2.2.   | Address         | P   | 30   | Affected |

| CCU6     | CC61SRH  | FD <sub>H</sub> | 0   | 0    | All      |

| (cont'd) | CC62SRL  | FE <sub>H</sub> | 0   | 0    | All      |

|          | CC62SRH  | FF <sub>H</sub> | 0   | 0    | All      |

|          | T12PRL   | 9C <sub>H</sub> | 0   | 1    | All      |

|          | T12PRH   | 9D <sub>H</sub> | 0   | 1    | All      |

|          | T13PRL   | 9E <sub>H</sub> | 0   | 1    | All      |

|          | T13PRH   | 9F <sub>H</sub> | 0   | 1    | All      |

|          | T12DTCL  | A4 <sub>H</sub> | 0   | 1    | All      |

|          | T12DTCH  | A5 <sub>H</sub> | 0   | 1    | All      |

|          | TCTR0L   | A6 <sub>H</sub> | 0   | 1    | All      |

|          | TCTR0H   | A7 <sub>H</sub> | 0   | 1    | All      |

|          | T12MSELL | 9A <sub>H</sub> | 0   | 2    | All      |

|          | T12MSELH | 9B <sub>H</sub> | 0   | 2    | All      |

|          | IENL     | 9C <sub>H</sub> | 0   | 2    | All      |

|          | IENH     | 9D <sub>H</sub> | 0   | 2    | All      |

|          | INPL     | 9E <sub>H</sub> | 0   | 2    | All      |

|          | INPH     | 9F <sub>H</sub> | 0   | 2    | All      |

|          | PSLR     | A6 <sub>H</sub> | 0   | 2    | All      |

|          | MCMCTR   | A7 <sub>H</sub> | 0   | 2    | All      |

|          | TCTR2L   | FA <sub>H</sub> | 0   | 2    | All      |

|          | TCTR2H   | FB <sub>H</sub> | 0   | 2    | All      |

|          | MODCTRL  | FC <sub>H</sub> | 0   | 2    | All      |

|          | MODCTRH  | FD <sub>H</sub> | 0   | 2    | All      |

|          | TRPCTRL  | FE <sub>H</sub> | 0   | 2    | All      |

|          | TRPCTRH  | FF <sub>H</sub> | 0   | 2    | All      |

|          | PISEL0L  | 9E <sub>H</sub> | 0   | 3    | All      |

|          | PISEL0H  | 9F <sub>H</sub> | 0   | 3    | All      |

|          | PISEL2   | A4 <sub>H</sub> | 0   | 3    | All      |

Table 8

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Module   | Register | SFR             | RMA | Page | Products |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-----------------|-----|------|----------|

| T13H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |          | Address         | Р   |      | Affected |

| CMPSTATH FF <sub>H</sub> 0 3 All  ADC GLOBCTR CA <sub>H</sub> 0 0 0 All  PRAR CC <sub>H</sub> 0 0 0 All  LCBR CD <sub>H</sub> 0 0 0 All  INPCR0 CE <sub>H</sub> 0 0 All  ETRCR CF <sub>H</sub> 0 0 All  CHCTR0 CA <sub>H</sub> 0 1 All  CHCTR1 CB <sub>H</sub> 0 1 All  CHCTR3 CD <sub>H</sub> 0 1 All  CHCTR4 CE <sub>H</sub> 0 1 All  CHCTR5 CF <sub>H</sub> 0 1 All  CHCTR6 D2 <sub>H</sub> 0 1 All  CHCTR7 D3 <sub>H</sub> 0 1 All  RCR0 CA <sub>H</sub> 0 1 All  RCR1 CB <sub>H</sub> 0 4 All  RCR2 CC <sub>H</sub> 0 4 All  CHINPR CD <sub>H</sub> 0 5 All  CRCR1 CA <sub>H</sub> 0 5 All  CRCR1 CA <sub>H</sub> 0 6 All  CRCR1 CB <sub>H</sub> 0 6 All  CRCR1 CB <sub>H</sub> 0 6 All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CCU6     | T13L     | FC <sub>H</sub> | 0   | 3    | All      |

| ADC  GLOBCTR  CAH  PRAR  CCH  DO  AII  PRAR  CCH  INPCRO  CEH  CHCTRO  CHCTR3  CHCTR4  CHCTR5  CHCTR6  CHCTR7  CHCTR7 | (cont'd) | T13H     | FD <sub>H</sub> | 0   | 3    | All      |

| PRAR         CC <sub>H</sub> 0         0         All           LCBR         CD <sub>H</sub> 0         0         All           INPCR0         CE <sub>H</sub> 0         0         All           ETRCR         CF <sub>H</sub> 0         0         All           CHCTR0         CA <sub>H</sub> 0         1         All           CHCTR1         CB <sub>H</sub> 0         1         All           CHCTR2         CC <sub>H</sub> 0         1         All           CHCTR3         CD <sub>H</sub> 0         1         All           CHCTR4         CE <sub>H</sub> 0         1         All           CHCTR5         CF <sub>H</sub> 0         1         All           CHCTR6         D2 <sub>H</sub> 0         1         All           CHCTR7         D3 <sub>H</sub> 0         1         All           RCR0         CA <sub>H</sub> 0         4         All           RCR1         CB <sub>H</sub> 0         4         All           RCR2         CC <sub>H</sub> 0         4         All           CHINPR         CD <sub>H</sub> 0         5         All           CHINPR         CD <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | CMPSTATH | FF <sub>H</sub> | 0   | 3    | All      |

| LCBR         CD <sub>H</sub> 0         0         All           INPCR0         CE <sub>H</sub> 0         0         All           ETRCR         CF <sub>H</sub> 0         0         All           CHCTR0         CA <sub>H</sub> 0         1         All           CHCTR1         CB <sub>H</sub> 0         1         All           CHCTR2         CC <sub>H</sub> 0         1         All           CHCTR3         CD <sub>H</sub> 0         1         All           CHCTR4         CE <sub>H</sub> 0         1         All           CHCTR5         CF <sub>H</sub> 0         1         All           CHCTR6         D2 <sub>H</sub> 0         1         All           CHCTR7         D3 <sub>H</sub> 0         1         All           RCR0         CA <sub>H</sub> 0         4         All           RCR1         CB <sub>H</sub> 0         4         All           RCR2         CC <sub>H</sub> 0         4         All           RCR3         CD <sub>H</sub> 0         5         All           EVINPR         D3 <sub>H</sub> 0         5         All           CRCR1         CA <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ADC      | GLOBCTR  | CA <sub>H</sub> | 0   | 0    | All      |

| INPCR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | PRAR     | CC <sub>H</sub> | 0   | 0    | All      |

| ETRCR         CF <sub>H</sub> 0         0         All           CHCTR0         CA <sub>H</sub> 0         1         All           CHCTR1         CB <sub>H</sub> 0         1         All           CHCTR2         CC <sub>H</sub> 0         1         All           CHCTR3         CD <sub>H</sub> 0         1         All           CHCTR4         CE <sub>H</sub> 0         1         All           CHCTR5         CF <sub>H</sub> 0         1         All           CHCTR6         D2 <sub>H</sub> 0         1         All           CHCTR6         D2 <sub>H</sub> 0         1         All           CHCTR7         D3 <sub>H</sub> 0         1         All           RCR0         CA <sub>H</sub> 0         4         All           RCR1         CB <sub>H</sub> 0         4         All           RCR2         CC <sub>H</sub> 0         4         All           RCR3         CD <sub>H</sub> 0         5         All           EVINPR         D3 <sub>H</sub> 0         5         All           CRCR1         CA <sub>H</sub> 0         6         All           CRMR1         CB <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | LCBR     | CD <sub>H</sub> | 0   | 0    | All      |

| CHCTR0         CA <sub>H</sub> 0         1         AII           CHCTR1         CB <sub>H</sub> 0         1         AII           CHCTR2         CC <sub>H</sub> 0         1         AII           CHCTR3         CD <sub>H</sub> 0         1         AII           CHCTR4         CE <sub>H</sub> 0         1         AII           CHCTR5         CF <sub>H</sub> 0         1         AII           CHCTR6         D2 <sub>H</sub> 0         1         AII           CHCTR7         D3 <sub>H</sub> 0         1         AII           RCR0         CA <sub>H</sub> 0         4         AII           RCR1         CB <sub>H</sub> 0         4         AII           RCR2         CC <sub>H</sub> 0         4         AII           RCR3         CD <sub>H</sub> 0         4         AII           CHINPR         CD <sub>H</sub> 0         5         AII           EVINPR         D3 <sub>H</sub> 0         5         AII           CRCR1         CA <sub>H</sub> 0         6         AII           CRPR1         CB <sub>H</sub> 0         6         AII           CRMR1         CC <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | INPCR0   | CE <sub>H</sub> | 0   | 0    | All      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | ETRCR    | CF <sub>H</sub> | 0   | 0    | All      |

| CHCTR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | CHCTR0   | CA <sub>H</sub> | 0   | 1    | All      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | CHCTR1   | CB <sub>H</sub> | 0   | 1    | All      |

| CHCTR4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | CHCTR2   | CC <sub>H</sub> | 0   | 1    | All      |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | CHCTR3   | CD <sub>H</sub> | 0   | 1    | All      |

| CHCTR6 D2 <sub>H</sub> 0 1 All CHCTR7 D3 <sub>H</sub> 0 1 All RCR0 CA <sub>H</sub> 0 4 All RCR1 CB <sub>H</sub> 0 4 All RCR2 CC <sub>H</sub> 0 4 All RCR3 CD <sub>H</sub> 0 4 All CHINPR CD <sub>H</sub> 0 5 All EVINPR D3 <sub>H</sub> 0 5 All CRCR1 CA <sub>H</sub> 0 6 All CRPR1 CB <sub>H</sub> 0 6 All CRMR1 CC <sub>H</sub> 0 6 All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | CHCTR4   | CE <sub>H</sub> | 0   | 1    | All      |

| CHCTR7 D3 <sub>H</sub> 0 1 AII  RCR0 CA <sub>H</sub> 0 4 AII  RCR1 CB <sub>H</sub> 0 4 AII  RCR2 CC <sub>H</sub> 0 4 AII  RCR3 CD <sub>H</sub> 0 4 AII  CHINPR CD <sub>H</sub> 0 5 AII  EVINPR D3 <sub>H</sub> 0 5 AII  CRCR1 CA <sub>H</sub> 0 6 AII  CRMR1 CC <sub>H</sub> 0 6 AII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | CHCTR5   | CF <sub>H</sub> | 0   | 1    | All      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | CHCTR6   | D2 <sub>H</sub> | 0   | 1    | All      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | CHCTR7   | D3 <sub>H</sub> | 0   | 1    | All      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          | RCR0     | CA <sub>H</sub> | 0   | 4    | All      |