16/32-Bit

**Architecture**

## XC2300C Derivatives

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / High Line

Errata Sheet V1.6 2013-03

## Microcontrollers

Edition 2013-03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2013 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

16/32-Bit

**Architecture**

## XC2300C Derivatives

16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC2000 Family / High Line

Errata Sheet V1.6 2013-03

Microcontrollers

### **Table of Contents**

| 1                                    | History List / Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                                          |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 2                                    | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8                                                                                                                          |

| 3                                    | Current Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                         |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4 | Errata Device Overview Functional Deviations Deviations from Electrical and Timing Specification Application Hints Documentation Updates                                                                                                                                                                                                                                                                                                                                                                       | 11<br>14<br>15                                                                                                             |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4 | Short Errata Description         Functional Deviations         Deviations from Electrical and Timing Specification         Application Hints         Documentation Updates                                                                                                                                                                                                                                                                                                                                     | 18<br>21<br>22                                                                                                             |

| <b>6</b><br>6.1                      | Detailed Errata Description Functional Deviations  BROM_TC.006  BSL_CAN_X.001  ECC_X.002  ESR_X.002  ESR_X.004  FlexRay_Al.087  FlexRay_Al.088  FlexRay_Al.090  FlexRay_Al.090  FlexRay_Al.091  FlexRay_Al.092  FlexRay_Al.093  FlexRay_Al.094  FlexRay_Al.095  FlexRay_Al.096  FlexRay_Al.098  FlexRay_Al.098  FlexRay_Al.098  FlexRay_Al.099  FlexRay_Al.099  FlexRay_Al.099  FlexRay_Al.099  FlexRay_Al.100  FlexRay_Al.100  FlexRay_Al.101  FlexRay_Al.102  FlexRay_Al.103  FlexRay_Al.103  FlexRay_Al.103 | 25<br>25<br>25<br>27<br>27<br>28<br>29<br>30<br>31<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33<br>33 |

Errata Sheet 4 V1.6, 2013-03

|     | GPT12E_X.002                                         | 40 |

|-----|------------------------------------------------------|----|

|     | OCDS_X.003                                           | 42 |

|     | PAD_X.001                                            | 42 |

|     | PARITY_X.001                                         | 47 |

|     | RESET_X.003                                          | 47 |

|     | RESET_X.004                                          | 47 |

|     | SCU_X.012                                            | 48 |

|     | StartUp_X.003                                        | 48 |

|     | USIC_AI.004                                          | 50 |

|     | USIC_AI.005                                          | 50 |

|     | USIC_AI.016                                          | 50 |

|     | WDT_X.002                                            | 51 |

| 6.2 | Deviations from Electrical- and Timing Specification | 53 |

|     | FLASH_X.P001                                         | 53 |

|     | SWD_X.P001                                           | 53 |

|     | SWD_X.P002                                           | 54 |

| 6.3 | Application Hints                                    | 55 |

|     | ADC_AI.H002                                          | 55 |

|     | CAPCOM12_X.H001                                      | 55 |

|     | CC6_X.H001                                           | 57 |

|     | ECC_X.H001                                           | 57 |

|     | FlexRay_AI.H004                                      | 57 |

|     | FlexRay_AI.H005                                      | 58 |

|     | FlexRay_AI.H006                                      | 58 |

|     | FlexRay_AI.H007                                      | 58 |

|     | FlexRay_AI.H009                                      | 59 |

|     | GPT12_AI.H001                                        | 59 |

|     | GPT12E_X.H002                                        | 60 |

|     | INT_X.H002                                           | 61 |

|     | INT_X.H004                                           | 61 |

|     | MultiCAN_AI.H005                                     | 62 |

|     | MultiCAN_AI.H006                                     | 62 |

|     | MultiCAN_AI.H007                                     | 62 |

|     | MultiCAN_AI.H008                                     | 63 |

|     | MultiCAN_TC.H002                                     | 63 |

|     | MultiCAN_TC.H003                                     | 64 |

|     | MultiCAN_TC.H004                                     | 64 |

|     | OCDS_X.H003                                          | 65 |

|     | PVC_X.H001                                           | 65 |

|     | RESET_X.H003                                         | 67 |

|     | RTC_X.H003                                           | 67 |

|     | SCU_X.H009                                           | 67 |

|     | SWD_X H001                                           | 68 |

Errata Sheet 5 V1.6, 2013-03

|     | USIC_AI.H001          | 86         |

|-----|-----------------------|------------|

|     | USIC_AI.H002          | 86         |

|     | USIC_AI.H003          | 39         |

| 6.4 | Documentation Updates | 70         |

|     | EBC_X.D001            |            |

|     | ECC_X.D002            | <b>7</b> 0 |

|     | RESET_X.D001          | 1          |

Errata Sheet 6 V1.6, 2013-03

**History List / Change Summary**

## 1 History List / Change Summary

Table 1 History List

| Version | Date       | Remark <sup>1)</sup>                                                   |

|---------|------------|------------------------------------------------------------------------|

| 1.0     | 30.09.2008 | new Errata Sheet                                                       |

| 1.1     | 30.01.2009 |                                                                        |

| 1.2     | 13.03.2009 | new Marking/Step ES-AA added to Errata Sheet, new Errata Sheet layout  |

| 1.3     | 01.03.2010 | Errata No. 01715AERRA, new Marking/Step (ES+AA) added to Errata Sheet. |

| 1.4     | 29.06.2010 | Errata No. 01810AERRA, new Marking/Step (ES-AB) added to Errata Sheet. |

| 1.5     | 23.09.2010 | Errata No. 01878AERRA, new Marking/Step (AB) added to Errata Sheet.    |

| 1.6     | 22.03.2013 | Errata No. 02533AERRA.                                                 |

Errata changes to the previous Errata Sheet are marked in Chapter 5 "Short Errata Description".

#### **Trademarks**

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

General

### 2 General

This Errata Sheet describes the deviations of the XC2300C Derivatives from the current user documentation

Each erratum identifier follows the pattern Module Arch.TypeNumber:

- Module: subsystem, peripheral, or function affected by the erratum

- Arch: microcontroller architecture where the erratum was firstly detected.

- AI: Architecture Independent

- CIC: Companion ICs

- TC: TriCore

- X: XC166 / XE166 / XC2000 Family

- XC8: XC800 Family[none]: C166 Family

- Type: category of deviation

- [none]: Functional Deviation

- P: Parametric Deviation

- H: Application Hint

- D: Documentation Update

- Number: ascending sequential number within the three previous fields. As

this sequence is used over several derivatives, including already solved

deviations, gaps inside this enumeration can occur.

This Errata Sheet applies to all temperature and frequency versions and to all memory size variants of this device, unless explicitly noted otherwise.

Note: This device is equipped with a C166S V2 Core. Some of the errata have workarounds which are possibly supported by the tool vendors.

Some corresponding compiler switches need possibly to be set. Please see the respective documentation of your compiler.

For effects of issues related to the on-chip debug system, see also the documentation of the debug tool vendor.

### General

Some errata of this Errata Sheet do not refer to all of the XC2300C Derivatives, please look to the overview:

Table 2 for Functional Deviations

Table 3 for Deviations from Electrical and Timing Specification

Table 4 for Application Hints

Table 5 for Documentation Updates

**Current Documentation**

### 3 Current Documentation

The Infineon XC2000 Family comprises device types from the XC2200 group, the XC2300 group and the XC2700 group. The XC23xxC device types belong to the XC2300 group.

Device XC23xxC

Marking/Step EES-AA, ES-AA, ES+AA, ES-AB, AB

Package PG-LQFP-144

This Errata Sheet refers to the following documentation:

- XC2300C Derivatives User's Manual

- XC238xC Data Sheet

- Documentation Addendum (if applicable)

Make sure you always use the corresponding documentation for this device available in category 'Documents' at <a href="https://www.infineon.com/xc2300">www.infineon.com/xc2300</a>.

The specific test conditions for EES and ES are documented in a separate Status Sheet.

Note: Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only.

**Errata Device Overview**

### 4 Errata Device Overview

This chapter gives an overview of the dependencies of individual errata to devices and steps. An  $\mathbf{X}$  in the column of the sales codes shows that this erratum is valid.

### 4.1 Functional Deviations

Table 2 shows the dependencies of functional deviations in the derivatives.

Table 2 Errata Device Overview:

| Function       | onai Dev        | viatioi                                     |

|----------------|-----------------|---------------------------------------------|

| Functional     | XC23xxC         |                                             |

| Deviation      | EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |

| BROM_TC.006    | X               | X                                           |

| BSL_CAN_X.001  | X               | X                                           |

| ECC_X.002      | X               |                                             |

| ESR_X.002      | X               | X                                           |

| ESR_X.004      | X               | X                                           |

| FlexRay_Al.087 | X               | X                                           |

| FlexRay_Al.088 | X               | X                                           |

| FlexRay_Al.089 | X               | X                                           |

| FlexRay_Al.090 | X               | X                                           |

| FlexRay_Al.091 | X               | X                                           |

| FlexRay_Al.092 | X               | X                                           |

| FlexRay_Al.093 | X               | X                                           |

| FlexRay_Al.094 | X               | X                                           |

| FlexRay_Al.095 | X               | X                                           |

### **Errata Device Overview**

Table 2 Errata Device Overview:

Functional Deviations (conf'd)

|                 |                                             | ns (cont'd) |

|-----------------|---------------------------------------------|-------------|

| XC23xxC         |                                             |             |

| EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

| X               | X                                           |             |

|                 | X X X X X X X X X X X X X X X X X X X       | X           |

<sup>1)</sup> From EES/ES-AA step to ES+AA/ES-AB/AB step, 2 errata have been fixed.

### **Errata Device Overview**

2) Valid for all AB steps encloses ES-AB and AB step.

**Errata Device Overview**

### 4.2 Deviations from Electrical and Timing Specification

**Table 3** shows the dependencies of deviations from the electrical and timing specification in the derivatives.

Table 3 Errata Device Overview:

Deviations from Electrical- and Timing Specification

| AC/DC/ADC    |                 | 7377                                        |

|--------------|-----------------|---------------------------------------------|

| Deviation    | EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |

| FLASH_X.P001 | X               | X                                           |

| SWD_X.P001   | X               |                                             |

| SWD_X.P002   | X               | X                                           |

<sup>1)</sup> From EES/ES-AA step to ES+AA/ES-AB/AB step, 2 errata have been fixed.

<sup>2)</sup> Valid for all AB steps encloses ES-AB and AB step.

**Errata Device Overview**

### 4.3 Application Hints

**Table 4** shows the dependencies of application hints in the derivatives.

Table 4 Errata Device Overview:

Application Hints

| Applicat         | ion m           | 1115                                        |  |

|------------------|-----------------|---------------------------------------------|--|

| Hint             | XC23xxC         |                                             |  |

|                  | EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |  |

| ADC_AI.H002      | X               | X                                           |  |

| CAPCOM12_X.H001  | X               | X                                           |  |

| CC6_X.H001       | X               | X                                           |  |

| ECC_X.H001       | X               | X                                           |  |

| FlexRay_Al.H004  | X               | X                                           |  |

| FlexRay_Al.H005  | X               | X                                           |  |

| FlexRay_Al.H006  | X               | X                                           |  |

| FlexRay_Al.H007  | X               | X                                           |  |

| FlexRay_Al.H009  | X               | X                                           |  |

| GPT12_AI.H001    | X               | X                                           |  |

| GPT12E_X.H002    | X               | X                                           |  |

| INT_X.H002       | X               | X                                           |  |

| INT_X.H004       | X               | X                                           |  |

| MultiCAN_AI.H005 | X               | X                                           |  |

| MultiCAN_AI.H006 | X               | X                                           |  |

| MultiCAN_AI.H007 | X               | X                                           |  |

| MultiCAN_AI.H008 | X               | X                                           |  |

| MultiCAN_TC.H002 | X               | X                                           |  |

| MultiCAN_TC.H003 | X               | X                                           |  |

|                  |                 |                                             |  |

#### **Errata Device Overview**

Table 4 Errata Device Overview:

Application Hints (cont'd)

|                 | 1113 (01                                    |

|-----------------|---------------------------------------------|

| XC23xxC         |                                             |

| EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |

| X               | X                                           |

| X               | X                                           |

| X               | X                                           |

| X               | X                                           |

| X               | X                                           |

| X               | X                                           |

| X               | X                                           |

| v               | X                                           |

| X               | ^                                           |

| X               | X                                           |

|                 | X<br>X<br>X<br>EES-AA<br>ES-AA              |

<sup>1)</sup> From EES/ES-AA step to ES+AA/ES-AB/AB step, 2 errata have been fixed.

<sup>2)</sup> Valid for all AB steps encloses ES-AB and AB step.

**Errata Device Overview**

### 4.4 Documentation Updates

**Table 5** shows the dependencies oft documentation updates in the derivatives.

Table 5 Errata Device Overview:

Documentation Updates

| Documentation | J???CJ.X        |                                             |

|---------------|-----------------|---------------------------------------------|

| Updates       | EES-AA<br>ES-AA | ES+AA <sup>1)</sup><br>all AB <sup>2)</sup> |

| EBC_X.D001    | X               | X                                           |

| ECC_X.D002    | X               | X                                           |

| RESET_X.D001  | X               | X                                           |

<sup>1)</sup> From EES/ES-AA step to ES+AA/ES-AB/AB step, 2 errata have been fixed.

<sup>2)</sup> Valid for all AB steps encloses ES-AB and AB step.

**Short Errata Description**

## 5 Short Errata Description

This chapter gives an overview on the deviations and application hints. Changes to the last Errata Sheet are shown in the column "Chg".

### 5.1 Functional Deviations

Table 6 shows a short description of the functional deviations.

Table 6 Functional Deviations

| Functional Deviation | Short Description                                                                                                                       | Chg | Pg |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| BROM_TC.006          | Baud Rate Detection for CAN Bootstrap<br>Loader                                                                                         | New | 25 |

| BSL_CAN_X.001        | Quartz Crystal Settling Time after PORST too Long for CAN Bootstrap Loader                                                              |     | 25 |

| ECC_X.002            | Incorrect ECC Error Indication for DPRAM                                                                                                |     | 26 |

| ESR_X.002            | ESREXSTAT1 and ESREXSTAT2 Status Bits can be Cleared after a Write Access                                                               |     | 27 |

| ESR_X.004            | Wrong Value of SCU_RSTCONx Registers after ESRy Application Reset                                                                       | New | 27 |

| FlexRay_Al.087       | After reception of a valid sync frame followed by a valid non-sync frame in the same static slot the received sync frame may be ignored |     | 28 |

| FlexRay_Al.088       | A sequence of received WUS may generate redundant SIR.WUPA/B events                                                                     |     | 29 |

| FlexRay_Al.089       | Rate correction set to zero in case of SyncCalcResult=MISSING_TERM                                                                      |     | 29 |

| FlexRay_Al.090       | Flag SFS.MRCS is set erroneously although at least one valid sync frame pair is received                                                |     | 30 |

### **Short Errata Description**

Table 6

Functional Deviations (cont'd)

| Functional<br>Deviation | Short Description                                                                                                                                              | Chg | Pg |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| FlexRay_Al.091          | Incorrect rate and/or offset correction value if second Secondary Time Reference Point (STRP) coincides with the action point after detection of a valid frame |     | 31 |

| FlexRay_Al.092          | Initial rate correction value of an integrating node is zero if pMicroInitialOffsetA,B = 0x00                                                                  |     | 32 |

| FlexRay_Al.093          | Acceptance of startup frames received after reception of more than gSyncNodeMax sync frames                                                                    |     | 32 |

| FlexRay_Al.094          | Sync frame overflow flag EIR.SFO may be set if slot counter is greater than 1024                                                                               |     | 33 |

| FlexRay_Al.095          | Register RCV displays wrong value                                                                                                                              |     | 34 |

| FlexRay_Al.096          | Noise following a dynamic frame that delays idle detection may fail to stop slot                                                                               |     | 35 |

| FlexRay_Al.097          | Loop back mode operates only at 10 MBit/s                                                                                                                      |     | 35 |

| FlexRay_Al.098          | Suspend Mode is not functional                                                                                                                                 |     | 36 |

| FlexRay_Al.099          | Erroneous cycle offset during startup after abort of startup or normal operation                                                                               |     | 36 |

| FlexRay_Al.100          | First WUS following received valid WUP may be ignored                                                                                                          |     | 37 |

| FlexRay_Al.101          | READY command accepted in READY state                                                                                                                          |     | 38 |

| FlexRay_Al.102          | Slot Status vPOC!SlotMode is reset immediately when entering HALT state                                                                                        |     | 38 |

| FlexRay_Al.103          | Received messages not stored in Message RAM when in Loop Back Mode                                                                                             | New | 39 |

| FlexRay_X.001           | Trigger User Reset after Power-On                                                                                                                              | New | 38 |

| GPT12E_X.002            | Effects of GPT Module Microarchitecture                                                                                                                        |     | 40 |

### **Short Errata Description**

**Table 6** Functional Deviations (cont'd)

| Functional Deviation | Short Description                                                               | Chg | Pg |

|----------------------|---------------------------------------------------------------------------------|-----|----|

| OCDS_X.003           | Peripheral Debug Mode Settings cleared by Reset                                 |     | 42 |

| PAD_X.001            | Additional Edges in the Input Signal                                            | New | 42 |

| PARITY_X.001         | PMTSR Register Initialization                                                   |     | 47 |

| RESET_X.003          | P2.[2:0] and P10.[12:0] Switch to Input                                         |     | 47 |

| RESET_X.004          | Sticky "Register Access Trap" forces device into power-save mode after reset.   | New | 47 |

| SCU_X.012            | Wake-Up Timer RUNCON Command                                                    | New | 48 |

| StartUp_X.003        | Debug Interface Configuration from Flash can Fail Upon Power-On                 | New | 48 |

| USIC_AI.004          | Receive shifter baudrate limitation                                             |     | 50 |

| USIC_AI.005          | Only 7 data bits are generated in IIC mode when TBUF is loaded in SDA hold time |     | 50 |

| USIC_AI.016          | Transmit parameters are updated during FIFO buffer bypass                       | New | 50 |

| WDT_X.002            | Clearing the Internal Flag which Stores Preceding WDT Reset Request             |     | 51 |

**Short Errata Description**

### 5.2 Deviations from Electrical and Timing Specification

**Table 7** shows a short description of the electrical and timing deviations from the specification.

Table 7 Deviations from Electrical- and Timing Specification

| AC/DC/ADC<br>Deviation | Short Description                                     | Chg | Pg |

|------------------------|-------------------------------------------------------|-----|----|

| FLASH_X.P001           | Test Condition for Flash parameter NER in Data Sheets | New | 53 |

| SWD_X.P001             | Supply Watchdog Level VSWD_min too Low                |     | 53 |

| SWD_X.P002             | Minimizing Power Consumption of an ADC Module         | New | 54 |

**Short Errata Description**

### 5.3 Application Hints

Table 8 shows a short description of the application hints.

Table 8 Application Hints

| Hint             | Short Description                                                 | Chg | Pg        |

|------------------|-------------------------------------------------------------------|-----|-----------|

| ADC_AI.H002      | Minimizing Power Consumption of an ADC Module                     |     | 55        |

| CAPCOM12_X.H001  | Enabling or Disabling Single Event Operation                      |     | 55        |

| CC6_X.H001       | Modifications of Bit MODEN in Register CCU6x_KSCFG                |     | 57        |

| ECC_X.H001       | ECC Error Indication Permanently Set                              |     | <b>57</b> |

| FlexRay_Al.H004  | Only the first message can be received in External Loop Back mode |     | 57        |

| FlexRay_Al.H005  | Initialization of internal RAMs requires one eray_bclk cycle more |     | 58        |

| FlexRay_Al.H006  | Transmission in ATM/Loopback mode                                 |     | <b>58</b> |

| FlexRay_Al.H007  | Reporting of coding errors via TEST1.CERA/B                       |     | 58        |

| FlexRay_Al.H009  | Return from test mode operation                                   |     | 59        |

| GPT12_AI.H001    | Modification of Block Prescalers BPS1 and BPS2                    | New | 59        |

| GPT12E_X.H002    | Reading of Concatenated Timers                                    |     | 60        |

| INT_X.H002       | Increased Latency for Hardware Traps                              |     | 61        |

| INT_X.H004       | SCU Interrupts Enabled After Reset                                |     | 61        |

| MultiCAN_AI.H005 | TxD Pulse upon short disable request                              |     | 62        |

| MultiCAN_AI.H006 | Time stamp influenced by resynchronization                        |     | 62        |

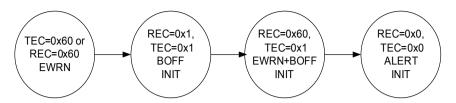

| MultiCAN_AI.H007 | Alert Interrupt Behavior in case of Bus-<br>Off                   | New | 62        |

| MultiCAN_AI.H008 | Effect of CANDIS on SUSACK                                        | New | 63        |

| MultiCAN_TC.H002 | Double Synchronization of receive input                           |     | 63        |

### **Short Errata Description**

Table 8

Application Hints (cont'd)

| Hint             | Short Description                                        | Chg        | Pg |

|------------------|----------------------------------------------------------|------------|----|

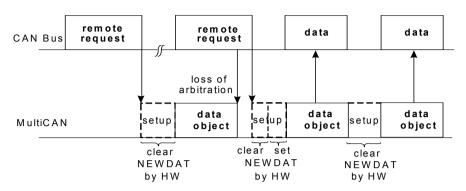

| MultiCAN_TC.H003 | Message may be discarded before transmission in STT mode |            | 64 |

| MultiCAN_TC.H004 | Double remote request                                    |            | 64 |

| OCDS_X.H003      | Debug Interface Configuration by User Software           |            | 65 |

| PVC_X.H001       | PVC Threshold Level 2                                    | Upd<br>ate | 65 |

| RESET_X.H003     | How to Trigger a PORST after an Internal Failure         |            | 67 |

| RTC_X.H003       | Changing the RTC Configuration                           |            | 67 |

| SCU_X.H009       | WUCR.TTSTAT can be set after a Power-<br>Up              |            | 67 |

| SWD_X.H001       | Application Influence on the SWD                         |            | 68 |

| USIC_AI.H001     | FIFO RAM Parity Error Handling                           |            | 68 |

| USIC_AI.H002     | Configuration of USIC Port Pins                          | New        | 68 |

| USIC_AI.H003     | PSR.RXIDLE Cleared by Software                           | New        | 69 |

**Short Errata Description**

### 5.4 Documentation Updates

Table 9 gives a short description of the documentation updates.

### Table 9 Documentation Updates

| Documentation Updates | Short Description                                              | Chg | Pg |

|-----------------------|----------------------------------------------------------------|-----|----|

| EBC_X.D001            | Visibility of Internal LXBus Cycles on<br>External Address Bus | New | 70 |

| ECC_X.D002            | Initialization of the Read-Control Logic                       |     | 70 |

| RESET_X.D001          | Reset Types of Trap Registers                                  |     | 71 |

**Detailed Errata Description**

### 6 Detailed Errata Description

This chapter provides a detailed description for each erratum. If applicable a workaround is suggested.

### 6.1 Functional Deviations

### **BROM TC.006** Baud Rate Detection for CAN Bootstrap Loader

In a specific corner case, the baud rate detected during reception of the initialization frame for the CAN bootstrap loader may be incorrect. The probability for this sporadic problem is relatively low, and it decreases with decreasing CAN baud rate and increasing module clock frequency.

#### Workaround:

If communication fails, the host should repeat the CAN bootstrap loader initialization procedure after a reset of the device.

## <u>BSL\_CAN\_X.001</u> Quartz Crystal Settling Time after PORST too Long for CAN Bootstrap Loader

The startup configuration of the CAN bootstrap loader when called immediately after PORST limits the settling time of the external oscillation to 0.5 ms. For typical quartz crystal this settling time is too short. The CAN bootstrap loader generates a time-out and goes into Startup Error State.

### Workaround

- For low performance CAN applications a ceramic resonator with settling time less than 0.5 ms can be used.

- An alternative is the Internal Start from on-chip Flash memory as startup mode after PORST. Then switch the system clock to external source and trigger a software reset with CAN bootstrap loader mode selected. Now the

Errata Sheet 25 V1.6, 2013-03

### **Detailed Errata Description**

device starts with a CAN bootstrap loader without limitation of the oscillator settling time.

### ECC X.002 Incorrect ECC Error Indication for DPRAM

Under certain conditions, the ECC error flag for the dual port memory (DPRAM) may indicate an error when none exists.

Conditions under which ECC error is incorrectly indicated:

- ECC memory protection has been selected for DPRAM (SCU MCHKCON.SELDP = 0).

- The ECC check is enabled for DPRAM (SCU ECCCON. DPEN = 1).

- A concurrent read and write access is made to the same byte or word in the DPRAM (possible due to instruction pipeline).

Under the above conditions, an ECC error may be indicated for DPRAM (flag SCU ECCSTAT.DP = 1), although there is no error in DPRAM.

It should be noted that despite the incorrect ECC error indication, the data are delivered error free, and the ECC logic still functions correctly (correcting data single bit errors, if present).

There is no data corruption in this case. The ECC bits that were written are generated correctly, as well as check and correction is not affected for that was read.

This problem is limited to the DPRAM. All other SRAM memories cannot perform concurrent read and write accesses, and therefore cannot have this issue.

### Workaround

Use parity protection for DPRAM (SCU MCHKCON.SELDP = 1).

Single-bit errors will be correctly indicated by parity logic, but will not be corrected.

**Detailed Errata Description**

## ESR\_X.002 ESREXSTAT1 and ESREXSTAT2 Status Bits can be Cleared after a Write Access

During a write access to any register, bits in registers ESREXSTAT1/2 can be cleared inadvertently.

ESREXSTAT1/2 store event(s) that can trigger various ESR functions.

### Workaround

- 1. Make sure that the trigger signals are still active when the associated service routine runs, so the trigger source can be evaluated by software.

- 2. Disable write access to registers CLRESREXSTAT1/2 by clearing bit 8 at word address 00'F008<sub>H</sub>. Use a read-modify-write sequence for this purpose to exclude other bits from this modification.

- To clear the status bits, write access to registers <code>CLRESREXSTAT1/2</code> can be enabled by setting bit 8 at word location  $00'F008_H$ . Use a read-modify-write sequence for this purpose to exclude other bits from this modification. Write access is enabled by default.

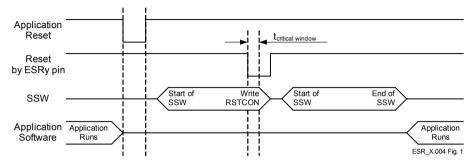

## ESR\_X.004 Wrong Value of SCU\_RSTCONx Registers after ESRy Application Reset

SCU\_RSTCONx registers are reset only by Power-On, but they may be wrongly affected after a second application reset requested by an ESRy pin. This may lead to the SCU\_RSTCONx register values being set to zero, which could unexpectedly disable reset sources within the user application. The conditions which lead to this behavior are:

- First, an application reset by SW (software), CPU (Central Processing Unit), MP (Memory), WDT (Watchdog Timer) or ESRy (External Service Request y) occurs.

- 2. Following this, an application reset on an ESRy pin occurs.

- 3. If the above mentioned ESRy reset occurs during a critical time window of the SSW (startup software), then it's possible that the application will operate with the wrong SCU\_RSTCONx register value. The critical time window occurs when the SSW is writing the SCU\_RSTCONx registers, and

#### **Detailed Errata Description**

at the same time, the ESRy reset request is processed by the reset circuitry. The width of this critical window  $f_{critical\ window}$  is less than 13 cycles.

Figure 1 Critical application reset sequence

#### Workaround

- Initialize SCU RSTCONX registers by user software after any reset, or

- assure that a second application reset request with an ESR pin does not occur during the critical time window.

# <u>FlexRay\_Al.087</u> After reception of a valid sync frame followed by a valid non-sync frame in the same static slot the received sync frame may be ignored

### Description:

If in a static slot of an even cycle a valid sync frame followed by a valid non-sync frame is received, and the frame valid detection (prt\_frame\_decoded\_on\_X) of the DEC process occurs one sclk after valid frame detection of FSP process (fsp\_val\_syncfr\_chx), the sync frame is not taken into account by the CSP process (devte\_xxs\_reg).

### Scope:

The erratum is limited to the case where more than one valid frame is received in a static slot of an even cycle.

#### **Detailed Errata Description**

### Effects:

In the described case the sync frame is not considered by the CSP process. This may lead to a SyncCalcResult of MISSIMG\_TERM (error flag SFS.MRCS set). As a result the POC state may switch to NORMAL\_PASSIVE or HALT or the Startup procedure is aborted.

#### Workaround

Avoid static slot configurations long enough to receive two valid frames.

## FlexRay\_Al.088 A sequence of received WUS may generate redundant SIR.WUPA/B events

### Description:

If a sequence of wakeup symbols (WUS) is received, all separated by appropriate idle phases, a valid wakeup pattern (WUP) should be detected after every second WUS. The E-Ray detects a valid wakeup pattern after the second WUS and then after each following WUS.

### Scope:

The erratum is limited to the case where the application program frequently resets the appropriate SIR.WUPA/B bits.

#### Effects:

In the described case there are more SIR. WUPA/B events seen than expected.

#### Workaround

Ignore redundant SIR. WUPA/B events.

## <u>FlexRay\_Al.089</u> Rate correction set to zero in case of SyncCalcResult=MISSING\_TERM

Description:

### **Detailed Errata Description**

In case a node receives too few sync frames for rate correction calculation and signals a SyncCalcResult of MISSING\_TERM, the rate correction value is set to zero instead to the last calculated value.

### Scope:

The erratum is limited to the case of receiving too few sync frames for rate correction calculation (SyncCalcResult=MISSING TERM in an odd cycle).

#### Effects:

In the described case a rate correction value of zero is applied in NORMAL\_ACTIVE / NORMAL\_PASSIVE state instead of the last rate correction value calculated in NORMAL\_ACTIVE state. This may lead to a desynchronisation of the node although it may stay in NORMAL\_ACTIVE state (depending on gMaxWithoutClockCorrectionPassive) and decreases the probability to re-enter NORMAL\_ACTIVE state if it has switched to NORMAL PASSIVE (pAllowHaltDueToclock=false).

#### Workaround

It is recommended to set gMaxWithoutClockCorrectionPassive to 1. If missing sync frames cause the node to enter NORMAL\_PASSIVE state, use higher level application software to leave this state and to initiate a re-integration into the cluster. HALT state can also be used instead of NORMAL\_PASSIVE state by setting pAllowHaltDueToClock to true.

## FlexRay\_Al.090 Flag SFS.MRCS is set erroneously although at least one valid sync frame pair is received

### Description:

If in an odd cycle 2c+1 after reception of a sync frame in slot n the total number of different sync frames per double cycle has exceeded gSyncNodeMax and the node receives in slot n+1 a sync frame that matches with a sync frame received in the even cycle 2c, the sync frame pair is not taken into account by CSP process. This may cause the flags SFS.MRCS and EIR.CCF to be set erroneously.

### **Detailed Errata Description**

### Scope:

The erratum is limited to the case of a faulty cluster configuration where different sets of sync frames are transmitted in even and odd cycles and the total number of different sync frames is greater than gSyncNodeMax.

#### Effects:

In the described case the error interrupt flag EIR.CCF is set and the node may enter either the POC state NORMAL\_PASSIVE or HALT.

#### Workaround

Correct configuration of gSyncNodeMax.

<u>FlexRay Al.091</u> Incorrect rate and/or offset correction value if second Secondary Time Reference Point (STRP) coincides with the action point after detection of a valid frame

### Description:

If a valid sync frame is received before the action point and additionally noise or a second frame leads to a STRP coinciding with the action point, an incorrect deviation value of zero is used for further calculations of rate and/or offset correction values.

### Scope:

The erratum is limited to configurations with an action point offset greater than static frame length.

#### Effects:

In the described case a deviation value of zero is used for further calculations of rate and/or offset correction values. This may lead to an incorrect rate and/or offset correction of the node.

**Detailed Errata Description**

#### Workaround

Configure action point offset smaller than static frame length.

## <u>FlexRay\_Al.092</u> Initial rate correction value of an integrating node is zero if pMicroInitialOffsetA,B = 0x00

### Description:

The initial rate correction value as calculated in figure 8-8 of protocol spec v2.1 is zero if parameter pMicroInitialOffsetA,B was configured to be zero.

### Scope:

The erratum is limited to the case where pMicroInitialOffsetA,B is configured to zero.

#### Effects:

Starting with an initial rate correction value of zero leads to an adjustment of the rate correction earliest 3 cycles later (see figure 7-10 of protocol spec v2.1). In a worst case scenario, if the whole cluster is drifting away too fast, the integrating node would not be able to follow and therefore abort integration.

#### Workaround

Avoid configurations with pMicroInitialOffsetA,B equal to zero. If the related configuration constraint of the protocol specification results in pMicroInitialOffsetA,B equal to zero, configure it to one instead. This will lead to a correct initial rate correction value, it will delay the startup of the node by only one microtick.

## <u>FlexRay\_Al.093</u> Acceptance of startup frames received after reception of more than gSyncNodeMax sync frames

Description:

### **Detailed Errata Description**

If a node receives in an even cycle a startup frame after it has received more than gSyncNodeMax sync frames, this startup frame is added erroneously by process CSP to the number of valid startup frames (zStartupNodes). The faulty number of startup frames is delivered to the process POC. As a consequence this node may integrate erroneously to the running cluster because it assumes that it has received the required number of startup frames.

### Scope:

The erratum is limited to the case of more than gSyncNodeMax sync frames.

#### Effects:

In the described case a node may erroneously integrate successfully into a running cluster.

#### Workaround

Use frame schedules where all startup frames are placed in the first static slots. gSyncNodeMax should be configured to be greater than or equal to the number of sync frames in the cluster.

## FlexRay\_Al.094 Sync frame overflow flag EIR.SFO may be set if slot counter is greater than 1024

### Description:

If in the static segment the number of transmitted and received sync frames reaches gSyncNodeMax and the slot counter in the dynamic segment reaches the value cStaticSlotIDMax + gSyncNodeMax = 1023 + gSyncNodeMax, the sync frame overflow flag EIR.SFO is set erroneously.

### Scope:

The erratum is limited to configurations where the number of transmitted and received sync frames equals to gSyncNodeMax and the number of static slots plus the number of dynamic slots is greater or equal than 1023 + gSyncNodeMax.

#### **Detailed Errata Description**

#### Effects:

In the described case the sync frame overflow flag EIR. SFO is set erroneously. This has no effect to the POC state.

#### Workaround

Configure gSyncNodeMax to number of transmitted and received sync frames plus one or avoid configurations where the total of static and dynamic slots is greater than cStaticSlotIDMax.

### FlexRay Al.095 Register RCV displays wrong value

### Description:

If the calculated rate correction value is in the range of [-pClusterDriftDamping .. +pClusterDriftDamping], vRateCorrection of the CSP process is set to zero. In this case register RCV should be updated with this value. Erroneously RCV.RCV[11:0] holds the calculated value in the range [-pClusterDriftDamping .. +pClusterDriftDamping] instead of zero.

### Scope:

The erratum is limited to the case where the calculated rate correction value is in the range of [-pClusterDriftDamping .. +pClusterDriftDamping].

#### Effects:

The displayed rate correction value RCV.RCV[11:0] is in the range of [-pClusterDriftDamping .. +pClusterDriftDamping] instead of zero. The error of the displayed value is limited to the range of [-pClusterDriftDamping .. +pClusterDriftDamping]. For rate correction in the next double cycle always the correct value of zero is used.

#### Workaround

A value of RCV.RCV[11:0] in the range of [-pClusterDriftDamping ... +pClusterDriftDamping] has to be interpreted as zero.

**Detailed Errata Description**

## FlexRay\_Al.096 Noise following a dynamic frame that delays idle detection may fail to stop slot

### Description:

If (in case of noise) the time between 'potential idle start on X' and 'CHIRP on X' (see Protocol Spec. v2.1, Figure 5-21) is greater than gdDynamicSlotIdlePhase, the E-Ray will not remain for the remainder of the current dynamic segment in the state 'wait for the end of dynamic slot rx'. Instead, the E-Ray continues slot counting. This may enable the node to further transmissions in the current dynamic segment.

### Scope:

The erratum is limited to noise that is seen only locally and that is detected in the time window between the end of a dynamic frame's DTS and idle detection ('CHIRP on X').

#### Effects:

In the described case the faulty node may not stop slot counting and may continue to transmit dynamic frames. This may lead to a frame collision in the current dynamic segment.

#### Workaround

None.

### FlexRay\_Al.097 Loop back mode operates only at 10 MBit/s

### Description:

The looped back data is falsified at the two lower baud rates of 5 and 2.5 MBit/s.

### Scope:

The erratum is limited to test cases where loop back is used with the baud rate prescaler (PRTC1.BRP[1:0]) configured to 5 or 2.5 MBit/s.

#### **Detailed Errata Description**

### Effects:

The loop back self test is only possible at the highest baud rate.

#### Workaround

Run loop back tests with 10 MBit/s (PRTC1.BRP[1:0] =  $00_B$ ).

### FlexRay Al.098 Suspend Mode is not functional

### Description:

The applied kernel mode (KSCFG.SUMCFG=2, Stop Mode 0) in suspend state will not be performed. The module proceeds its communication and the module clock is not switched off.

#### Workaround

To keep a smooth FlexRay communication ongoing, the FlexRay controller will go to halt state at the end of the communication cycle. If the FlexRay controller is in "NORMAL\_ACTIVE" or "NORMAL\_PASSIVE" state, the controller goes to POC HALT state, by setting  ${\tt SUCC1.CMD=0110_B}$ . In any other state, the command will not be accepted  $({\tt SUCC1.CMD=0000_B}$  "COMMAND NOT ACCEPTED").

### FlexRay Al.099 Erroneous cycle offset during startup after abort of startup or normal operation

### Description:

An abort of startup or normal operation by a READY command near the macotick border may lead to the effect that the state INITIALIZE\_SCHEDULE is one macrotick too short during the first following integration attempt. This leads to an early cycle start in state INTEGRATION\_COLDSTART\_CHECK or INTEGRATION CONSISTENCY CHECK.

As a result the integrating node calculates a cycle offset of one macrotick at the end of the first even/odd cycle pair in the states

### **Detailed Errata Description**

INTEGRATION\_COLDSTART\_CHECK

or

INTEGRATION\_CONSISTENCY\_CHECK and tries to correct this offset.

If the node is able to correct the offset of one macrotick (pOffsetCorrectionOut >> gdMacrotick), the node enters NORMAL\_ACTIVE with the first startup attempt.

If the node is not able to correct the offset error because pOffsetCorrectionOut is too small (pOffsetCorrectionOut  $\leq$  gdMacrotick), the node enters ABORT\_STARTUP and is ready to try startup again. The next (second) startup attempt is not effected by this erratum.

### Scope:

The erratum is limited to applications where READY command is used to leave STARTUP, NORMAL ACTIVE, or NORMAL PASSIVE state.

#### Effects:

In the described case the integrating node tries to correct an erroneous cycle offset of one macrotick during startup.

#### Workaround

With a configuration of pOffsetCorrectionOut >> gdMacrotick • (1+cClockDeviationMax) the node will be able to correct the offset and therefore also be able to successfully integrate.

## FlexRay Al.100 First WUS following received valid WUP may be ignored

## Description:

When the protocol engine is in state WAKEUP\_LISTEN and receives a valid wakeup pattern (WUP), it transfers into state READY and updates the wakeup status vector CCSV.WSV[2:0] as well as the status interrupt flags SIR.WST and SIR.WUPA/B. If the received wakeup pattern continues, the protocol engine may ignore the first wakeup symbol (WUS) following the state transition and signals the next SIR.WUPA/B at the third instead of the second WUS.

### **Detailed Errata Description**

| S | C | o | b | е |  |

|---|---|---|---|---|--|

|   |   |   |   |   |  |

The erratum is limited to the reception of redundant wakeup patterns.

#### Effects:

Delayed setting of status interrupt flags SIR.WUPA/B for redundant wakeup patterns.

#### Workaround

None.

## FlexRay Al.101 READY command accepted in READY state

### Description:

The E-Ray module does not ignore a READY command while in READY state.

### Scope:

The erratum is limited to the READY state.

#### Effects:

Flag CCSV.CSI is set. Cold starting needs to be enabled by POC command ALLOW COLDSTART (SUCC1.CMD = 1001<sub>R</sub>).

#### Workaround

None.

# FlexRay Al.102 Slot Status vPOC!SlotMode is reset immediately when entering HALT state

## Description:

When the protocol engine is in the states NORMAL\_ACTIVE or NORMAL\_PASSIVE, a HALT or FREEZE command issued by the Host resets

### **Detailed Errata Description**

vPOC!SlotMode immediately to SINGLE slot mode (CCSV.SLM[1:0] =  $00_B$ ). According to the FlexRay protocol specification, the slot mode should not be reset to SINGLE slot mode before the following state transition from HALT to DEFAULT CONFIG state.

### Scope:

The erratum is limited to the HALT state.

#### Effects:

The slot status vPOC!SlotMode is reset to SINGLE when entering HALT state.

#### Workaround

None.

# <u>FlexRay\_Al.103</u> Received messages not stored in Message RAM when in Loop Back Mode

After a FREEZE or HALT command has been asserted in NORMAL\_ACTIVE state, and if state LOOP\_BACK is then entered by transition from HALT state via DEF\_CONFIG and CONFIG, it may happen that acceptance filtering for received messages is not started, and therefore these messages are not stored in the respective receive buffer in the Message RAM.

## Scope:

The erratum is limited to the case where Loop Back Mode is entered after NORMAL\_ACTIVE state was left by FREEZE or HALT command.

#### Effects:

Received messages are not stored in Message RAM because acceptance filtering is not started.

#### Workaround

Leave HALT state by hardware reset.

**Detailed Errata Description**

## FlexRay X.001 Trigger User Reset after Power-On

After a Power-On the FlexRay Interrupt Request Flags (e.g. FR\_0IC.IR) are sometime set erroneous. After interrupt enabling (e.g. FR\_0IC.IE) and if the corresponding Interrupt Request Flag is set the interrupt routine will be called.

#### Workaround

Trigger a Functional / User Reset (i.e. Debug Reset, Internal Application Reset or Application Reset) by software and after that the FlexRay module is correct installed.

### **GPT12E X.002** Effects of GPT Module Microarchitecture

The present GPT module implementation provides some enhanced features (e.g. block prescalers BPS1, BPS2) while still maintaining timing and functional compatibility with the original implementation in the C166 Family of microcontrollers.

Both the GPT1 and GPT2 blocks use a finite state machine to control the actions within each block. Since multiple interactions are possible between the timers (T2 .. T6) and register CAPREL, these elements are processed sequentially within each block in different states. However, all actions are normally completed within one basic clock cycle.

The GPT2 state machine has 4 states (2 states when  $BPS2 = 01_B$ ) and processes T6 before T5. The GPT1 state machine has 8 states (4 states when  $BPS1 = 01_B$ ) and processes the timers in the order T3 - T2 (all actions except capture) - T4 - T2 (capture).

In the following, two effects of the internal module microarchitecture that may require special consideration in an application are described in more detail.

# 1.) Reading T3 by Software with T2/T4 in Reload Mode

When T2 or T4 are used to reload T3 on overflow/underflow, and T3 is read by software on the fly, the following unexpected values may be read from T3:

### **Detailed Errata Description**

- when T3 is counting  $\mathbf{up}$ ,  $0000_{H}$  or  $0001_{H}$  may be read from T3 directly after an overflow, although the reload value in T2/T4 is higher ( $0001_{H}$  may be read in particular if BPS1 =  $01_{B}$  and T3I =  $000_{B}$ ),

- when T3 is counting down, FFFF<sub>H</sub> or FFFE<sub>H</sub> may be read from T3 directly after an underflow, although the reload value in T2/T4 is lower (FFFE<sub>H</sub> may be read in particular if BPS1 = 01<sub>B</sub> and T3I = 000<sub>B</sub>).

Note: All timings derived from T3 in this configuration (e.g. distance between interrupt requests, PWM waveform on T3OUT, etc.) are accurate except for the specific case described under 2.) below.

#### Workaround:

- When T3 counts up, and value\_x < reload value is read from T3, value\_x should be replaced with the reload value for further calculations.</li>

- When T3 counts down, and value\_x > reload value is read from T3, value\_x should be replaced with the reload value for further calculations.

Alternatively, if the intention is to identify the overflow/underflow of T3, the T3 interrupt request may be used.

# 2.) Reload of T3 from T2 with setting $\mathtt{BPS1}$ = 01 $_B$ and $\mathtt{T3I}$ = 000 $_B$

When T2 is used to reload T3 in the configuration with  $BPS1 = 01_B$  and  $T3I = 000_B$  (i.e. fastest configuration/highest resolution of T3), the reload of T3 is performed with a delay of one basic clock cycle.

#### Workaround 1:

To compensate the delay and achieve correct timing,

- increment the reload value in T2 by 1 when T3 is configured to count up,

- decrement the reload value in T2 by 1 when T3 is configured to count down.

#### Workaround 2:

Alternatively, use T4 instead of T2 as reload register for T3. In this configuration the reload of T3 is not delayed, i.e. the effect described above does not occur with T4.

**Detailed Errata Description**

## OCDS\_X.003 Peripheral Debug Mode Settings cleared by Reset

The behavior (run/stop) of the peripheral modules in debug mode is defined in bitfield SUMCFG in the KSCCFG registers. The intended behavior is, that after an application reset has occurred during a debug session, a peripheral reenters the mode defined for debug mode.

For some peripherals, the debug mode setting in SUMCFG is erroneously set to normal mode upon any reset (instead upon a debug reset only). It remains in this state until SUMCFG is written by software or the debug system.

Some peripherals will **not** re-enter the state defined for debug mode after an application reset:

**GPT12**, **CAPCOM2**, **and MultiCAN** will resume normal operation like after reset, i.e. they are inactive until they are initialized by software.

In case the **RTC** has been running before entry into debug mode, and it was configured in SUMCFG to stop in debug mode, it will resume operation as before entry into debug mode instead.

All other peripheral modules, i.e. ADC, CCU6 and USIC, will correctly re-enter the state defined for debug mode after an application reset in debug mode.

For **Flash** and **CPU**, bitfield SUMCFG must be configured to normal mode anyway, since they are required for debugging.

#### Workaround

None.

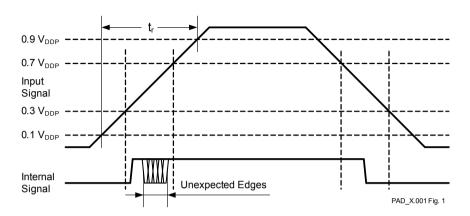

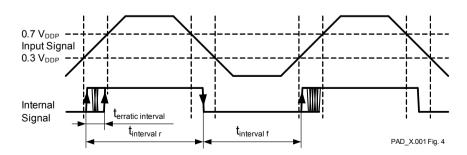

## PAD\_X.001 Additional Edges in the Input Signal

The digital input- and I/O-pins are designed using Schmitt trigger input structures with hysteresis. Even with this structure, it is possible that very slow rising edges may generate spikes, resulting in unexpected additional edges at the input signal.

The next picture **Figure 2** is an example for a slow input signal, with spikes shown on the slow rising input signal.

Figure 2 Example for a Slow Input Signal

The first rising edge in **Figure 2** of the internal signal is always valid. The edges which are marked with "Unexpected Edges" must be ignored.

Measurements have shown that a spike can be generated under the following conditions.

Table 10 Conditions for Additional Edges in the Input Signal

| Parameter              | Symbol    | Typ. Value | Unit | Note                |

|------------------------|-----------|------------|------|---------------------|

| Digital supply voltage | $V_{DDP}$ | 4.5 to 5.5 | V    | Upper Voltage Range |

| Junction Temperature   | $T_{J}$   | full range | °C   |                     |

| System frequency       | $f_{sys}$ | all        | MHz  |                     |

| Rising Slope           | $t_{r}$   | >1         | μs   |                     |

The reaction to this spike generation strongly depends on the application (hardware, software, internal and external noise). Although it is not possible to define how the application will react in all cases, it is possible to categorize how applications are typically affected, as shown below.

#### **Detailed Errata Description**

Applications which can be affected by a spike:

- · CCU6, CAPCOM2 and GPT inputs

- Port inputs

- · Interrupts input

Applications which should not be affected by a spike due to faster rising slope  $t_{\rm r}$  which is necessary for the application, due the interface protocol or due multiple sampling of the hardware:

- USIC

- CAN

- Others

### **Workaround for Input Capture Conditions**

## 1. Workaround for all Affected Applications

Use rising edges with faster rising slope  $t_r$  than defined in **Table 10**.

# 2. Workaround for CCU6, CAPCOM2 and GPT Inputs

No generic solution is available for these applications. Add or switch to a software solution.

For example, the software could check whether the measured signal values are in the expected range.

# 3. Workaround for Port Inputs

- The captured time interval value should be checked whether it is in a reasonable range.

- 2. The input pin should be read several times, and a majority decision may be made to decide whether the edge was correct or erratic.

Only if 1) and 2) indicate that the edge was reliable, the captured value should be used for further calculations. Otherwise, a substituted (extrapolated) value might be used.

### 4. Workaround for Interrupt Inputs

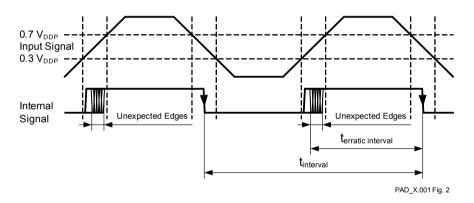

### 4.1 Falling Edge Detection Approach

- 1. Measure the time interval since the last interrupt (shown as in  $t_{\rm interval}$  in Figure 3 below) and check that it is in the expected time range. In the example, an erratic edge would cause the measured time interval  $t_{\rm erratic\ interval}$  to be approximately 50% of the expected value.

- 2. The state of the input pin that caused the interrupt could be read several times in the interrupt service routine and a majority decision made to check if the input pin really is at a low level to determine whether this is a genuine falling edge interrupt or whether the interrupt was triggered by a spike generated by a slow rising edge.

Figure 3 Falling Edge Detection Approach

Only if 1) and/or 2) indicate that the edge was reliable, should the rest of the interrupt service routine be executed.

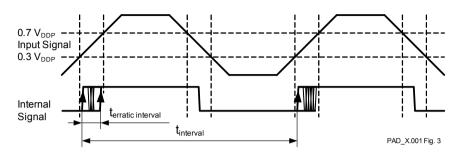

# 4.2 Rising Edge Detection Approach

In case of rising edge detection multiple interrupts would be generated when the spike occurs. The time interval since the last interrupt can be measured – if it is very small compared to the expected value, this would indicate a spike and the interrupt should be ignored.

Figure 4 Rising Edge Detection Approach

If the time between the rising signal edge and the rising edge caused by a spike  $t_{\rm erratic}$  is less than the ISR service time, a workaround would be to clear the interrupt request (IR) flag before the return from interrupt is done. The clearing of the IR flag will avoid a further erratic interrupt.

The preferred solution for interrupt handling is to use the rising edge detection.

## 4.3 Rising Edge and Falling Edge Detection Approach

The rising edge detection workaround works also if both edges are used as trigger for interrupt and the following conditions are valid:

- $t_{\text{erratic interval}} << t_{\text{interval r}}$  and

- t<sub>erratic interval</sub> << t<sub>interval f</sub>

Figure 5 Rising Edge and Falling Edge Detection Approach

Errata Sheet 46 V1.6, 2013-03

### **Detailed Errata Description**

## PARITY\_X.001 PMTSR Register Initialization

The PMTSR register content after start-up is 0100<sub>H</sub>, meaning the parity logic for SBRAM is not in standard mode of operation.

#### Workaround

If parity will be used as Memory Control mechanism for SBRAM, it must be enabled by initializing the PMTSR register with  $8000_H$ .

### RESET X.003 P2. [2:0] and P10. [12:0] Switch to Input

During the execution of an Application Reset and Debug Reset the pins P2.[2:0] and P10.[12:0] are intermediately switched to input.

These pins return to their previous mode approximately 35 system clock cycles after the application reset counter has expired (approx. 0.6 µs with default reset delay at 80 MHz).

If such a pin is used as output, make sure that this short interruption does not lead to critical system conditions.

#### Workaround

External pull devices can be added to have a defined level on these pins during Application and Debug Reset.

## <u>RESET\_X.004</u> Sticky "Register Access Trap" forces device into powersave mode after reset.

The system control unit (SCU) provides trap generation, to respond to certain system level events or faults. Certain trap sources maintain sticky trap flags which are only cleared explicitly by software, or by a power-on reset. These sticky trap flags are contained in the SCU register DMPMIT.

In case the "Register Access Trap" flag (DMPMIT.RAT) becomes set, but is not cleared before a debug, internal application, or application reset occurs, then the microcontroller will reset, but will fail to start-up correctly. The microcontroller start-up software will detect that the sticky trap flag is set, and

### **Detailed Errata Description**

will force the device into power-save mode with DMP\_1 shut down and DMP\_M powered.

#### Workaround

In response to the trap event, software must explicitly clear the sticky trap flag using the SCU register DMPMITCLR, before executing a debug, internal application, or application reset.

Note that this workaround does not address <u>unexpected</u> debug, internal application, or application resets which occur between the sticky trap event and the clearing of the sticky flags by software. To keep this exposure period as short as possible, it is recommended to clear the flag early in the trap routine.

Note: Register DMPMITCLR is protected by the register security mechanism after execution of the EINIT instruction and must be unlocked before accessing.

## SCU\_X.012 Wake-Up Timer RUNCON Command

The Wake-Up Timer can be started and stopped by the <code>WUCR.RUNCON</code> bit field. Under the precondition that the Wake-Up Timer is configured to stop when reaching zero ( $WUCR.ASP=1_B$ ) and if two Wake-Up Timer commands are executed successively (e.g. "start" is directly followed by "stop") then the second command will be ignored and will not change the state of the Wake-Up Timer.

#### Workaround

After executing the first command wait at least 4 Wake-Up Timer cycles ( $f_{WUT}$ ) before writing again to the WUCR.RUNCON bit field and requesting the second command.

# <u>StartUp\_X.003</u> Debug Interface Configuration from Flash can Fail Upon Power-On

This erratum only affects devices with a Date Code before G1203 (i.e. digit value < 1203).

Errata Sheet 48 V1.6, 2013-03

### **Detailed Errata Description**

XC2000/XE166 devices allow the user to select between a number of debug interface options including type (JTAG/DAP) and pin assignment.

The primary selection is done by configuration pins upon power-on, where one of the supported options is to install the debug interface according to the value taken from dedicated locations in user Flash (C001F0 $_{\rm H}$ ..C001F3 $_{\rm H}$ ). This option is selected by configuration pin values (HWCFG) xxxxx111 $_{\rm B}$  (code start from internal Flash) or x1100000 $_{\rm B}$  (code start from external memory). The other configurations directly selecting a debug mode work correctly.

The start-up procedure reads the dedicated locations in Flash too early - before Flash redundancy is installed - which can lead to an unrecoverable read error and terminate the boot process if the block from  ${\rm C001F0_H}$  to  ${\rm C001FF_H}$  is programmed by the user. A limited number of devices are affected – a rough estimation is below 1% from the production - and the (mis) behavior is constant. That means any device is either always error free or always failing if no programming of the block from  ${\rm C001F0_H}$  to  ${\rm C001FF_H}$  is done after the last power-on.

Note, that only the two mentioned modes upon power-on and only the read from dedicated locations during start-up are affected but not in general Flash and debug interface functionality.

#### Workaround

- Do not program the page from C00180<sub>H</sub> to C001FF<sub>H</sub>. This provides an erased, error free flash read during start-up (without installed flash redundancy) of DBGPRR register value which allows start-up from internal/external memory and JTAG position A.

- If these start-up configurations are used during development, a device that does not start-up in the desired debug configuration should be replaced by another device.

- Alternatively, select a debug interface not from Flash data but directly using configuration pins - refer to the User's Manual. With this it is not possible to start from external memory, nor is JTAG position A available.

### **Detailed Errata Description**

### USIC Al.004 Receive shifter baudrate limitation

If the frame length of SCTRH.FLE does not match the frame length of the master, then the baudrate of the SSC slave receiver is limited to  $f_{sys}/2$  instead of  $f_{sys}$ .

#### Workaround

None.

# <u>USIC Al.005</u> Only 7 data bits are generated in IIC mode when TBUF is loaded in SDA hold time

When the delay time counter is used to delay the data line SDA ( $\mathtt{HDEL} > 0$ ), and the empty transmit buffer  $\mathtt{TBUF}$  was loaded between the end of the acknowledge bit and the expiration of programmed delay time  $\mathtt{HDEL}$ , only 7 data bits are transmitted.

With setting HDEL=0 the delay time will be  $t_{HDEL}$  = 4 x 1/ $f_{SYS}$  + delay (approximately 60ns @ 80MHz).

#### Workaround

- Do not use the delay time counter, i.e use only HDEL=0 (default),

or

- write TBUF before the end of the last transmission (end of the acknowledge bit) is reached.

# <u>USIC\_AI.016</u> Transmit parameters are updated during FIFO buffer bypass

Transmit Control Information (TCI) can be transferred from the bypass structure to the USIC channel when a bypass data is loaded into TBUF. Depending on the setting of TCSR register bit fields, different transmit parameters are updated by TCI:

When SELMD = 1, PCR.CTR[20:16] is updated by BYPCR.SELO (applicable only in SSC mode)

### **Detailed Errata Description**

- When WLEMD = 1, SCTR.WLE and TCSR.EOF are updated by BYPCR BWLF

- When FLEMD = 1, SCTR.FLE[4:0] is updated by BYPCR.BWLE

- When HPCMD = 1, SCTR.HPCDIR and SCTR.DSM are updated by BHPC

- When all of the xxMD bits are 0, no transmit parameters will be updated

However in the current device, independent of the xxMD bits setting, the following are always updated by the TCI generated by the bypass structure, when TBUF is loaded with a bypass data:

- WLE, HPCDIR and DSM bits in SCTR register

- EOF and SOF bits in TCSR register

- PCR.CTR[20:16] (applicable only in SSC mode)

#### Workaround

The application must take into consideration the above behaviour when using FIFO buffer bypass.

# <u>WDT\_X.002</u> Clearing the Internal Flag which Stores Preceding WDT Reset Request

The information that the WDT has already been exceeded once is stored in an internal flag. In contrary to the documentation, that this flag can be cleared by writing a  $1_B$  to bit WDTCS.CLRIRF at any time, clearing of the internal flag is only possible, when the WDT is in Prewarning Mode.

#### Workaround 1

Applications following the proposal of Application Note **AP16103** (section `Using ESR pins to trigger a PORST reset`) to trigger a Power-on Reset upon a WDT event will find the internal flag cleared upon the Power-on Reset and thus will have no issue with this limitation.

#### Workaround 2

In case the WDT triggers a User Reset upon a WDT overflow, the internal flag will not be cleared by the reset itself. Any further overflow of the WDT will lead to a permanent reset of the device.

### **Detailed Errata Description**

Applications which intentionally let the WDT exceed once, e.g. in conjunction with an initial self test, might want to have the internal flag cleared to prevent a permanent reset upon a real WDT overflow.

If the internal flag shall be cleared by software, this must be done as a reaction on a WDT overflow in the time frame the WDT is in Prewarning Mode before the permanent User Reset will be triggered. The CPU is notified upon the WDT entering Prewarning Mode by issuing an interrupt request. The application can react on this request and clear the internal flag now by writing a  $1_{\rm B}$  to bit  ${\tt WDTCS.CLRIRF}$  e.g. within an ISR.

#### Workaround 3