## **Errata Sheet**

V1.2, 2008-06-04

Device XC161CJ-16F

Marking/Step (E)ES-BB, BB

Package PG-TQFP-144-7, P-TQFP-144-19

This Errata Sheet describes the deviations from the current user documentation.

The module oriented classification and numbering system uses an ascending sequence over several derivatives, including already solved deviations. So gaps inside this enumeration can occur.

This Errata Sheet applies to all temperature (SAB-/SAF-/SAK-.....) and frequency versions (.20./.40.), unless explicitly noted otherwise.

Versions beginning from V1.0 apply to the current documentation rules.

#### **Current Documentation**

- XC161CJ-16F Data Sheet V2.4, 2006-08

- XC161 User's Manual V2.2, Volume 1: System Units, 2004-01

- XC161 User's Manual V2.2, Volume 2: Peripheral Units, 2004-01

- C166S V2 User's Manual (Core, Instruction Set) V1.7, 2001-01

(for viewing, click on weblinks above and follow link to "Documents")

Note: Devices additionally marked with EES- or ES- or E followed by a 3-digit date code are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only. The specific test conditions for EES and ES are documented in a separate Status Sheet.

Note: For simplicity all versions are referred to by the term XC161 throughout this document.

#### **Contents**

| ection                                              | age |

|-----------------------------------------------------|-----|

| istory List/Change Summary                          | 2   |

| unctional Problems                                  | 7   |

| CDS and OCE Modules                                 | .31 |

| eviations from Electrical- and Timing Specification | .33 |

| pplication Hints                                    | .34 |

| ocumentation Update                                 | .56 |

## 1 History List/Change Summary

(from step (E)ES-BA, previous errata sheet: V1.1, step: (E)ES-BB, BB)

**Table 1** Functional Deviations

| Functional<br>Problem | Short Description                                                                                            | Fixed in step | Change |

|-----------------------|--------------------------------------------------------------------------------------------------------------|---------------|--------|

| EBC_X.003             | TwinCAN access with EBC enabled                                                                              |               |        |

| EBC_X.006             | Visibility of internal LXBus cycles on external address bus                                                  |               |        |

| SDLM_X.001            | Reset TXRQ - TXCPU                                                                                           |               |        |

| CPU_X.002             | Branch to wrong target after mispredicted JMPI                                                               |               |        |

| CPU_X.003             | Software Modification of Return Address on<br>System Stack in combination with<br>RET/RETP/RETS instructions |               | update |

| INT_X.007             | Interrupt using a Local Register Bank during execution of IDLE                                               |               |        |

| INT_X.008             | HW Trap during Context Switch in Routine using a Local Bank                                                  |               |        |

| INT_X.009             | Delayed Interrupt Service of Requests using a Global Bank                                                    |               |        |

| INT_X.010             | HW Traps and Interrupts may get postponed                                                                    |               | new    |

| PORTS_X.012.1         | Interference of Input Signals on P9.2 and P9.4 with internal Flash                                           |               |        |

| SCU_X.008.1           | Modification of register PLLCON while CPSYS = 1                                                              | EES-<br>BA    |        |

| SCU_X.009.1           | Oscillator is not locked                                                                                     |               |        |

| SCU_X.010             | Reset while PLL is not locked - step (E)ES-BA only                                                           | ES+BA<br>BA   |        |

| SCU_X.011             | Register Security Mechanism after Write Access in Secured Mode                                               |               |        |

| TwinCAN2.005          | Double Send                                                                                                  | EES-<br>BA    |        |

| TwinCAN2.006          | CPUUPD fast set/reset                                                                                        | EES-<br>BA    |        |

Errata Sheet 2/60 V1.2, 2008-06-04

## Table 1 Functional Deviations (cont'd)

| Functional<br>Problem | Short Description                                                                                                 | Fixed in step | - 3 |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|---------------|-----|--|

| TwinCAN_AI.007        | Transmit after error (former name: TwinCAN_X.007)                                                                 |               |     |  |

| TwinCAN_AI.008        | Double remote request (former name: TwinCAN_X.008)                                                                |               |     |  |

| TwinCAN_AI.009        | CPUUPD remote (former name: TwinCAN_X.009                                                                         |               |     |  |

| TwinCAN_AI.010        | Reserved Bits in Register MSGARHn[15:13]                                                                          |               |     |  |

| FLASH_X.004           | PACER trap after wake-up from Sleep/Idle mode                                                                     |               |     |  |

| FLASH_X.005.1         | Erase of Logical Sector 1, 2, 3, 4                                                                                |               |     |  |

| ASC_X.001             | ASC Autobaud Detection in 8-bit Modes with Parity                                                                 |               |     |  |

| ADC_X.003             | Coincidence of Result Read and End of next<br>Conversion or Start of Injected Conversion in<br>Wait for Read Mode | EES-<br>BA    |     |  |

| ADC_X.004             | ADC Overrun Error Generation when result is read during last cycle of conversion                                  | EES-<br>BA    |     |  |

| SLEEP_X.001           | Wake up trigger during last clock cycle before entry into sleep mode                                              |               |     |  |

| GPT12E_X.001          | T5/T6 in Counter Mode with BPS2 = 1X <sub>B</sub>                                                                 |               |     |  |

| IIC_AI.001            | Handling of the Receive/Transmit Buffer RTB                                                                       |               | new |  |

| IIC_AI.003            | SCL low time tLOW violated before repeated start condition in standard mode                                       |               | new |  |

| IIC_AI.005            | Restart condition only possible with CI = 0                                                                       |               | new |  |

### Table 2 OCDS and OCE Modules

| Functional<br>Problem | Short Description                                                                  | Fixed in step | Change |

|-----------------------|------------------------------------------------------------------------------------|---------------|--------|

| OCDS_X.001            | BRKOUT pulsing after Instruction Pointer Debug Event                               | EES-<br>BA    |        |

| OCDS_X.002            | OCDS indicates incorrect status after break_now requests if PSW.ILVL ≥ CMCTR.LEVEL |               |        |

Errata Sheet 3/60 V1.2, 2008-06-04

## Table 2 OCDS and OCE Modules (cont'd)

| Functional<br>Problem | Short Description                                          | Fixed in step | Change |

|-----------------------|------------------------------------------------------------|---------------|--------|

| OCE_X.001             | Wrong MAC Flags are declared valid at Core - OCE interface |               |        |

#### Table 3 AC/DC Deviations

| AC/DC<br>Deviations | Short Description                                                        | Fixed in step | Change |

|---------------------|--------------------------------------------------------------------------|---------------|--------|

| TAP_X.85            | Maximum ambient temperature during flash programming 85°C                | EES-<br>BA    |        |

| FCPUR_X.1632        | Frequency Limits for Flash Read Accesses - SAK temperature version only! | BB            |        |

| M40_WLE_X.001       | Minimum Ambient Temperature for Flash<br>Wordline Erase Command          | BB            |        |

## Table 4 Application Hints

| Hint         | Short Description                                               | Change |

|--------------|-----------------------------------------------------------------|--------|

| CPU_X.H1     | Configuration of Registers CPUCON1 and CPUCON2                  |        |

| CPU_X.H2     | Special Characteristics of I/O Areas                            |        |

| FLASH_X.H1.1 | Access to Flash Module after Program/Erase                      |        |

| FLASH_X.H2.2 | Access to Flash Module after Shut-Down                          |        |

| FLASH_X.H3.2 | Read Access to internal Flash Module with modified Margin Level |        |

| FLASH_X.H4   | Minimum active time after wake-up from sleep or idle mode       |        |

| SLEEP_X.H3.2 | Clock system after wake-up from Sleep Mode                      |        |

| IDLE_X.H1    | Entering Idle Mode after Flash Program/Erase                    |        |

| ADC_X.H1     | Polling of Bit ADBSY                                            |        |

| BREAK_X.H1   | Break on MUL/DIV followed by zero-cycle jump                    |        |

| OCDS_X.H001  | Effect of Bit OCDSIOEN in Register EMUCON                       |        |

| IIC_AI.H001  | Read of Bit ACKDIS                                              | new    |

Errata Sheet 4/60 V1.2, 2008-06-04

Table 4Application Hints (cont'd)

| Hint          | Short Description                                                                     | Change |  |  |

|---------------|---------------------------------------------------------------------------------------|--------|--|--|

| IIC_AI.H002   | Bit LRB is not cleared on read or write of RTB                                        |        |  |  |

| IIC_AI.H003   | IIC master cannot lose arbitration at acknowledge bit during read                     |        |  |  |

| IIC_AI.H004   | Jitter of fractional divider might violate the IIC timings                            | new    |  |  |

| IIC_AI.H005   | General call feature does not work with 10-bit address mode                           | new    |  |  |

| IIC_AI.H006   | TRX-Bit is not immediately set after writing to register RTB                          | new    |  |  |

| IIC_X.H1      | Maximum IIC Bus Data Rate at low fCPU                                                 |        |  |  |

| IIC_X.H2      | Timing of Bit IRQD                                                                    |        |  |  |

| POWER_X.H1.1  | Initialization of SYSCON3 for Power Saving Modes                                      |        |  |  |

| POWER_X.H2.2  | Power Consumption during Clock System Configuration                                   |        |  |  |

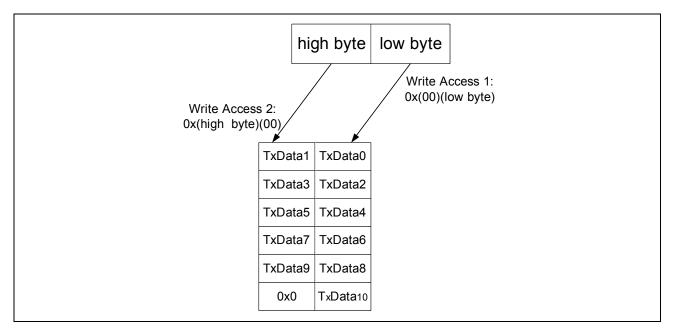

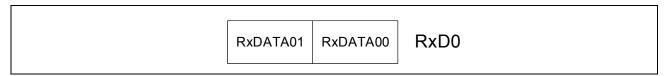

| SDLM_X.H1     | Writing the Transmit Buffer and reading the Receive Buffer in FIFO Mode               |        |  |  |

| RSTOUT_X.H1   | RSTOUT# driven by weak driver during HW Reset                                         |        |  |  |

| SCU_X.H1      | Shutdown handshake by software reset (SRST) instruction                               |        |  |  |

| SCU_X.H3      | Effect of PLLODIV on Duty Cycle of CLKOUT                                             |        |  |  |

| SCU_X.H4      | Changing PLLCON in Emergency Mode                                                     |        |  |  |

| SCU_X.H5      | Sleep/Idle/Power Down Mode not entered while PLLODIV = 0Fh                            |        |  |  |

| SCU_X.H6      | Interrupt request during entry into sleep mode                                        |        |  |  |

| SCU_X.H7      | VCO Configuration with Input Clock disconnected                                       |        |  |  |

| SCU_X.H8      | PLL Bypass Mode with VCO on                                                           |        |  |  |

| SCU_X.H10     | Register Security Mechanism usage with CPUCON1 and CPUCON2 registers                  |        |  |  |

| RTC_X.H1.1    | Resetting and Disabling of the Real Time Clock                                        |        |  |  |

| FOCON_X.H1    | Read Access to register FOCON                                                         |        |  |  |

| OSC_X.H001    | Signal Amplitude on Pin XTAL1                                                         |        |  |  |

| TwinCAN_AI.H2 | Reading Bitfield INTID                                                                |        |  |  |

| INT_X.H1      | Software Modifications of Interrupt Enable (xx_IE) or Interrupt Request (xx_IR) Flags |        |  |  |

| INT_X.H002    | Increased Latency for Hardware Traps                                                  |        |  |  |

Errata Sheet 5/60 V1.2, 2008-06-04

## Table 4Application Hints (cont'd)

| Hint          | Short Description                      | Change |

|---------------|----------------------------------------|--------|

| GPT12E_X.H001 | Capture Correction for Register CAPREL | new    |

## Table 5 Documentation Update

| Name               | Short Description                                                                          | Change |

|--------------------|--------------------------------------------------------------------------------------------|--------|

| INT_X.D1           | Interrupt Vector Location of CAPCOM Register 28                                            |        |

| RSTLEN_X.D1        | Duration of Internal Reset Sequence                                                        |        |

| SCU_X.D1.1         | Oscillator Gain Reduction                                                                  |        |

| SCU_X.D2.2         | Functionality of register OPSEN                                                            |        |

| SCU_X.D3           | Register PLLCON after software reset                                                       |        |

| SCU_X.D5           | VCO band after hardware/watchdog reset in single chip mode                                 |        |

| SCU_X.D6           | Register Security Mechanism - Unprotected Mode active until execution of EINIT instruction |        |

| WDTCON_X.D1        | Write access to register WDTCON                                                            |        |

| FLASH_X.D1         | Interaction between Program Flash and Security Sector Programming                          |        |

| PORTS_X.<br>D2_144 | Internal Pull-up Device active on P3.12 during Reset                                       |        |

| TwinCAN_AI.D1      | Reserved Bits in Registers of the TwinCAN Module                                           |        |

| CPU_X.D1           | Write Operations to Control Registers                                                      |        |

| ADC_X.D3           | ADC Sample Time with Improved/Enhanced Timing Control                                      |        |

| ID-Registers       | ID-Registers                                                                               |        |

Errata Sheet 6/60 V1.2, 2008-06-04

### 2 Functional Problems

#### EBC\_X.003 TwinCAN Access with EBC enabled

If the External Bus Controller (EBC) is enabled, a read or write access to the TwinCAN module fails when an external bus access with TCONCSx.PHA  $\neq$  00<sub>B</sub> precedes the TwinCAN access.

#### Workaround:

Since it is hard to predict the order of external bus and TwinCAN accesses (in particular when PEC transfers are involved), it is recommended to set bitfield PHA to  $00_B$  in all TCONCSx registers which are used for external bus accesses.

#### EBC\_X.006 Visibility of internal LXBus cycles on external address bus

When an external bus is enabled, accesses to internal LXBus modules are to some extent reflected on those parts of the external address bus that is not multiplexed, i.e.

- on those pins of Port 4 that are configured as segment address lines,

- and on the pins of PORT1 (P1L, P1H) if a non-multiplexed external bus mode is enabled in one of the FCONCSx registers.

The effect is as follows

- a) After an LXBus access (e.g. to the TwinCAN module), the address of the location accessed last on the LXBus remains visible on the non-multiplexed part of the external address bus, unless an external bus cycle immediately follows the LXBus cycle.

- b) During an internal LXBus access, the external address bus is tristated. Due to an internal race condition, the pads on the non-multiplexed part of the external address bus may already start to drive the LXBus address (for ~ 3 ns) before they are tristated. This may result in undefined logic levels on the non-multiplexed part of the external address bus during an internal LXBus cycle.

However, no external chip select signal CSx or ALE/RD/WR strobe is active during an internal LXBus cycle.

#### Workaround:

Not needed if external circuitry does not evaluate levels on external address bus during internal LXBus cycles.

Errata Sheet 7/60 V1.2, 2008-06-04

#### SDLM\_X.001 Reset TXRQ - TXCPU

A reset on bit TXRQ in register BUFFCON by software should reset the register TXCPU. This is the case, if blockmode (bit BMEN, register GLOBCON) is enabled.

Failure: In all other cases TXCPU is not reset, if TXRQ is reset by software.

Note: This problem is referred to as SDLM.11 in C161JC/JI devices.

#### Workaround:

Reset TXCPU by software.

#### <u>CPU\_X.002</u> Branch to wrong target after mispredicted JMPI

After a JMPI is initially mispredicted according to the static branch prediction scheme of the C166S V2, code execution may continue at a wrong target address in the following situations:

#### Situation I:

- a memory write operation is processed by the DMU

- followed by a MUL(U)

- followed by the mispredicted JMPI

#### Example\_1:

```

MOV mem, [Rwn]

MUL R13, R14

JMPI cc_NV, [R6]

```

#### Situation II:

- MUL(U) or DIV(L/U/LU)

- followed by not-mispredicted zero-cycle jump (e.g. JMPA, JMPR, JMPS; bit ZCJ (CPUCON1.0) = 1)

- followed by the mispredicted JMPI

#### Example\_2a:

```

MULU R13, R14

JMPA- cc_V, _some_target ; predicated not taken => correct

JMPI cc_NV, [R6] ; taken, but predicted not taken

```

It could be possible that the JMPI is at the jump target of the JMPA, if it is taken:

```

Example_2b:

```

```

MULU R13, R14

JMPA+ cc_NZ, _jmpi_addr ; predicted taken => correct

.... other code ....

_jmpi_addr: JMPI cc_NV, [R6] ; taken but predicted not taken

```

#### Effect on tools:

In the **Altium/Tasking** compiler (V7.0 and above) the problem is not present. The result of a MUL/DIV instruction is available through the MDL/MDH SFRs. These SFRs are not allocatable by the register allocator. Therefore, the compiler always needs a MOV instruction to transfer MDL/H to a GPR. This avoids the problem.

In the RT- and FP-libraries (v7.0 and above) the problem was not found. Versions lower than v7.0 do not explicitly support the C166S V2 core.

In case optimizations are implemented in future versions which could cause this problem to occur, also a workaround will be included.

All **Keil** C166 tool Versions (compiler and libraries) since V3.xx do not generate a MUL(U) or a DIV(L/U/LU) followed by either of the jump instructions JMPR, JMPS, JMPA, JMPI. Basically the support of the C166S V2 core requires anyway V4.21 or higher.

#### Workarounds:

Examples for program parts written in assembly language:

generally disable overrun of pipeline bubbles by clearing bit CPUCON2.OVRUN (CPUCON2.4 = 0). This will result only in a negligible performance decrease, and will prohibit corruption of the target IP of the JMPI.

or:

provide a NOP (or any other suitable instruction) between the MUL/DIV instructions and the succeeding jump in the above cases. To simplify, place a NOP between any MUL/DIV and a JMPR, JMPS, JMPA, JMPI that might follow it. Other branches (CALLs, jump-on-bit instructions) do not need to be taken into account.

Errata Sheet 9/60 V1.2, 2008-06-04

## <u>CPU\_X.003</u> Software Modification of Return Address on System Stack in combination with RET/RETP/RETS instructions

#### Introduction:

Upon subroutine calls (instructions CALLA/R/I/S, PCALL) or interrupts/traps, the return address and status information is saved on the system stack, including:

- IP: intra-segment address of the next, not executed instruction

- CSP: segment number of the next, not executed instruction (for inter-segment CALLS instructions and interrupt/traps only)

- PSW: processor status word for next, not executed instruction (for interrupt/traps only)

When the corresponding return instruction (RET, RETS, RETP, RETI) is executed, program execution normally continues - at the return address popped from the system stack - with the next instruction, i.e. the instruction linearly following the subroutine call, or the instruction following the one after which the interrupt/trap occurred.

In case the return address on the system stack has been modified by software, program execution will continue at this address - instead of the address that was originally pushed on the system stack - when the next return instruction is executed. This method might be used e.g. by operating systems, or by compilers in conjunction with specific options (e.g. stack models), to perform branches within or between code segments. Besides directly changing the contents of the stack pointer SP, two methods basically exist for manipulations of the return address:

- Method M1: the return address contained in the last stack frame is directly modified: [SP]+4: CSP<sub>o</sub> --> CSP<sub>m</sub>; CSP value originally pushed is modified to CSP<sub>m</sub> [SP]+2: IP<sub>o</sub> --> IP<sub>m</sub>; IP value originally pushed is modified to IP<sub>m</sub> [SP]: <Top of System Stack>

- Method M2: an additional frame with a new return (branch target) address is pushed onto the system stack. The original return address is still available on the system stack:

[SP]+8: CSP<sub>o</sub>; CSP value originally pushed on system stack by last CALLS

[SP]+6:  ${\rm IP_o}$ ; IP value originally pushed on system stack by last CALL(S)

[SP]+4:  $CSP_m$ ; CSP value additionally pushed on system stack

[SP]+2: IP<sub>m</sub>; IP value additionally pushed on system stack

[SP]: <Top of System Stack>

In order to optimize the execution speed of return instructions, the C166S V2 core additionally stores (mirrors) the 24-bit return address information (CSP<sub>r</sub>:IP<sub>r</sub>, r=1..6) of the last up to 6 subroutine calls (invoked by CALLA/R/I/S, PCALL) in a 'last in/first out' Return Stack (see User's Manual, IFU Block Diagram). Whenever one of the return instructions RET, RETS, RETP is executed, the information from the top of the Return Stack is used to already start fetching the return target instruction. When the actual return address from the system stack is available, it is compared with the information from the Return Stack. In case of a mismatch, the instruction that was 'speculatively'

Errata Sheet 10/60 V1.2, 2008-06-04

#### **Functional Problems**

read with the address information obtained from the Return Stack is cancelled, and a new fetch with the address from the system stack is started.

The Return Stack (including the potential performance increase) is not used in combination with interrupts/traps and the corresponding RETI instruction.

The Return Stack can only provide a performance increase when identical return addresses are delivered by the Return Stack and by the system stack. This is only the case when the system stack is not manipulated by software, i.e.

- the contents of the stack pointer SP is not explicitly modified by software

- the return address on the system stack is not directly modified by software (method M1)

- no additional 'return' addresses are pushed on the system stack by software to perform special branches (method M2), or RETI is used (after pushing PSW) to return from a subroutine call. Otherwise, Return Stack and system stack are no longer aligned, and the comparison of the return addresses will also fail for all remaining Return Stack entries (r=1..5).

#### **Problem Description:**

When the return address on the system stack, composed of  $CSP_m$  and/or  $IP_m$ , is modified by software, and the Return Stack is not empty, care must be taken that a valid instruction is also located at

- 1. address CSP<sub>rtop</sub>:IP<sub>rtop</sub> when the next return instruction is RETS

- 2. address CSP<sub>C</sub>: IP<sub>rtop</sub> when the next return instruction is RET or RETP

#### where:

- CSP<sub>rtop</sub> = CSP value on top of Return Stack

- = CSP value originally pushed on system stack by last call instruction if no other return instruction has been executed, else

- = CSP value originally pushed on system stack by last-nth call instruction if n other return instructions have been executed, and no other call instruction has been executed

- IP<sub>rtop</sub> = IP value on top of Return Stack

- = IP value originally pushed on system stack by last call instruction if no other return instruction has been executed, else

- = IP value originally pushed on system stack by last-nth call instruction if n other return instructions have been executed, and no other call instruction has been executed

- CSP<sub>C</sub> = current contents of CSP

- valid instruction = code, or data decoded as instruction, that does not access memory areas that will generate a PACER trap (e.g. reserved memory areas, disabled flash, etc.)

Errata Sheet 11/60 V1.2, 2008-06-04

Return Stack empty = e.g. number of executed return instructions ≥ number of call instructions, or 6 consecutive return instructions are executed.

Otherwise, when no valid instruction is located at the address described above, a PACER trap could be generated (due to a 'speculative' access) instead of branching to the modified return address from the system stack.

#### Examples:

#### **Case 1** (see 1. in Problem Description above):

Usually, a valid instruction will be located at address CSP<sub>rtop</sub>:IP<sub>rtop</sub>, i.e. at the location after the original CALL instruction. An exception is the case where the CALL instruction is the last instruction in a code section that is terminated with RETV (virtual return, no code generated), and a data section directly follows this code section, e.g.:

```

CALLS f_no_ret ; function modifying system stack, does

; not return to following instruction

; virtual return (no code generated)

RETV

; end of procedure xy

_proc_xy ENDP

_sec_c_xy ENDS

; end of code section xy

_sec_d_ab SECTION DATA; begin of data section ab

_ab_array LABEL WORD ; next location used by locator

; this address is pushed on system

; stack by CALLS

DW OFFFAh; data located here, decoded as instruction,

DW 0000h ; must result in a valid instruction

; FA FF 00 00 is decoded as JMPS OFFh, 0000h

; ==> access to FF:0000 will cause PACER trap

; when function f_no_ret executes RETS

```

In the above example, a PACER trap will be generated after the RETS instruction (corresponding to the CALLS instruction) at the end of function  $f_{no}$ ret is executed: the speculatively prefetched instruction JMPS 0FFh, 0000h is trying to access a reserved memory area.

#### **Case 2** (see 2. in Problem Description above):

When a RET or RETP instruction is executed after a modification of the system stack, an intra-segment branch is performed. If the contents of the CSP register has not changed since the last CALL instruction (e.g. no JMPS/CALLS or interrupt has occurred), then  $CSP_C = CSP_{rtop}$ , which is the same situation as already discussed in Case 1 before.

Errata Sheet 12/60 V1.2, 2008-06-04

In case the last function was e.g. called with a CALLS instruction (inter-segment call), the current contents CSP<sub>C</sub> of the Code Segment Pointer CSP is different from the CSP value that has been originally pushed on the stack by the CALLS instruction, e.g.:

```

Location: Instruction

C1′9876:

CALLS CO, 3456h; inter-segment call,

; return addr CSP=C1, IP=987A

; pushed on system stack by HW

. . .

C0'3456:

MOV Rx, #5678h

; prepare intra-segment branch

C0'345A:

PUSH Rx

; push 'return' addr IPm=5678

; on system stack by SW

C0'345C: RET

; branch (=return) to 'target'

; addr IPm=5678 with CSPc=C0

. . .

C0'5678: <target_instr> ; continue at branch target

. . .

CO'987A: <valid_instr> ; code or data located here must

; result in a valid instruction

```

In the above example, if the instruction (fragment) or data located at address  $CSP_C:IP_m$  (here: C0'987A) - when decoded as instruction - does not result in a valid instruction, a PACER trap will be generated after the RET instruction is executed.

#### Workaround 1

Do not perform modifications of the return address on the system stack.

#### Workaround 2 (when stack modification method M1 is used)

To avoid generation of the (unjustified) PACER trap,

- use RETS to branch to the modified return address CSP<sub>m</sub>:IP<sub>m</sub> after manipulation of the system stack. In case the last subroutine call was only an intra-segment CALL, extend the last stack frame with CSP<sub>m</sub>, and

- use a real return instruction (e.g. RETS) instead of the virtual RETV when the last executed call instruction was the last instruction of a code section followed by a data section. This ensures that a valid instruction is located after the original CALL/S instruction.

### Workaround 3 (when stack modification method M2 is used)

To avoid generation of the (unjustified) PACER trap,

use RETI to branch to the modified return address CSP<sub>m</sub>:IP<sub>m</sub> after manipulation of the system stack. RETI does not affect the Return Stack. In this case, the PSW must

Errata Sheet 13/60 V1.2, 2008-06-04

be pushed on the system stack in addition to the components of the modified return address  $CSP_m$  and  $IP_m$ , e.g.:

```

PUSH PSW; push current contents of PSW

PUSH Rx; push return segment address CSPm

PUSH Ry; push return address IPm

RETI; branch (=return) to CSPm:IPm

```

#### Workaround 4

After manipulation of the return address on the system stack, perform a sequence of 6 CALL instructions, followed by 6 return instructions. This will clear the Return Stack. Then, perform the return instruction that branches to the modified return address.

#### Workaround 5

If the modifications of the return instructions discussed in Workaround 2 .. 4 can not be performed (e.g. because the code is part of library functions or an operating system), the PACER trap service routine should be modified. To distinguish the 'unjustified' PACER trap from other defined conditions for a PACER trap, e.g.

- · first, check bit DBER in register FSR for flash double bit errors

- else, perform a sequence of six CALL instructions, followed by 6 return instructions to clear the Return Stack, and then return from the PACER trap handler, e.g.

```

BCLR PACER ; clear PACER trap flag

CALLS clear_ret_stack1 ; clear Return Stack

RETI ; return from PACER trap handler

...

clear_ret_stack1:

CALLS clear_ret_stack2

RETS

...

clear_ret_stack5:

CALLS clear_ret_stack6

RETS

CALLS clear_ret_stack6

RETS

clear_ret_stack6:

RETS

```

Errata Sheet 14/60 V1.2, 2008-06-04

#### INT\_X.007 Interrupt using a Local Register Bank during execution of IDLE

During the execution of the IDLE instruction, if an interrupt which uses a local register bank is acknowledged, the CPU may stall, preventing further code execution. Recovery from this condition can only be made through a hardware or watchdog reset.

All of the following conditions must be present for the problem to occur:

- The IDLE instruction is executed while the global register bank is selected (bit field BANK = 00<sub>B</sub> in register PSW),

- The interrupting routine is using one of the **local** register banks (BANK = 10<sub>B</sub> or 11<sub>B</sub>), and the local register bank is selected automatically via the bank selection registers BNKSEL0..3, (i.e. the interrupting routine has a priority level ≥12),

- The system stack is located in the internal dual-ported RAM (DPRAM, locations 0F600<sub>H</sub>...0FDFF<sub>H</sub>),

- The interrupt is acknowledged during the first 8 clock cycles of the IDLE instruction execution.

#### Workaround 1

Disable interrupts (either globally, or only interrupts using a local register bank) before execution of IDLE:

```

BCLR IEN ; Disable interrupts globally

IDLE ; Enter idle or sleep mode

BSET IEN ; After wake-up: re-enable interrupts

```

If an interrupt request is generated during this sequence, idle/sleep mode is terminated and the interrupt is acknowledged after BSET IEN.

#### Workaround 2

Do not use local register banks, use only global register banks.

#### Workaround 3

Locate the system stack in a memory other than the DPRAM, e.g. in DSRAM.

#### INT\_X.008 HW Trap during Context Switch in Routine using a Local Bank

When a hardware trap occurs under specific conditions in a routine using a local register bank, the CPU may stall, preventing further code execution. Recovery from this condition can only be made through a hardware or watchdog reset.

All of the following conditions must be present for this problem to occur:

The routine that is interrupted by the hardware trap is using one of the local register banks (bit field PSW.BANK = 10<sub>B</sub> or 11<sub>B</sub>)

Errata Sheet 15/60 V1.2, 2008-06-04

- The system stack is located in the internal dual-ported RAM (DPRAM, locations 0F600<sub>H</sub>...0FDFF<sub>H</sub>)

- The hardware trap occurs in the second half (load phase) of a context switch operation triggered by one of the following actions:

- a) Execution of the IDLE instruction, or

- b) Execution of an instruction writing to the Context Pointer register CP (untypical case, because this would mean that the routine using one of the local banks modifies the CP contents of a global bank)

#### Workaround 1

Locate the system stack in a memory other than the DPRAM, e.g. in DSRAM.

#### Workaround 2

Do not use local register banks, use only global register banks.

#### Workaround 3

Condition b) (writing to CP while a local register bank context is selected) is not typical for most applications. If the application implementation already eliminates the possibility for condition b), then only a workaround for condition a) is required.

The workaround for condition a) is to make sure that the IDLE instruction is executed within a code sequence that uses a global register bank context.

## INT X.009 Delayed Interrupt Service of Requests using a Global Bank

Service of an interrupt request using a global register bank is delayed - regardless of its priority - if it would interrupt a routine using one of the local register banks in the following situations:

#### Case 1:

- The Context Pointer CP is written to (e.g. by POP, MOV, SCXT .. instructions) within a routine that uses one of the local register banks (bit field PSW.BANK = 10<sub>B</sub> or 11<sub>B</sub>),

- Then an interrupt request occurs which is programmed (with GPRSELx = 00<sub>B</sub>) to automatically use the **global** bank via the bank selection registers BNKSEL0..3 (i.e. the interrupting routine has a priority level ≥12).

Note that this scenario is regarded as untypical case, because this would mean that the routine using one of the local banks modifies the CP contents of a global bank.

In this case service of the interrupt request is delayed until bit field PSW.BANK becomes  $00_B$ , e.g. by explicitly writing to the PSW, or by an implicit update from the stack when executing the RETI instruction at the end of the routine using the local bank.

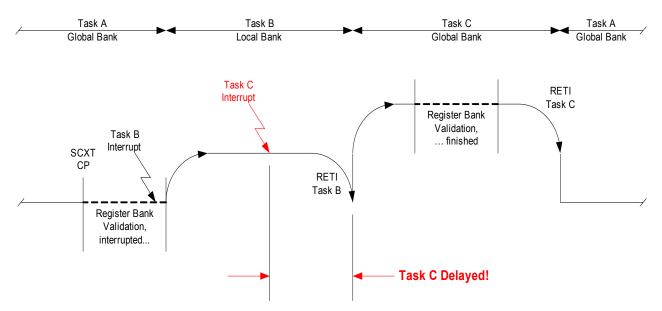

Case 2 (see also Figure 1):

Errata Sheet 16/60 V1.2, 2008-06-04

- The Context Pointer CP is written to (e.g. by POP, MOV, SCXT .. instructions) within a routine (Task A) that uses a **global** register bank (bit field PSW.BANK = 00<sub>B</sub>), i.e. the context for this routine will be modified,

- This context switch procedure (19 cycles) is interrupted by an interrupt request (Task B) which is programmed (with GPRSELx = 1X<sub>B</sub>) to automatically use one of the local banks via the bank selection registers BNKSEL0..3 (i.e. the interrupting routine has a priority level ≥12),

- Before the corresponding interrupt service routine is finished, another interrupt request (Task C) occurs which is programmed (with GPRSELx =  $00_B$ ) to automatically use the **global** bank via the bank selection registers BNKSEL0..3 (i.e. the interrupting routine has a priority level  $\geq$ 13)

In this case service of this interrupt request (for Task C) is delayed until bit field PSW.BANK becomes  $00_B$  after executing the RETI instruction at the end of the routine (Task B) using the local bank.

Figure 1 Example for Case 2: Interrupt Service for Task C delayed

#### **Workaround for Case 1**

Do not write to the CP register (i.e. modify the context of a global bank) while a local register bank context is selected.

#### Workaround for Case 2

When using both local and global register banks via the bank selection registers BNKSEL0..3 for interrupts on levels ≥12, ensure that there is no interrupt using a global register bank that has a higher priority than an interrupt using a local register bank.

Errata Sheet 17/60 V1.2, 2008-06-04

#### **Functional Problems**

#### Example 1:

Local bank interrupts are used on levels 14 and 15, no local bank interrupts on level 12 and 13. In this case, global bank interrupts on level 15 must not be used.

#### Example 2:

Local bank interrupts are used on level 12. In this case, no global bank interrupts must be used on levels 13, 14, 15.

#### INT\_X.010 HW Traps and Interrupts may get postponed

Under the special conditions described below, a hardware trap (HWTx) and subsequent interrupts, PEC transfers, OCDS service requests (on priority level  $< 11_H$ ) or class B and class A traps (if HWTx also was class A) may get postponed until the next RETI instruction is executed. If no RETI is executed, these requests may get postponed infinitely.

Both of the following conditions must be fulfilled at the same time when the trigger for the hardware trap HWTx occurs in order to cause the problem:

- 1. The pipeline is cancelled due to one of the following reasons:

- a) a multiply or divide instruction is followed by a mispredicted conditional (zero-cycle) jump.

- b) a class A hardware trap is triggered quasi-simultaneously with the request for a class B trap (= HWTx), i.e. the trigger for the class A trap arrives before the previously injected TRAP instruction for the class B trap has reached the Execute stage of the pipeline.

- In this case, the class A trap is entered, but when the RETI instruction at the end of the class A trap routine is executed, the pending class B trap (HWTx) is **not** entered, and subsequent interrupts/PECs/class B traps are postponed until the next RETI.

- c) a break is requested by the debugger.

- 2. The pipeline is stalled in the Execute or Write Back stage due to consecutive writes, or due to a multi-cycle write that is performed to a memory area with wait states (PSRAM, external memory).

#### Workaround

Disable overrun of pipeline bubbles by setting bit OVRUN (CPUCON2.4) = 0.

### PORTS\_X.012.1 Interference of Input Signals on P9.2 and P9.4 with internal Flash

As specified in table "DC Characteristics" of the Data Sheet, input signals may exceed the positive or negative supply voltages  $V_{\rm SSP}$  or  $V_{\rm DDP}$  by up to 0.5V, while during Overload Conditions (Vin >  $V_{\rm DDP}$ +0.5V or Vin <  $V_{\rm SSP}$ -0.5V), the (injected) overload

Errata Sheet 18/60 V1.2, 2008-06-04

#### **Functional Problems**

current must be limited to 5mA per pin/50 mA per device (see section "Operating Conditions").

However, two pins (**P9.2/CC18IO/CAN1\_RxD** and **P9.4/CC20IO**) have been identified that under exceptional conditions (e.g. massive low frequency noise) may cause side effects on internal flash (read or erase) operations before these overload limits are reached or exceeded, depending on the amplitude and width of the respective input signal:

### No problem will occur

- when the input levels on pin P9.2/CC18IO/CAN1\_RxD do not exceed the positive or negative supply voltages V<sub>SSP</sub> or V<sub>DDP</sub> as listed in the table below.

Otherwise, incorrect data may be read from the internal flash module, or program or erase operations may fail if this condition is present while the respective operation is in progress.

- when the input low level on pin **P9.4/CC20IO** does not exceed the negative supply voltage  $V_{\rm SSP}$  as listed in the table below. Otherwise, an erase operation of the internal flash module may fail if this condition is present while an erase operation is in progress.

### **Conditions for Amplitude and Width of Input Signal:**

No problem will occur for signals on pin P9.2/CC18IO/CAN1\_RxD with the following characteristics:

- for low or high pulses with an amplitude Vin <  $V_{\rm DDP}$ +0.5V or Vin >  $V_{\rm SSP}$ -0.5V **and** pulse width < 100 ns **and** duty cycle DC < 0.33 (e.g. high pulses < 100 ns with this amplitude are tolerated if the following low phase is > 200 ns)

- for steady state signals or pulses > 100 ns with an amplitude Vin <  $V_{\rm DDP}$ +0.2V or Vin >  $V_{\rm SSP}$ -0.2V

**No problem** will occur for signals on pin **P9.4/CC20IO** with the following characteristics:

- for low pulses with an amplitude Vin >  $V_{\rm SSP}$ -0.5V **and** pulse width < 1 µs **and** duty cycle DC < 0.33 (e.g. low pulses < 1 µs with this amplitude are tolerated if the following high phase is > 2 µs)

- for steady state signals or low pulses > 1  $\mu s$  with an amplitude Vin >  $V_{\rm SSP}$ -0.3V.

Typical overshoot/undershoot after signal transitions is normally uncritical (covered by duty cycle specification, see notes <sup>1)</sup> and <sup>2)</sup> below).

Errata Sheet 19/60 V1.2, 2008-06-04

Table 6 DC Characteristics P9.2 and P9.4 (Operating Conditions apply)

| Parameter                    | Symbol                                   | Limit                        | Limit Values           |   | Notes                                                           |  |

|------------------------------|------------------------------------------|------------------------------|------------------------|---|-----------------------------------------------------------------|--|

|                              |                                          | Min.                         | Max.                   |   |                                                                 |  |

| Input low voltage on<br>P9.2 | $V_{\rm IL}$ , SI $V_{\rm ILS}$          | R -0.2<br>instead of<br>-0.5 | not<br>affected        | V |                                                                 |  |

| Input low voltage on P9.2    | $V_{\rm IL}$ , SI $V_{\rm ILS}$          | ₹ -0.5                       | not<br>affected        | V | for pulses with $T_{low} < 100 \text{ ns}$ and DC $< 0.33^{1)}$ |  |

| Input high voltage on P9.2   | $V_{\mathrm{IH,}}$ SI $V_{\mathrm{IHS}}$ | R not affected               | V <sub>DDP</sub> + 0.2 | V |                                                                 |  |

| Input high voltage on P9.2   | $V_{\rm IH,}$ SI $V_{\rm IHS}$           | R not affected               | V <sub>DDP</sub> + 0.5 | V | for pulses with $T_{high} < 100 \text{ ns}$ and DC $< 0.33^{2}$ |  |

| Input low voltage on<br>P9.4 | $V_{\rm ILS}$ SI                         | R -0.3<br>instead of<br>-0.5 | not<br>affected        | V |                                                                 |  |

| Input low voltage on<br>P9.4 | $V_{\rm ILS}$ SI                         | ₹ -0.5                       | not<br>affected        | V | for pulses with $T_{low} < 1 \mu s$ and DC $< 0.33^{1)}$        |  |

<sup>1)</sup> For low pulses, DC =  $T_{low}/(T_{high}+T_{low})$  must be < 0.33. This means e.g. low pulses < 100 ns are tolerated if the following high phase is > 200 ns.

Using these pins as outputs is considered uncritical because the output signal is tightly coupled to the internal supply voltages  $V_{\rm SSP}$  or  $V_{\rm DDP}$ . If unused, these pins should be switched to output by software. If possible, these pins should be left floating after reset instead of being pulled high or low by an external pull device.

If used as inputs, a series resistor will further reduce (but can not under all circumstances fully exclude) the risk in case the input levels described above are exceeded. Furthermore, the risk resulting from input signals exceeding these levels is reduced if the device is not operated at the upper limits of supply voltage, temperature, and frequency at the same time.

Errata Sheet 20/60 V1.2, 2008-06-04

<sup>2)</sup> For high pulses, DC =  $T_{high}/(T_{high}+T_{low})$  must be < 0.33. This means e.g. high pulses < 100 ns are tolerated if the following low phase is > 200 ns.

#### SCU\_X.011 Register Security Mechanism after Write Access in Secured Mode

To modify an SFR that is protected by the register security mechanism, a certain security level has to be selected and/or a command sequence has to be executed prior to the write access to one of these registers. Table 6-15 in the User's Manual, volume System Units, lists all registers protected by the security mechanism (see copy of Table 6-15 below).

After selecting Secured Mode (bitfield  $SL = 01_B$  in register SCUSLS), a single command (command4) enables one single write access to a protected register. After this write access the protected registers are locked again automatically.

#### **Exception:**

After modification of registers CPUCON1, CPUCON2, EBCMOD0, EBCMOD1, TCONCSx, FCONCSx, ADDRSELx (which are not part of the SCU), all registers listed in Table 6-15 are **not locked** until the next write access to an SCU register (i.e. a register which is different from the group CPUCON1 .. ADDRSELx).

#### Workaround:

In order to lock all registers again, after a write access to the non-SCU registers CPUCON1 .. ADDRSELx a "dummy" write access to an SCU register should be executed. It is therefore proposed to use e.g. the read-only register IDCHIP for this purpose. The registers of the identification control block also belong to the SCU, and a write access to these read-only registers re-enables secured mode:

#### **Example:**

```

MOV R4, #2000H ; value to be stored in register EBCMOD0

EXTR #1 ; Access sequence in secured mode

MOV SCUSLC, #8E12H ; Command4: current password = EDH

OR EBCMOD0, R4 ; Access to EBCMOD enabled

; by preceding Command4

MOV IDCHIP, ZEROS ; dummy write to a read-only SCU register

; re-enables secured mode

```

### Table 7 Registers Protected by the Security Mechanism

| Register Name | Function                 | Loc. |

|---------------|--------------------------|------|

| RSTCON        | Reset control            | SCU  |

| SYSCON0       | General system control   | SCU  |

| SYSCON1       | Power management         | SCU  |

| PLLCON        | Clock generation control | SCU  |

Errata Sheet 21/60 V1.2, 2008-06-04

Table 7 Registers Protected by the Security Mechanism (cont'd)

| Register Name    | Function                                     | Loc. |  |

|------------------|----------------------------------------------|------|--|

| SYSCON3          | Peripheral management                        | SCU  |  |

| FOCON            | Peripheral management (CLKOUT/FOUT)          | SCU  |  |

| IMBCTR           | Control of internal instruction memory block |      |  |

| OPSEN            | Emulation control                            |      |  |

| EMUCON           | Emulation control                            | SCU  |  |

| WDTCON           | Watchdog timer properties                    | SCU  |  |

| EXICON           | Ext. interrupt control                       | SCU  |  |

| EXISEL0, EXISEL1 | Ext. interrupt control                       | SCU  |  |

| CPUCON1, CPUCON2 | CPU configuration                            | CPU  |  |

| EBCMOD0, EBCMOD1 | EBC mode selection                           | EBC  |  |

| TCONCSx          | EBC timing configuration                     |      |  |

| FCONCSx          | EBC function configuration                   |      |  |

| ADDRSELx         | EBC address window configuration             |      |  |

## TwinCAN\_AI.007 Transmit after Error

During a CAN error, transmission may stop (after EOF or an error frame), until a successful reception or a write access to the TwinCAN module.

#### **Detailed Description**

In case of a CAN error and when there is no other activity on the CAN module (e.g. frame reception or frame transmission on the other CAN node or write access to any CAN register), the transmission of messages may stop, even if some transmit requests are still set.

The CAN module will start transmitting immediately, after a reception or a write access to the module.

#### Workarounds:

- Write periodically FFFF<sub>H</sub> to one of the MSGCTRx registers, as this value is having no effect on the register.

- In case writing to a CAN register shall be the exception, use the last error code (LEC) interrupt. This shall start writing to one of the MSGCTRx register FFFF<sub>H</sub>, in case the LEC value is unequal to 0.

Errata Sheet 22/60 V1.2, 2008-06-04

#### TwinCAN\_AI.008 Double remote request

After the transmission of the remote request, TXRQ is not cleared in the receive object, if NEWDAT is set. As a consequence the remote request is transmitted once again.

#### Workaround:

Clear NEWDAT after the reception of a data frame.

#### TwinCAN AI.009 CPUUPD remote

In case of a remote request to a standard message object which is chosen for transmission, a transmit of the data frame takes place, even if CPUUPD is currently set.

#### **Detailed Description**

If a transmit message object gets a remote request and there is no other message object with higher transmit priority pending for transmission, then the transmit object sends the data frame to answer the remote request, even if CPUUPD is set.

#### Workaround:

This workaround is only required in systems where remote requests are used.

To answer remote requests, the MMC bitfield in MSGFGCR has to be configured to a FIFO slave object instead of a standard message object for transmission. To reach this goal, the following settings for the corresponding message object are needed:

- bitfield MMC (MSGFGCRHn.10-8) = 011<sub>B</sub> (FIFO functionality enabled (slave object))

- bitfield CANPTR (MSGFGCRHn.4-0) = n (the CAN Pointer shall reference itself, by referring to the message object number of this object)

- bit FD (MSGFGCRLn.13) = 0 (the CANPTR is updated after a correct reception)

## <u>TwinCAN\_AI.010</u> Reserved Bits in Register MSGARHn[15:13]

The 3 reserved bits MSGARHn[15:13] in the Message Object n Arbitration Register may be erroneously loaded with non-zero values (i.e. different from their reset values) under an arbitration loss condition.

#### Workaround:

If the received identifier is checked by software, the software should be written in a way that these bits have no impact on the decision (e.g. by masking off the upper 3 bits).

#### FLASH\_X.004 PACER Trap after Wake-Up from Sleep/Idle Mode

An unexpected Program Access Error Trap (flag PACER = 1 in register TFR) occurs after a wake-up event from sleep or idle mode under the following conditions:

- bit field PFCFG = 01<sub>B</sub> in register SYSCON1, i.e. the flash module is switched off during sleep or idle mode

- a wake-up event (interrupt, PEC transfer, NMI) occurs in a specific time window (few clock cycles) after execution of the IDLE instruction during the flash deactivation process

- and the corresponding interrupt/trap routine or the instruction following IDLE (in case interrupts are disabled) or the PEC source data are located in the internal flash.

#### Workaround 1:

Do not switch off the flash module in sleep or idle mode, i.e. leave bit field PFCFG =  $00_B$  in register SYSCON1 (default after reset). This increases power consumption to a certain extent while reducing the time overhead for sleep/idle mode entry and exit (in clocking modes where the clock is derived from the VCO).

#### Workaround 2

In order to avoid the problem (when PFCFG =  $01_B$ ), make sure that the wake-up trigger only occurs after the device has completely entered sleep or idle mode.

If the RTC is used as wake-up source, check e.g. the RTC before entering sleep mode. If the wake-up trigger will occur soon, either skip entry into sleep mode, or extend the time for the next wake-up. If the RTC time interval is reprogrammed, make sure that no interrupt occurs between reprogramming and entry into sleep mode.

#### Workaround 3

In order to differentiate an unexpected PACER trap due to a wake-up trigger in the critical time window from other events that can lead to a PACER trap, set a semaphore bit before executing the IDLE instruction., e.g.

```

ATOMIC #2

BSET sema_idle

IDLE

```

In the trap handler for the PACER trap, if the semaphore bit is set and no other indications for the PACER trap are found (e.g. error flags in register FSR are set), clear the semaphore bit and the PACER flag and return from the trap handler with RETI. The stack contains a valid return address in this case (e.g. address of instruction following IDLE in case interrupts were disabled during wake-up).

#### **Functional Problems**

For **PEC transfers** during sleep or idle mode, which will cause a PACER trap if they read data from flash, automatic return to sleep/idle mode is not accomplished with the concept described so far.

• In order to support return to idle/sleep mode after a PEC transfer (which is performed after the RETI instruction from the PACER trap routine is executed), e.g. a semaphore bit may be used. This bit may be set to '1' before the IDLE instruction is executed. All trap (except PACER) and interrupt service routines invoked after wake up from idle/sleep should clear this bit to '0'. After having returned from the PACER trap routine to the program in the internal flash, this bit should be tested (allow a sufficient time of e.g. 12 cycles for interrupt arbitration), and if it is still at '1' (i.e. no interrupts/traps have occurred), repeat the IDLE instruction for re-entry into idle/sleep mode.

#### Workaround 4

Use an auxiliary sequence in internal PRAM that bridges the time until the flash is ready after wake-up from sleep/idle mode, e.g.:

- Disable interrupts, and execute the IDLE instruction to enter sleep mode from the internal PRAM. After wake-up, the instruction following IDLE will be executed (if no hardware trap or NMI has occurred).

- Wait until the internal flash is ready after wake-up (check register FSR) before reading from the internal flash). If the sequence in internal PRAM that includes the IDLE instruction is not CALLed from internal flash (i.e. it is not terminated with a RETx instruction), at least 8 instructions that do not read from the internal flash should be inserted after the IDLE instruction to avoid speculative prefetches

- Enable the interrupt system again.

The following details should be considered:

- If hardware traps (including NMI) can occur, add the corresponding interrupt vectors to PRAM and modify register VECSEG to point to the PRAM space.

- In order to support return to idle/sleep mode after a PEC transfer, e.g. a semaphore bit may be used. This bit may be set to '1' before the IDLE instruction is executed. All trap and interrupt service routines invoked after wake up from idle/sleep should clear this bit to '0'. After having returned to the program in the internal flash and having enabled the interrupt system, this bit should be tested (allow a sufficient time of e.g. 12 cycles for interrupt arbitration), and if it is still at '1' (i.e. no interrupts/traps have occurred), repeat the auxiliary routine that prepares for re-entry into idle/sleep mode.

Errata Sheet 25/60 V1.2, 2008-06-04

#### FLASH\_X.005.1 Erase of Logical Sector 1, 2, 3, 4

When the last erase or program operation was performed on logical sector 5, a successive erase of logical sector 1, 2, 3, 4 may fail.

Typically, the problem is more likely to occur under the following external conditions:

- The voltage V<sub>DDI</sub> is above its nominal value (i.e. > 2.5 V).

- The voltage V<sub>DDP</sub> is below its nominal value (i.e. < 5.0 V).</li>

- The ambient temperature is above room temperature (i.e. > 25°C).

However, it can **not** be excluded that this problem does not occur outside the temperature and voltage ranges listed above.

An erase operation of a wordline in a logical sector and an erase operation of logical sector 0 does always work. Thus these operations can be done under all conditions.

This also implies that an erase or erase-and-program sequence starting with logical sector 0 and increasing the logical sector number will always work.

#### **Workaround 1:**

Do the erase logical sector operation twice:

```

Example code (for sector 4 starting at C0'8000h):

; data for 1st erase command

VOM

R4 , #0080h

; data for 2nd erase command

R5 , #00AAh

VOM

MOV R6 , #0033h

; data for 3rd erase command

; before erase operation check if flash is busy

CALL waitBusy

EXTS #0C0h , #3

; use segment 0C0h for next 3 operations

MOV 000AAh , R4

; 1st erase command

MOV 00054h , R5

; 2nd erase command

MOV 08000h , R6

; 3rd erase command

; for logical sector 4 at 08000h

; wait until erase operation is done

CALL waitBusy

EXTS #0C0h , #3

; use segment 0C0h for next 3 operations

MOV 000AAh , R4

; 1st erase command

MOV 00054h , R5

; 2nd erase command

MOV 08000h , R6

; 3rd erase command

; for logical sector 4 at 08000h

CALL waitBusy

```

#### Workaround 2:

Program one page of the logical sector first and then erase the logical sector:

```

Example code (for sector 4 starting at C0'8000h):

; wait for flash ready

CALL waitBusy

CALL enterPageMode

; enter Page mode for programming

CALL writePage

; program content of page buffer

MOV R4 , #0080h

; data for 1st erase command

; data for 2nd erase command

MOV R5 , #00AAh

MOV R6 , #0033h

; data for 3rd erase command

CALL waitBusy ; before erase operation check if flash is busy

EXTS #0C0h , #3

; use segment OCOh for next 3 operations

MOV 000AAh , R4

; 1st erase command

MOV 00054h , R5

; 2nd erase command

MOV 08000h , R6 ; 3rd erase command to...

; ...logical sector 4 at 08000h

CALL waitBusy

; wait until erase operation is done

waitBusy:

; check busy flag in FSR

EXTS #0FFh, #1 ; use segment 0FFh for next operation

MOV R7 , 0F000h ; read FSR

JB

R7.0 , waitBusy ; if flash still busy loop again

RET

enterPageMode:

, #00AAh ; first command address for enter page mode

MOV R4

, #0050h; first command data for enter page mode

MOV R5

```

```

, #08000h; page address of logical sector 4

VOM

EXTS #0C0h, #2

[R4] , R5

; first command of enter page mode sequence

VOM

VOM

[R6] , R4

; second command of enter page mode sequence

RET

writePage:

, #00AAh ; first write page sequence address

VOM

R4

R5

, #00A0h ; first write page sequence data

VOM

, #005Ah ; second write page sequence address

VOM

R6

MOV

R7 , #00AAh ; second write page sequence data

EXTS #0C0h, #2

[R4] , R5

; first command of write page sequence

VOM

[R6] , R7

; second command of write page sequence

VOM

RET

```

The second workaround is faster than the first workaround. While the first approach takes about 200 ms, the second approach only takes about 100 ms.

Note: Usually it is not allowed to program a page twice without an erase operation inbetween. This may lead to flash read problems in user applications. In this case double programming is not critical, because the program operation is followed by an erase operation.

After a reset the default configuration of the flash module allows an erase of logical sector 1, 2, 3, 4 without using one of the workarounds listed above.

## ASC\_X.001 ASC Autobaud Detection in 8-bit Modes with Parity

The Autobaud Detection feature of the Asynchronous/Synchronous Serial Interface (ASC) does **not** work correctly for **8-bit** modes **with** even or odd **parity**.

The Autobaud Detection feature works correctly for 7-bit modes with even or odd parity, and for 8-bit modes without parity.

Errata Sheet 28/60 V1.2, 2008-06-04

**Functional Problems**

### **GPT12E\_X.001** T5/T6 in Counter Mode with BPS2 = $1X_B$

When T5 and/or T6 are configured for counter mode (bit field  $TxM = 001_B$  in register GPT12E\_TxCON, x = 5, 6), and bit field **BPS2 = 1X**<sub>B</sub> in register GPT12E\_T6CON, then edge detection for the following count input and control signals does not work correctly: **T5IN, T6IN, T5EUD, T6EUD**.

Note: The configuration where T5 counts the overflow/underflow events of T6 is not affected by this problem.

#### Workaround

Do not set bit field BPS2 =  $1X_B$  in register GPT12E\_T6CON when T5 and/or T6 are configured for counter mode. Use only settings BPS2 =  $0X_B$  when T5 and/or T6 are configured for counter mode.

### **IIC AI.001** Handling of the Receive/Transmit Buffer RTB

Due to incorrect internal handling of the Transmit Byte Counter (bit field CO), the following problems will occur:

- 1. Unexpected IRQD in slave on stop/restart condition: If the master receiver wants to stop the transfer, it must signal to the slave the end of data by not generating an acknowledge on the last byte. The slave generates the interrupts IRQD, IRQE and releases the data line. With getting the stop condition (generated by the master) the slave generates both interrupts IRQE and IRQD for a second time, instead of IRQE only.

- 2. Incorrect buffer handling by master receiver: If the master receiver was configured with 1 byte buffer ( $CI=00_B$ ) the first transmit byte of data from slave will not be written to its register RTB0. If more than 1 byte was selected, the first byte is written to RTB1.

#### Workaround for 1.

At the first IRQE interrupt (for the no acknowledge), perform as many dummy (byte or word) reads to RTB as are required to read the number of bytes indicated in bit field CO. This resets bit field CO, because these bits are not writeable (bit IRQD will also be cleared if bit INT=0, otherwise it must be cleared by software).

### Workaround for 2.

Perform a dummy read to RTB after the slave address was transmitted and bit TRX was cleared (bit IRQD will be cleared if bit INT=0, otherwise it must be cleared by software).

## <u>IIC\_AI.003</u> SCL low time tLOW violated before repeated start condition in standard mode

With setting bit RSC and clearing interrupt flags (IRQD, IRQE, IRQP) the master wants to send a repeated start condition. The SCL line is released, but the minimum SCL low hold time is not met (SCL to low is asserted already, if SDA line is high and the minimum low time is not elapsed). Actually it is only 1/4 of the period defined by the baudrate instead of 4.7 us (as defined in the IIC standard).

#### Workaround

If this is not tolerated, use baudrate <= 50 kbit/s for standard mode.

#### IIC Al.005 Restart condition only possible with CI = 0

If the (Multi) Master generates a repeated start condition with transmit buffer length CI > 0, then erroneously further repeated start conditions are generated for each transmitted byte (RTBx).

#### Workaround

Set CI to 0 for repeated start condition (RSC = 1).

Errata Sheet 30/60 V1.2, 2008-06-04

#### **OCDS and OCE Modules**

#### 3 OCDS and OCE Modules

The following issues have been found in the OCDS and OCE modules. Please see the debugger or emulator manufacturer's documentation whether or not these issues actually cause a problem or restriction when the respective tool is used.

## OCDS\_X.002 OCDS indicates incorrect status after break\_now requests if PSW.ILVL ≥ CMCTR.LEVEL

When the OCDS processes a break\_now request while the CPU priority level (in PSW.ILVL) is not lower than the OCDS break level (in CMCTR.LEVEL), the actual break is delayed until either PSW.ILVL or CMCTR.LEVEL is reprogrammed such that CMCTR.LEVEL > PSW.ILVL. If in the meantime further debug events have occurred, register DBGSR will still indicate the status of the first break\_now request. If e.g. a software break is executed, the OCDS will accept this, but register DBGSR will indicate the wrong cause of break.

#### Workarounds:

- If the application uses tasks with different levels and debugging is to take place using the OCDS break level feature (e.g. only tasks up to a maximum level are halted, higher-level tasks aren't halted, and the OCDS level is programmed in between), there is no problem if:

- only classic hardware breakpoints (IP address) or software breakpoints are used (i.e. no trigger on address, data, TASKID)

- no external pin assertions are used to trigger breaks

- no direct writes to DBGSR.DEBUG STATE are used to force breaks

- 2. If break\_now request sources are to be used, the maximum level of the application (PSW.ILVL) should always be lower than the programmed OCDS break level (e.g. PSW.ILVL ≤ 14<sub>D</sub> and CMCTR.LEVEL = 15<sub>D</sub>). This means that all generated break\_now requests by the OCDS will always be accepted, independent of the CPU or interrupt priority.

## OCE\_X.001 Wrong MAC Flags are declared valid at Core - OCE interface

In case a MAC instruction (Co...) is directly followed by a MOV MSW, #data16 instruction, the upper byte of data16 is output instead of the flags corresponding to the MAC instruction. The bug was found with code:

```

COSHR #00001h MOV MSW, #00100h ;(+ other variations of data16)

```

#### **OCDS and OCE Modules**

#### Workaround

Add a NOP instruction between the two instructions:

COSHR #00001h

NOP

MOV MSW, #00100h ; (+ other variations of data16)

**Deviations from Electrical- and Timing Specification**

## 4 Deviations from Electrical- and Timing Specification

No deviations from the Electrical- and Timing specification are known for this step.

Errata Sheet 33/60 V1.2, 2008-06-04

**Application Hints**

## 5 Application Hints

#### CPU\_X.H1 Configuration of Registers CPUCON1 and CPUCON2

The default values of registers CPUCON1 and CPUCON2 have been chosen to provide optimized performance directly after reset. It is recommended

- not to modify the performance related parts of register CPUCON1

- not to modify register CPUCON2, except for test purposes or for enabling specific workarounds under special conditions (see e.g. problem CPU\_X.002 or application hint BREAK X.H1).

CPUCON2: reset/recommended value = 8FBB<sub>H</sub>; enables several performance features

CPUCON1: reset/recommended value = 0..0 0XXX X111<sub>B</sub>; only the 3 LSBs are performance related

| Bit Position   | Field<br>Name | Value | Description                                                                                                                        |

|----------------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| CPUCON1.[15:7] | 0             | 0     | reserved                                                                                                                           |

| CPUCON1.[6:5]  | VECSC         | 00    | scaling factor for vector table, value depends on application, '00' is compatible to C166 systems                                  |

| CPUCON1.4      | WDTCTL        | 0     | configuration for scope and function of DISWDT/ENWDT instructions, value depends on application, '0' is compatible to C166 systems |

| CPUCON1.3      | SGTDIS        | 0     | segmentation enable/disable control, value depends on application                                                                  |

| CPUCON1.2      | INTSCXT       | 1     | enable interruptibility of switch context                                                                                          |

| CPUCON1.1      | BP            | 1     | enable branch prediction unit                                                                                                      |

| CPUCON1.0      | ZCJ           | 1     | enable zero cycle jump function                                                                                                    |

## **CPU\_X.H2** Special Characteristics of I/O Areas

As an element of performance optimization, the pipeline of the C166S V2 core may perform speculative read accesses under specific conditions. In case the prediction for the speculative read was wrong, the read to the actually required location is restarted. While this method is uncritical e.g. for accesses to non-volatile memories or SRAMs, it may cause problems on devices which do not tolerate speculative reads (e.g. FIFOs which are advanced on every read access).

#### **Application Hints**

No speculative reads are performed in memory areas which are marked as I/O area. This memory area includes

- the SFR and ESFR space (e.g. with buffers for received data from serial interfaces or A/D results)

- the 4-Kbyte internal I/O area (00'E000<sub>H</sub> ..00'EFFF<sub>H</sub>), including IIC<sup>1)</sup> and SDLM<sup>1)</sup> module

- the 2-Mbyte external I/O area (20'0000<sub>H</sub> ...3F'FFFF<sub>H</sub>), including the TwinCAN<sup>1)</sup> module (default: from 20'0000<sub>H</sub> ... 20'07FF<sub>H</sub>)

It is therefore recommended to map devices which do not tolerate speculative reads into the 2-Mbyte external I/O area  $(20'0000_H ..3F'FFFF_H)$ .

For further special properties of the I/O areas, see section IO Areas (3.6) in chapter Memory Organization in the User's Manual.

#### FLASH\_X.H1.1 Access to Flash Module after Program/Erase

After the last instruction of a program or erase command, the BUSY bit in register FSR is set to '1' (status = busy) after a delay of one instruction cycle. When polling the BUSY flag, one NOP or other instruction which is not evaluating the BUSY flag must be inserted after the last instruction of a program or erase command.

No additional delay is required when performing the first operand read or instruction fetch access from the flash module after the BUSY bit has returned to '0' (status = not busy).

#### FLASH X.H2.2 Access to Flash Module after Shut-Down

When the flash is disabled by software (shut-down) by writing bit PFMDIS = 1 in register SYSCON3.

- and it is (at some later time) enabled again by writing PFMDIS = 0

- and the instruction immediately following the instruction which sets PFMDIS = 0 is fetched or reads operands from internal flash

then the PACER flag in register TFR is set and the BTRAP routine is entered.

Therefore, it is recommended to insert 4 NOPs before the internal flash is accessed again after PFMDIS has been set to 0.

Errata Sheet 35/60 V1.2, 2008-06-04

<sup>1)</sup> this module is implemented in specific derivatives of the XC166 family

**Application Hints**

#### FLASH\_X.H3.2 Read Access to internal Flash Module with modified Margin Level

When the internal flash module is read (e.g. for test purposes) with modified margin level (i.e. bitfield MARLEVSEL =  $0001_B$  or  $0100_B$ ) in register MAR, an additional wait state must be selected in bitfield WSFLASH in register IMBCTR. This waitstate must be added to the number of flash waitstates that are required to match the flash access time to the CPU operating frequency.

#### FLASH\_X.H4 Minimum active time after wake-up from sleep or idle mode

If the flash module is automatically disabled upon entry into sleep or idle mode (bit field PFCFG =  $01_B$  in register SYSCON1), sleep or idle mode should not be re-entered before a minimum active ("awake") time has elapsed. Otherwise, the current consumption during this sleep/idle phase will be ~ 1 mA above the specified limits of the Data Sheet. Therefore,

- If code is executed from the **internal flash** after wake-up, at least 16 instructions should be executed from the internal flash before re-entering sleep/idle mode. This ensures that the flash module is actually accessed after wake-up, since more instructions are required than can be stored in the prefetch queue.

- If code is executed from **external memory or PRAM**, wait until the flash BUSY bit returns to '0' before re-entering sleep/idle mode.

- If PEC transfers with automatic return to sleep/idle mode shall be triggered by the wake-up event, use e.g. the following procedure:

Use an auxiliary routine in internal flash with the required minimum active time after wake-up from sleep or idle mode, e.g.

- define a semaphore bit that is set to '1' before the IDLE instruction is executed. All trap and interrupt service routines invoked after wake up from idle/sleep should clear this bit to '0'

- disable interrupts

- execute the IDLE instruction

- if idle or sleep mode is terminated by an interrupt request, the instructions following the IDLE instruction will be executed (the interrupt request flags remain set)

- if idle or sleep mode was terminated by an  $\overline{\text{NMI}}$ , the trap handler will be invoked

- enable interrupts to allow prioritization of requests for interrupt or PEC service

- the instructions following the IDLE instruction should test the flash BUSY bit in register FSR; when the flash is ready (BUSY = 0), and at least 12 instructions have been executed after the interrupt system has been enabled, and if the semaphore bit is still at '1' (i.e. no interrupts/traps have occurred), disable interrupts and return to the IDLE instruction.

Errata Sheet 36/60 V1.2, 2008-06-04

**Application Hints**

#### SLEEP\_X.H3.2 Clock system after wake-up from Sleep Mode

There are different wake-up behaviors, depending on the PLL control setting used in register PLLCON during entry into sleep mode, and depending on whether the RTC is running on the main oscillator. Note that in either case, the VCO is turned off during sleep mode, and does not contribute to any additional power consumption.

In bypass mode with VCO off (PLLCTRL = 00<sub>B</sub>), the device will directly continue to run on the frequency derived from the external oscillator input after wake-up from sleep. If the RTC is running on the main oscillator, the device is immediately clocked, since the oscillator (input XTAL1) is not turned off during sleep mode.