Microcontrollers

Edition 2007-08

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2007 Infineon Technologies AG

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### **Warnings**

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TC1796

32-Bit Single-Chip Microcontroller Delta BD-to-BE Step

Microcontrollers

## TC1796 Delta BD-to-BE Step, Documentation Addendum

## Revision History: V1.2 2007-08

| Previous Versions: V1.1, V1.0 |                                              |  |  |  |  |  |

|-------------------------------|----------------------------------------------|--|--|--|--|--|

| Page                          | Subjects (major changes since last revision) |  |  |  |  |  |

| 2                             | References to actual documents updated.      |  |  |  |  |  |

|                               |                                              |  |  |  |  |  |

#### **Trademarks**

TriCore® is a trademark of Infineon Technologies AG.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

# **Table of Contents**

# **Table of Contents**

| 1     | Introduction                        |

|-------|-------------------------------------|

| 1.1   | Functional Improvements/DIfferences |

| 1.1.1 | RTID Register                       |

| 1.1.2 | PCP                                 |

| 1.1.3 | Pads                                |

| 1.1.4 | SCU Control Register 3              |

| 1.1.5 | EBU 5                               |

| 1.1.6 | ADC 5                               |

| 1.1.7 | Single Scan Chain Mode (SSCM)       |

## 1 Introduction

This document describes functional differences and improvements of the TC1796 BE-Step in comparison to the previous B-Steps, especially the BD-Step.

The referenced documents to this addendum are located at the Internet page:

- www.infineon.com/tc1796

- TC1796 System Units User's Manual (Vol.1), V2.0, July 2007

- TC1796 Peripheral Units User's Manual (Vol.2), V2.0, July 2007

- TC1796 Data Sheet V0.7, March 2006

## 1.1 Functional Improvements/Differences

This section summarizes the functional differences and improvements of the TC1796 BE-Step.

## 1.1.1 RTID Register

In the TC1796 BE-Step the reset value of register RTID =  $0000 \ 0300_{H}$ .

#### 1.1.2 PCP

The erratum PCP\_TC.029 "Possible corruption of CPPN value when a nested channel is restarted" has been fixed in the BE-Step.

#### 1.1.3 Pads

This section summarizes all pad related changes and improvements.

- The ESD strength based on human body model of the BD-Step will be improved in the BE-Step. Detailed parameters are defined in the Data Sheet for the BE-Step.

- The erratum PWR\_TC.P009 "Power up behavior" with the problem: "High cross current at OCDS L2 ports during power up" is fixed in the BE-Step. Therefore, also the constraints for the power up sequence as defined in the data sheet can be relaxed concerning the OCDS trace pins.

- <u>Up to the BD-Step</u>, the input pads with spike filter functionality PORST, HDRST, and NMI have no hysteresis. In the BE-Step these three input pads have a built-in hysteresis.

- The JTAG module clock input TCLK and the JTAG module reset/enable input TRST have a weak pull-down device active during reset (PORST = 0). Caused by this change, the pad test feature for pins TCLK and TRST (bits SCU\_PTDAT2.TRST and SCU\_PTDAT2.TCK) is no more supported. This means, the two bits 3 and 4 in register SCU\_PTDAT2 are "rh" bits.

- In the BE-Step, the eight LVDS MSC Clock and Data output pads of the BE-Step are set into a high-impedance state if they are disabled by SCU\_CON.LCDEN = 0.

• In the BE-Step, the driver strength of class A1 and A2 pads have been improved. This especially affects the test conditions for the output low voltage  $V_{\rm OLA}$  and output high voltage  $V_{\rm OHA}$ . The detailed test condition values for  $I_{\rm OL}$  and  $I_{\rm OH}$  are defined in the Data Sheet for the BE-Step.

## 1.1.4 SCU Control Register

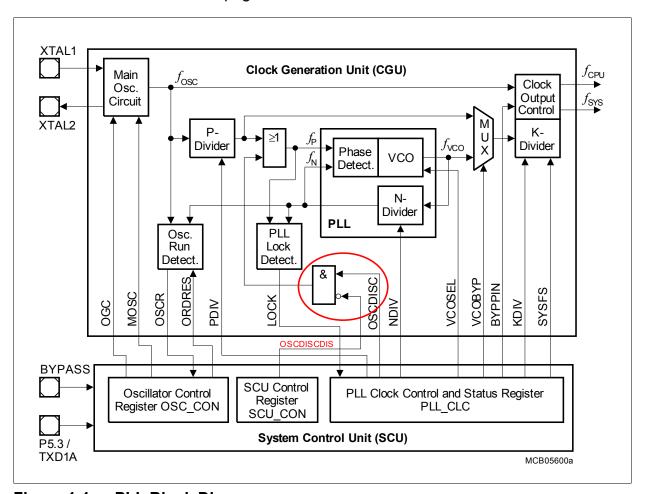

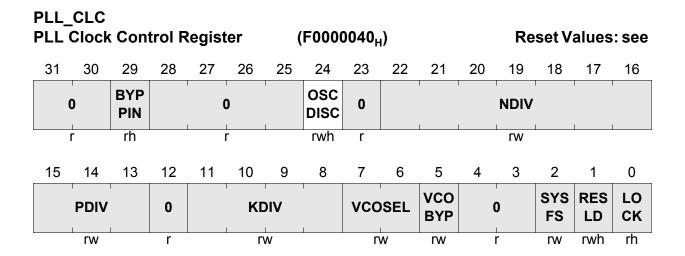

In the TC1796 BE-Step it is possible that  $f_{\rm OSC}$  remains connected to the PLL even if a PLL loss-of-lock failure is detected. This feature is controlled by the new bit OSCDISCDIS in the SCU\_CON register. **Figure 1-1** shows the changes of the CGU of the BE-Step (in the red circle). The changes in registers SCU\_CON and PLL\_CLC are also documented on the next pages.

Figure 1-1 PLL Block Diagram

| SCU_CON SCU Control Register |     |   |    |    |            |          | (F0000050 <sub>H</sub> ) |    |          |           | Reset Value: FF00 0002 <sub>H</sub> |                    |           |           |                 |            |

|------------------------------|-----|---|----|----|------------|----------|--------------------------|----|----------|-----------|-------------------------------------|--------------------|-----------|-----------|-----------------|------------|

| 3′                           | 1 3 | 0 | 29 | 28 | 27         | 26       | 25                       | 24 | 23       | 22        | 21                                  | 20                 | 19        | 18        | 17              | 16         |

|                              | -   |   |    | OI | NE         |          |                          |    |          | ZERO      |                                     | OSC<br>DISC<br>DIS | GIN       | N1S       | SSC<br>0<br>PDR | SLS<br>PDR |

|                              |     |   |    | r  | W          |          |                          |    |          | rw        | I                                   | rw                 | r         | W         | rw              | rw         |

| 15                           | 5 1 | 4 | 13 | 12 | 11         | 10       | 9                        | 8  | 7        | 6         | 5                                   | 4                  | 3         | 2         | 1               | 0          |

|                              |     | 0 |    |    | RPA<br>RAV | LD<br>EN | DTS<br>ON                |    | <b>D</b> | AN7<br>TM | NMI<br>EN                           | EPU<br>D           | CS<br>GEN | CS<br>OEN | CS<br>EEN       | FIEN       |

|                              |     | r |    |    | rw         | rw       | rw                       |    | r        | rw        | rws                                 | rw                 | rw        | rw        | rw              | rw         |

| Field      | Bits                   | Type | Description                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSCDISCDIS | 20                     | rw   | Oscillator Disconnect Disable This bit is used to disable the control of PLL_CLC.OCSDISC in a PLL loss-of-lock case.  In case of a PLL loss-of-lock the oscillator clock $f_{\rm OSC}$ is controlled by bit PLL_CLC.OCSDISC (default after reset)  In case of a PLL loss-of-lock the oscillator clock $f_{\rm OSC}$ is always connected to the PLL even in a PLL loss-of-lock case. |  |  |

| ZERO       | [23:2 <mark>1</mark> ] | rw   | Spare 0 Control Bits                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Field   | Bits | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCDISC | 24   | rwh  | Oscillator Disconnect  This bit is used to disconnect the divided $f_{\rm OSC}$ clock from the PLL in order to avoid unstable operation due to noise or sporadic clock pulses coming from the oscillator circuit while the PLL is still trying to lock to invalid clock pulses. The functionality of this bit can be disabled by setting SCU_CON.OSCDISCDIS to 1.  O Oscillator clock $f_{\rm OSC}$ is connected to the PLL.  Oscillator clock $f_{\rm OSC}$ is disconnected from the PLL (default after reset)  This bit is set by hardware if a PLL loss-of-lock failure is detected. |

#### 1.1.5 EBU

The erratum EBU\_TC.019 "Burst Mode signals delayed longer than specified" has been fixed in the BE-Step.

#### 1.1.6 ADC

The erratum ADC\_TC.033 "Wrong CHCON register might be used by inserted conversion" has been fixed in the BE-Step.

# 1.1.7 Single Scan Chain Mode (SSCM)

The SSCM is a test mode which is especially implemented in the BE-Step for analysis purposes. In SSCM, all device internal scan chains are concatenated to one single

chain. This configuration allows to access the scan chains with a minimum number of external pins. This section describes the hardware requirements for a system that allows use of the SSCM for in-system diagnostics.

#### **Entering Single Scan Chain Mode**

The SSCM is entered if the following signals are applied during the rising edge of PORST.

- $\overline{NMI} = 0$

- TMS = 0

- BYPASS = 1

- TESTMODE = 0

- P10.[3:0] / HWCFG[3:0] = 0100<sub>B</sub>

Note that the pins TESTMODE, BYPASS, and NMI are forced to their non-default states. All the pins mentioned in the list above must be permanently driven when the SSCM is active. This must be regarded during board design.

#### **Device State in Single Scan Chain Mode**

When the TC1796 is in SSCM, the pins/modules are in the following states:

- P0 to P9 I/O pins: high impedance state

- EBU pins: high impedance state

- Trace pins: high impedance state

- · LVDS pins: switched off

- Dedicated SSC pins: high impedance state

- BRKIN, BRKOUT: high impedance state

- TSTRES: high impedance input

- HDRST: drives 0

- XTAL1: drive through mode, not used during SSCM

- Analog inputs AN[43:0]: not selected

- CPU & Peripheral modules: logic connected together in single scan chain

#### Pins used to control the SSCM

The following device pins of the TC1796 must be accessible during SSCM for in-system diagnostics.

- TRST: JTAG reset input

- TDI: Scan chain enable

- TCK: Scan chain clock, used for shift and capture

- TMS: Scan chain input

- TDO: Scan chain output

www.infineon.com

Published by Infineon Technologies AG