# PMA71xx/PMA51xx

SmartLEWIS<sup>TM</sup> MCU

RF Transmitter FSK/ASK 315/434/868/915 MHz Embedded 8051 Microcontroller with 10 bit ADC Embedded 125 kHz ASK LF Receiver

# **Application Note**

I<sup>2</sup>C protocol for programming the PMA71xx/PMA51xx Revision 1.1, 2010-04-23

Wireless Control

#### Edition 2010-04-23

Published by Infineon Technologies AG 81726 Munich, Germany © 2010 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### **Table of Contents**

# **Table of Contents**

|     | Table of Contents 3                                  |

|-----|------------------------------------------------------|

|     | List of Tables                                       |

| 1   | Introduction                                         |

| 2   | General information 6                                |

| 2.1 | PMA71xx/PMA51xx PROGRAMMING Mode selection           |

| 2.2 | Setup for I <sup>2</sup> C communication             |

| 2.3 | I <sup>2</sup> C protocol                            |

| 2.4 | FLASH memory organization 8                          |

| 3   | PROGRAMMING Mode commands 8                          |

| 3.1 | FLASH Write Line 9                                   |

| 3.2 | FLASH Read Line                                      |

| 3.3 | FLASH Erase 9                                        |

| 3.4 | FLASH Check Erase Status                             |

| 3.5 | FLASH Set Code Lock (Lockbyte 2)                     |

| 3.6 | FLASH Set User Data Sector Lock (Lockbyte 3)         |

| 3.7 | Read Status                                          |

| 4   | Programming sequence for PMA71xx/PMA51xx code sector |

| 5   | Estimation of device programming time                |

| 5.1 | FLASH command transaction times                      |

| 5.2 | FLASH programming scenario 1                         |

| 5.3 | FLASH programming scenario 2                         |

| 6   | Application example (PMA Starterkit as programmer)   |

|     | List of Figures                                      |

|     | References                                           |

**Table of Contents**

#### **List of Tables**

# **List of Tables**

| Table 1  | Electrical parameters for I <sup>2</sup> C communication             | 9  |

|----------|----------------------------------------------------------------------|----|

| Table 2  | FLASH Erase: Sector byte                                             |    |

| Table 3  | FLASH Check Erase Status: Sector byte                                |    |

| Table 4  | FLASH Check Erase Status: Status byte                                |    |

| Table 5  | Read Status: Status byte                                             | 14 |

| Table 6  | Assumptions for the calculation of FLASH command transaction times   | 16 |

| Table 7  | FLASH Check Erase Status                                             | 16 |

| Table 8  | FLASH Erase                                                          |    |

| Table 9  | FLASH Write Line                                                     | 17 |

| Table 10 | FLASH Read Line                                                      | 17 |

| Table 11 | FLASH Read Status                                                    |    |

| Table 12 | FLASH Set User Data Sector Lock                                      | 18 |

| Table 13 | Programming time estimation with status verification every 256 bytes | 19 |

| Table 14 | Programming time estimation with verification of each byte           |    |

#### **List of Figures**

# **List of Figures**

| Figure 1  | Operating mode selection of the PMA71xx/PMA51xx after Reset       | 8    |

|-----------|-------------------------------------------------------------------|------|

| igure 2   | PMA71xx/PMA51xx hardware setup for I <sup>2</sup> C communication | 9    |

| igure 3   | I <sup>2</sup> C protocol                                         | . 10 |

| igure 4   | PMA71xx/PMA51xx FLASH memory organization                         | . 10 |

| igure 5   | Nomenclature for I <sup>2</sup> C communication                   | . 11 |

| igure 6   | FLASH Write Line command                                          | . 11 |

| igure 7   | FLASH Read Line command                                           | . 11 |

| igure 8   | FLASH Erase command                                               | . 12 |

| igure 9   | FLASH Erase: Sector byte                                          | . 12 |

| igure 10  | FLASH Check Erase Status command                                  | . 12 |

| igure 11  | FLASH Check Erase Status: Sector byte                             | . 12 |

| igure 12  | FLASH Check Erase Status: Status byte                             | . 13 |

| igure 13  | FLASH Set Lockbyte 3 command                                      | . 13 |

| igure 14  | Read Status command                                               | . 13 |

| Figure 15 | Read Status: Status byte                                          | . 13 |

| igure 16  | Possible programming sequence for PMA71xx/PMA51xx code sector     | . 15 |

| igure 17  | Usage of PMA Starterkit as programmer                             | . 20 |

|           |                                                                   |      |

Revision 1.1, 2010-04-23

Revision History: 2010-04-23, Revision 1.1

**Previous Revision: 1.0**

| Page | Subjects (major changes since last revision) Initial Version                                                                                        |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|      |                                                                                                                                                     |  |  |  |  |

|      | Restructured document: Table of Contents, List of Tables and List of Figures were moved to the beginning of the document.                           |  |  |  |  |

| 11   | Description of FLASH Write Line command changed: A read back verification of the written line is executed within each FLASH Write Line instruction. |  |  |  |  |

|      |                                                                                                                                                     |  |  |  |  |

|      |                                                                                                                                                     |  |  |  |  |

|      |                                                                                                                                                     |  |  |  |  |

#### Trademarks of Infineon Technologies AG

APOXI<sup>TM</sup>, BlueMoon<sup>TM</sup>, COMNEON<sup>TM</sup>, CONVERGATE<sup>TM</sup>, COSIC<sup>TM</sup>, C166<sup>TM</sup>, CROSSAVE<sup>TM</sup>, CanPak<sup>TM</sup>, CIPOS<sup>TM</sup>, CoolMos<sup>TM</sup>, CoolSet<sup>TM</sup>, Corecontrol<sup>TM</sup>, Dave<sup>TM</sup>, EasyPIM<sup>TM</sup>, EconoBridge<sup>TM</sup>, EconoDual<sup>TM</sup>, EconoPack<sup>TM</sup>, EconoPim<sup>TM</sup>, EiceDriver<sup>TM</sup>, Eupec<sup>TM</sup>, FCOs<sup>TM</sup>, Falc<sup>TM</sup>, Geminax<sup>TM</sup>, GoldMos<sup>TM</sup>, Hitfet<sup>TM</sup>, HybridPack<sup>TM</sup>, Isac<sup>TM</sup>, Isoface<sup>TM</sup>, Isopack<sup>TM</sup>, my-d<sup>TM</sup>, Mipaq<sup>TM</sup>, Modstack<sup>TM</sup>, NovalithIc<sup>TM</sup>, OmniTune<sup>TM</sup>, OmniVia<sup>TM</sup>, OptiVerse<sup>TM</sup>, OptiMos<sup>TM</sup>, Origa<sup>TM</sup>, Profet<sup>TM</sup>, Profet<sup>TM</sup>, Profet<sup>TM</sup>, Rasic<sup>TM</sup>, Reversave<sup>TM</sup>, Sceptre<sup>TM</sup>, Serocco<sup>TM</sup>, SicoFi<sup>TM</sup>, Smarti<sup>TM</sup>, Smint<sup>TM</sup>, Socrates<sup>TM</sup>, Satric<sup>TM</sup>, Sensonor<sup>TM</sup>, Sindrion<sup>TM</sup>, Smartlewis<sup>TM</sup>, Sieget<sup>TM</sup>, Truentry<sup>TM</sup>, Tempfet<sup>TM</sup>, Tricore<sup>TM</sup>, thinq!<sup>TM</sup>, Trenchstop<sup>TM</sup>, Vinax<sup>TM</sup>, Vinetic<sup>TM</sup>, X-Gold<sup>TM</sup>, XMM<sup>TM</sup>, X-PMu<sup>TM</sup>, XPOSYS<sup>TM</sup>, XWAY<sup>TM</sup>.

#### Other Trademarks

AMBA<sup>TM</sup>, ARM<sup>TM</sup>, MULTI-ICE<sup>TM</sup>, PRIMECELL<sup>TM</sup>, REALVIEW<sup>TM</sup>, THUMB<sup>TM</sup> of ARM Limited, UK. AUTOSAR<sup>TM</sup> is licensed by AUTOSAR development partnership. Bluetooth<sup>TM</sup> of Bluetooth SIG Inc. CAT-iq<sup>TM</sup> of DECT Forum. COLOSSUS<sup>TM</sup>, FirstGPS<sup>TM</sup> of Trimble Navigation Ltd. EMV<sup>TM</sup> of EMVCo, LLC (Visa Holdings Inc.). EPCOS<sup>TM</sup> of Epcos AG. FLEXGO<sup>TM</sup> of Microsoft Corporation. FlexRay<sup>TM</sup> is licensed by FlexRay Consortium. HYPERTERMINAL<sup>TM</sup> of Hilgraeve Incorporated. IEC<sup>TM</sup> of Commission Electrotechnique Internationale. IrDA<sup>TM</sup> of Infrared Data Association Corporation. ISO<sup>TM</sup> of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB<sup>TM</sup> of MathWorks, Inc. MAXIM<sup>TM</sup> of Maxim Integrated Products, Inc. MICROTEC<sup>TM</sup>, NUCLEUS<sup>TM</sup> of Mentor Graphics Corporation. Mifare<sup>TM</sup> of NXP. MIPI<sup>TM</sup> of MIPI Alliance, Inc. MIPS<sup>TM</sup> of MIPS Technologies, Inc., USA. muRata<sup>TM</sup> of MURATA MANUFACTURING CO. OmniVision<sup>TM</sup> of OmniVision Technologies, Inc. Openwave<sup>TM</sup> Openwave Systems Inc. RED HAT<sup>TM</sup> Red Hat, Inc. RFMD<sup>TM</sup> RF Micro Devices, Inc. SIRIUS<sup>TM</sup> of Sirius Sattelite Radio Inc. SOLARIS<sup>TM</sup> of Sun Microsystems, Inc. SPANSION<sup>TM</sup> of Spansion LLC Ltd. Symbian<sup>TM</sup> of Symbian Software Limited. TAIYO YUDEN<sup>TM</sup> of Taiyo Yuden Co. TEAKLITE<sup>TM</sup> of CEVA, Inc. TEKTRONIX<sup>TM</sup> of Tektronix Inc. TOKO<sup>TM</sup> of TOKO KABUSHIKI KAISHA TA. UNIX<sup>TM</sup> of X/Open Company Limited. VERILOG<sup>TM</sup>, PALLADIUM<sup>TM</sup> of Cadence Design Systems, Inc. VLYNQ<sup>TM</sup> of Texas Instruments Incorporated. VXWORKS<sup>TM</sup>, WIND RIVER<sup>TM</sup> of WIND RIVER SYSTEMS, INC. ZETEX<sup>TM</sup> of Diodes Zetex Limited.

Last Trademarks Update 2009-05-27

Introduction

#### 1 Introduction

This document describes how the PMA71xx/PMA51xx can be programmed via the I<sup>2</sup>C interface. In **Chapter 2** the PROGRAMMING Mode selection, the setup for I<sup>2</sup>C communication, the I<sup>2</sup>C protocol and the FLASH memory organization are explained. **Chapter 3** shows the structure of the I<sup>2</sup>C commands that can be used in the PROGRAMMING Mode. A possible procedure how data can be loaded into the code sector, verified and protected against undesired read outs is illustrated in **Chapter 4**. An estimation of the device programming time is given in **Chapter 5**. Finally **Chapter 6** describes how the PMA71xx/PMA51xx Starterkit can be used as programmer.

#### 2 General information

This chapter describes how the PROGRAMMING Mode of the PMA71xx/PMA51xx can be entered. Furthermore the setup for I<sup>2</sup>C communication, the I<sup>2</sup>C protocol which is used for communication with the programmer and the FLASH organization of the PMA71xx/PMA51xx is shown.

#### 2.1 PMA71xx/PMA51xx PROGRAMMING Mode selection

The PMA71xx/PMA51xx can be operated in three different operating modes

- PROGRAMMING Mode

- NORMAL Mode

- DEBUG Mode

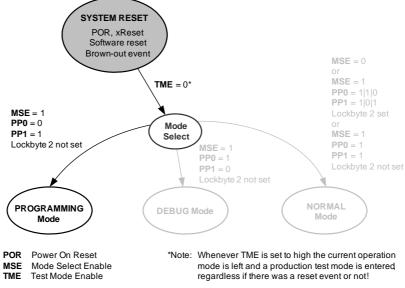

The Mode Select is entered after the System Reset expires. The levels on the I/O pins PP0 and PP1 are latched by the system controller and read by the operating system to determine the mode of operation of the device. Figure 1 shows the settings for the selection of the three different operating modes. The MSE, PP0 and PP1 levels must not change after reset release during the whole  $t_{MODE}$  (defined in [1]) period. Furthermore, the available operating modes are also dependent upon the state of the FLASH code lock (Lockbyte 2), which is used to secure the FLASH code sector against undesired read outs.

Figure 1 Operating mode selection of the PMA71xx/PMA51xx after Reset

**General information**

## 2.2 Setup for I<sup>2</sup>C communication

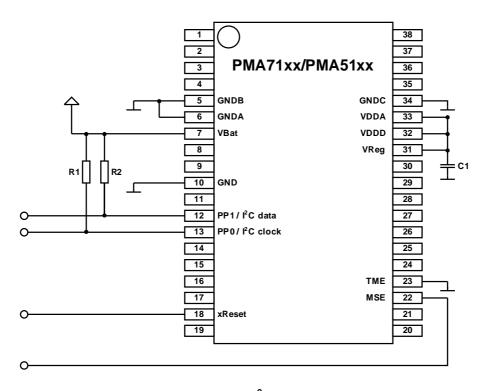

**Figure 2** and **Table 1** show the setup of the PMA71xx/PMA51xx required for I<sup>2</sup>C communication in PROGRAMMING Mode. Note that the resistors are required for reliable I2C communication for all modes other than NORMAL Mode, so these may be implemented as part of the programming equipment, rather than included as part of the application circuitry.

Figure 2 PMA71xx/PMA51xx hardware setup for I<sup>2</sup>C communication

Table 1 Electrical parameters for I<sup>2</sup>C communication

| Parameter                   | Min. | Тур. | Max. | Unit  | Remarks      |

|-----------------------------|------|------|------|-------|--------------|

| VBat                        |      |      |      | VDC   | refer to [1] |

| R1                          |      | 3.3k |      | Ohm   |              |

| R2                          |      | 3.3k |      | Ohm   |              |

| C1                          |      | 200n |      | Farad |              |

| I <sup>2</sup> C datarate   |      |      | 400k | Bit/s |              |

| I <sup>2</sup> C level low  |      |      |      | VDC   | refer to [1] |

| I <sup>2</sup> C level high |      |      |      | VDC   | refer to [1] |

### 2.3 I<sup>2</sup>C protocol

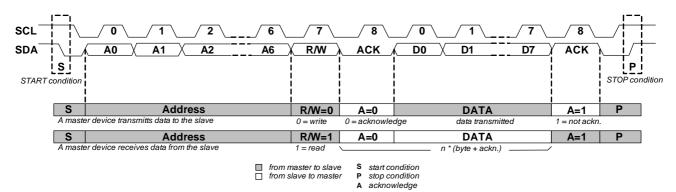

**Figure 3** shows the protocol which is used for I<sup>2</sup>C communication. Data are transmitted bit by bit on line SDA in coaction with line SCL. To start communication a master device generates a start condition. Subsequently the address and data are transferred each followed by an acknowledge from the receiving device. The data on the SDA line must be stable during the high period of the clock and may only be changed during SCL low phase. After all data have been transferred the master closes transmission with a stop condition. To continue data transfer (with changed read/write behavior) the master device could generate a restart condition immediately.

Figure 3 I<sup>2</sup>C protocol

#### 2.4 **FLASH** memory organization

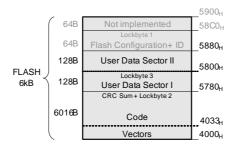

Figure 4 shows the FLASH memory organization of the PMA71xx/PMA51xx. The Flash Configuration + ID sector is written at the end of production test. Also the Lockbyte 1 is set and prevents a write access to this sector. User Data Sector I + II and the Code Sector can be written using PROGRAMMING Mode commands described in Chapter 3.

Figure 4 PMA71xx/PMA51xx FLASH memory organization

#### 3 **PROGRAMMING Mode commands**

In PROGRAMMING Mode the PMA71xx/PMA51xx is accessible as a slave using the I<sup>2</sup>C interface. The device is operating using the 12 MHz RC HF Oscillator as clock source. To avoid programming failures all PROGRAMMING Mode commands are protected by a 16 bit CRC at the end of each command. The checksum has to be calculated over all bytes in the command excluding the PMA71xx/PMA51xx I2C device address. For the calculation of the CRC checksum the CCITT polynomial 1021<sub>H</sub> (x<sup>16</sup>+x<sup>12</sup>+x<sup>5</sup>+1) and the 16 bit start value FFFF<sub>H</sub> have to be used.

Figure 5 shows the nomenclature used for the description of the I<sup>2</sup>C commands.

from programmer to PMA

S start condition

From PMA to programmer

P stop condition

CRCH MSB of CRC checksum SR restart condition or stop / start condition

CRCL LSB of CRC checksum A acknowledge

Data 0-31 data which is written into / read from FLASH nA not acknowledge

Pause Time where no communication is allowed Sector selection of the sector

Status Status byte

Figure 5 Nomenclature for I<sup>2</sup>C communication

#### 3.1 FLASH Write Line

The FLASH Write Line command writes 32 bytes to the FLASH. The FLASH Code Sector and FLASH User Data Sectors can be written using this command. The start address has to be a multiple of  $20_{\rm H}$ . As shown in Figure 4 FLASH address range  $4000_{\rm H}$  to  $587F_{\rm H}$  is accessible.

This command should only be used if the FLASH line is fully erased. If an already programmed FLASH line gets overwritten (without being erased first) the resulting data is undefined. After the stop condition (P) is received the data is programmed into the FLASH. During the programming time incoming I<sup>2</sup>C commands are not acknowledged. Programming time is specified in [1]. Figure 6 shows the structure of the FLASH Write Line command. A read back verification of the written line is executed within each FLASH Write Line instruction. However, in order to see if this write command was successful, a Read Status command must be issued, or a FLASH Read Line command may be used to read back the stored values.

#### Note:

- 1. If transferring the start address, the lower 5 bits are cleared automatically.

- 2. If less than 36 data bytes are received, nothing is written into the FLASH. The Read Status command can be used to check an invalid command length error.

- 3. If an already written section in the FLASH gets re-written (without being erased before), the resulting data is undefined.

- 4. After the stop condition (P) is received the data is programmed into the FLASH. During the programming time incoming \(^{\rho}\)C commands are not acknowledged.

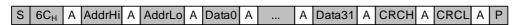

Figure 6 FLASH Write Line command

#### 3.2 FLASH Read Line

The contents of the FLASH memory (4000<sub>H</sub> to 587F<sub>H</sub>) can be read out via the I<sup>2</sup>C interface. **Figure 7** shows the structure of the FLASH read line command.

Figure 7 FLASH Read Line command

#### 3.3 FLASH Erase

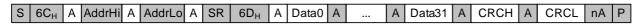

The FLASH Erase command is show in **Figure 8** and can be used to erase the Code Sector and the User Data Sectors. The FLASH Erase time is specified in [1]. **Figure 9** and **Table 2** describe the bits of the Sector byte.

Note: After the stop condition (P) is received the selected FLASH sectors are being erased. During the erase time incoming  $f^2C$  commands are not acknowledged.

Figure 8 FLASH Erase command

Figure 9 FLASH Erase: Sector byte

Table 2 FLASH Erase: Sector byte

| Bits | Field    | Description                                                                                                   |

|------|----------|---------------------------------------------------------------------------------------------------------------|

| 2    | UDSec II | 0 <sub>B</sub> : don't check User Data Sector II 1 <sub>B</sub> : check whether User Data Sector II is erased |

| 1    | UDSec I  | 0 <sub>B</sub> : don't check User Data Sector I 1 <sub>B</sub> : check whether User Data Sector I is erased   |

| 0    | CSec     | 0 <sub>B</sub> : don't check Code Sector<br>1 <sub>B</sub> : check whether Code Sector is erased              |

#### 3.4 FLASH Check Erase Status

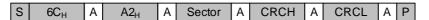

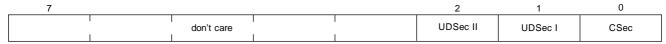

This function returns the status of the selected FLASH sector(s). The time required for checking the sectors depends on the selected sectors. The structure of the I<sup>2</sup>C command *Flash Check Erase Status* is shown in **Figure 10**. **Figure 11** and **Table 3** describe the bits of the Sector byte. The Status byte is illustrated in **Figure 12** and **Table 4**.

Note: After the first stop condition (P) is received the selected FLASH sectors are checked. During this time incoming  $f^2C$  commands are not acknowledged.

Figure 10 FLASH Check Erase Status command

| 7 |            |   |   | 2        | 1       | 0    |

|---|------------|---|---|----------|---------|------|

|   | don't care |   |   | UDSec II | UDSec I | CSec |

| 1 | 1          | 1 | 1 |          |         |      |

Figure 11 FLASH Check Erase Status: Sector byte

Table 3 FLASH Check Erase Status: Sector byte

| Bits | Field    | Description                                                                                                      |

|------|----------|------------------------------------------------------------------------------------------------------------------|

| 2    | UDSec II | 0 <sub>B</sub> : don't check User Data Sector II<br>1 <sub>B</sub> : check whether User Data Sector II is erased |

| 1    | UDSec I  | 0 <sub>B</sub> : don't check User Data Sector I 1 <sub>B</sub> : check whether User Data Sector I is erased      |

| 0    | CSec     | 0 <sub>B</sub> : don't check Code Sector<br>1 <sub>B</sub> : check whether Code Sector is erased                 |

I2C\_FLASHCheckEraseStatusByte.vsd

Figure 12 FLASH Check Erase Status: Status byte

Table 4 FLASH Check Erase Status: Status byte

| Bits | Field    | Description                                                                                                                   |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 2    | UDSec II | 0 <sub>B</sub> : User Data Sector II is erased or untested<br>1 <sub>B</sub> : at least one bit is set in User Data Sector II |

| 1    | UDSec I  | 0 <sub>B</sub> : User Data Sector I is erased or untested 1 <sub>B</sub> : at least one bit is set in User Data Sector I      |

| 0    | CSec     | 0 <sub>B</sub> : Code Sector is erased or untested<br>1 <sub>B</sub> : at least one bit is set in Code Sector                 |

## 3.5 FLASH Set Code Lock (Lockbyte 2)

To set Lockbyte 2  $D1_H$  has to be written to FLASH address 577 $F_H$  (top address of Code Sector). After the Lockbyte 2 is set, a startup in DEBUG or PROGRAMMING Mode is not possible any more.

Note: To activate the Code Sector Lock the PMA71xx/PMA51xx has to be reset after Lockbyte D1<sub>H</sub> has been set.

### 3.6 FLASH Set User Data Sector Lock (Lockbyte 3)

This command sets the Lockbyte for FLASH User Data Sectors I + II.

Note: It is required to set Code Sector Lock (Lockbyte 2) to enable User Data Sector Lock to become effective.

Note: To activate the User Data Sector Lock (Lockbyte 3) the PMA71xx/PMA51xx has to be reset after setting the Lockbyte for User Data Sector and Code Sector.

Figure 13 FLASH Set Lockbyte 3 command

#### 3.7 Read Status

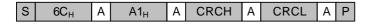

This function is intended to read out the status of the previous executed functions (pass/fail). It can be called whenever desired to verify if there were errors since the last *Read status* call. **Figure 15** and **Table 5** describe the bits of the Status byte.

13

Figure 15 Read Status: Status byte

#### Programming sequence for PMA71xx/PMA51xx code sector

Table 5 Read Status: Status byte

| Bits | Field                                                                                                                                                                                                                             | Description                                                                                                                                                                      |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:4  | CmdCnt  Number of executed commands since the first detected error.  1111 <sub>B</sub> : 15 commands or more  1110 <sub>B</sub> : 14 commands   0001 <sub>B</sub> : 1 command  0000 <sub>B</sub> : error occurred in last command |                                                                                                                                                                                  |  |  |  |

| 3:2  | ErrCnt                                                                                                                                                                                                                            | Erroneous events since the last Read status call.  11 <sub>B</sub> : three or more errors  10 <sub>B</sub> : two errors  01 <sub>B</sub> : one error  00 <sub>B</sub> : no error |  |  |  |

| 1    | InvCmdL                                                                                                                                                                                                                           | 1 <sub>B</sub> : Invalid command length or execution fail since the last Read status call 0 <sub>B</sub> : Command length and execution correct since the last Read status call  |  |  |  |

| 0    | CRCFail                                                                                                                                                                                                                           | 1 <sub>B</sub> : CRC Failure detected since the last Read status call 0 <sub>B</sub> : no CRC Error occurred since the last Read status call                                     |  |  |  |

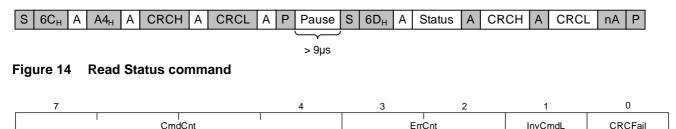

## 4 Programming sequence for PMA71xx/PMA51xx code sector

Figure 16 shows a possible sequence to program the PMA71xx/PMA51xx code sector. First of all the PMA71xx/PMA51xx has to be set into PROGRAMMING Mode by setting PP0 to 0<sub>B</sub>, PP1 to 1<sub>B</sub> and MSE to 1<sub>B</sub> during reset. The MSE, PP0 and PP1 levels must not change after reset release during the whole t<sub>MODE</sub> period (see [1]). Before writing data to the code sector the sector has to be erased by using the I<sup>2</sup>C command *FLASH Erase*. When the sector is erased, which can be checked with I<sup>2</sup>C command *FLASH Check Erase Status*, data can be written line by line (32 bits by 32 bits) into the code sector by calling the I<sup>2</sup>C command *FLASH Write Line*. Verification of the data can be done by reading out the currently written sector line by line with the I<sup>2</sup>C command *FLASH Read Line*. When the code sector is written a CRC checksum has to be calculated over the whole code sector. The low byte of the CRC checksum has to be stored to 577E<sub>H</sub> and the high byte to 577D<sub>H</sub>. To protect the code sector against undesired read outs this sector can be locked by writing D1<sub>H</sub> to FLASH address 577F<sub>H</sub> (Code Lock). After setting the Code Lock the PROGRAMMING and DEBUG Mode can not be entered again. The PMA71xx/PMA51xx can be set into the NORMAL Mode by setting MSE to 0<sub>B</sub> and resetting the chip.

#### Programming sequence for PMA71xx/PMA51xx code sector

Figure 16 Possible programming sequence for PMA71xx/PMA51xx code sector

## 5 Estimation of device programming time

Due to the fact that the programming time is an important cost factor some estimations of the device programming time are done in this chapter. Chapter 5.1 shows an estimation of the transaction times of every FLASH command. In Chapter 5.2 and Chapter 5.3 two programming scenarios are described.

#### 5.1 FLASH command transaction times

The transaction time for each PROGRAMMING Mode command is calculated and summarized in **Table 7** to **Table 12**. The timing values of  $t_{POR}$  (Power On Reset time),  $t_{MODE}$  (Mode selection time),  $t_{PROGRAM}$  (FLASH write time per line) and  $t_{ERASE}$  (FLASH erase time) are assumptions. For specified values refer to [1].

Table 6 Assumptions for the calculation of FLASH command transaction times

| Parameter                 | assumed value           |  |  |

|---------------------------|-------------------------|--|--|

| $t_{POR}$                 | 10 ms                   |  |  |

| t <sub>MODE</sub>         | 2.5 ms                  |  |  |

| t <sub>PROGRAM</sub>      | 2.2 ms                  |  |  |

| t <sub>ERASE</sub>        | 102 ms                  |  |  |

| I <sup>2</sup> C datarate | 400 kbit/s              |  |  |

| FLASH lines               | 188 (with 32 byte each) |  |  |

Table 7 FLASH Check Erase Status

| Nomenclature                          | Units | Bits / Unit | Bits total |  |  |

|---------------------------------------|-------|-------------|------------|--|--|

| S                                     | 2     | 1           | 2          |  |  |

| Bytes                                 | 9     | 8           | 72         |  |  |

| A                                     | 8     | 1           | 8          |  |  |

| nA                                    | 1     | 1           | 1          |  |  |

| Р                                     | 2     | 1           | 2          |  |  |

| Total bits per command                |       |             | 85         |  |  |

| Total time per command [ms]           |       |             | 0.2125     |  |  |

| Pause [ms]                            |       |             |            |  |  |

| Total time per operation [ms] 35.2125 |       |             |            |  |  |

Table 8 FLASH Erase

| Nomenclature                  | Units | Bits / Unit | Bits total |

|-------------------------------|-------|-------------|------------|

| S                             | 1     | 1           | 1          |

| Bytes                         | 5     | 8           | 40         |

| A                             | 5     | 1           | 5          |

| Р                             | 1     | 1           | 1          |

| Total bits per command        |       |             | 47         |

|                               |       |             |            |

| Total time per command [ms]   |       |             | 0.1175     |

| t <sub>ERASE</sub> [ms]       |       |             | 102        |

| Total time per operation [ms] |       |             | 102.1175   |

Table 9 FLASH Write Line

| Table 9 FLASH Write Line      |       |             |            |

|-------------------------------|-------|-------------|------------|

| Nomenclature                  | Units | Bits / Unit | Bits total |

| S                             | 1     | 1           | 1          |

| Bytes                         | 37    | 8           | 296        |

| A                             | 37    | 1           | 37         |

| Р                             | 1     | 1           | 1          |

| Total bits per command        |       |             | 335        |

| Total time per command [ms]   |       |             | 0.8375     |

| t <sub>PROGRAM</sub> [ms]     |       |             | 2.2        |

| Total time per operation [ms] | ·     |             | 3.0375     |

### Table 10 FLASH Read Line

| Nomenclature                  | Units | Bits / Unit | Bits total |

|-------------------------------|-------|-------------|------------|

| S                             | 1     | 1           | 1          |

| SR                            | 1     | 1           | 1          |

| Bytes                         | 38    | 8           | 304        |

| A                             | 37    | 1           | 37         |

| nA                            | 1     | 1           | 1          |

| Р                             | 1     | 1           | 1          |

| Total bits per command        |       |             | 345        |

| Total time per command [ms]   |       |             | 0.8625     |

| Total time per operation [ms] |       |             | 0.8625     |

Table 11 **FLASH Read Status**

| Nomenclature                  | Units | Bits / Unit | Bits total |

|-------------------------------|-------|-------------|------------|

| S                             | 2     | 1           | 2          |

| Bytes                         | 8     | 8           | 64         |

| A                             | 7     | 1           | 7          |

| nA                            | 1     | 1           | 1          |

| Р                             | 2     | 1           | 2          |

| Total bits per command        |       |             | 76         |

|                               |       |             |            |

| Total time per command [ms]   |       |             | 0.19       |

| Pause [ms]                    |       |             | 0.009      |

| Total time per operation [ms] |       |             | 0.199      |

Table 12 FLASH Set User Data Sector Lock

| Nomenclature                  | Units | Bits / Unit | Bits total |

|-------------------------------|-------|-------------|------------|

| S                             | 1     | 1           | 1          |

| Bytes                         | 4     | 8           | 32         |

| A                             | 4     | 1           | 4          |

| Р                             | 1     | 1           | 1          |

| Total bits per command        |       |             | 38         |

|                               |       |             |            |

| Total time per command [ms]   |       |             | 0.095      |

| Total time per operation [ms] |       |             | 0.095      |

|                               |       |             |            |

#### 5.2 FLASH programming scenario 1

FLASH programming scenario 1 is optimized for throughput (speed), and assumes that I<sup>2</sup>C and bus errors are occurring only very rarely and that a simple status check of FLASH write operations is sufficient to ensure integrity. There are a maximum of 188 FLASH lines that must be programmed, and a FLASH Read Status command is performed after every 8 FLASH lines are written (i.e. for every 256 bytes of programmed FLASH). The total device programming time, including power on reset, mode selection, and all necessary I<sup>2</sup>C transactions, can be estimated as shown in Table 13.

Note: The FLASH Code sector is locked with the last FLASH Write Line command by writing the Lockbyte D1<sub>H</sub> to 577F<sub>H</sub>.

Table 13 Programming time estimation with status verification every 256 bytes

|                             | Units [ms] | Unit | Total time [ms] |

|-----------------------------|------------|------|-----------------|

| t <sub>POR</sub>            | 10         | 1    | 10              |

| t <sub>MODE</sub>           | 2.5        | 1    | 2.5             |

| FLASH Erase Status          | 35.2125    | 1    | 35.2125         |

| FLASH Write Line            | 3.0375     | 188  | 571.05          |

| FLASH Check Status          | 0.199      | 24   | 4.776           |

| FLASH Set Code Lock         | 0          | 0    | 0               |

| Total time for 6 kbyte [ms] | ,          |      | 623.5385        |

#### 5.3 FLASH programming scenario 2

FLASH programming scenario 2 is less optimistic than the first, and assumes that I<sup>2</sup>C bus errors are more likely to occur. There are a maximum of 188 FLASH lines that must be programmed, and a FLASH Read Line command is performed after every FLASH line is written to allow write verification of each byte. The total device programming time, including power on reset, mode selection, and all necessary I<sup>2</sup>C transactions, can be estimated as shown in Table 14.

Note: The FLASH Code sector is locked with the last FLASH Write Line command by writing the Lockbyte D1<sub>H</sub> to 577F<sub>H</sub>.

Table 14 Programming time estimation with verification of each byte

|                             | Units [ms] | Unit | Total time [ms] |

|-----------------------------|------------|------|-----------------|

| t <sub>POR</sub>            | 10         | 1    | 10              |

| t <sub>MODE</sub>           | 2.5        | 1    | 2.5             |

| FLASH Erase Status          | 35.2125    | 1    | 35.2125         |

| FLASH Write Line            | 3.0375     | 188  | 571.05          |

| FLASH Read Line             | 0.8625     | 188  | 162.15          |

| FLASH Set Code Lock         | 0          | 0    | 0               |

| Total time for 6 kbyte [ms] |            |      | 780.9125        |

Application example (PMA Starterkit as programmer)

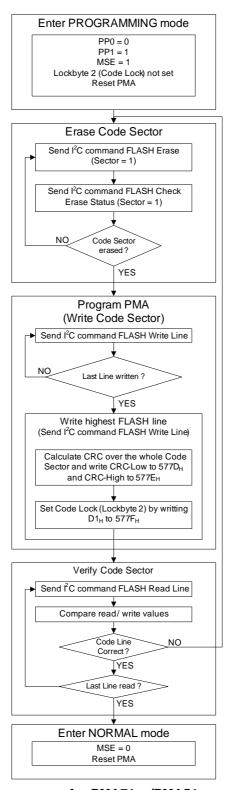

# 6 Application example (PMA Starterkit as programmer)

**Figure 17** shows how the PMA Starterkit can be used as programmer for a PMA on a customer circuit. For the communication between the PMA on the Starterkit and the KEIL<sup>TM</sup> driver on the PC an FTDI chip is used. The PMA on the Starterkit interacts with the FTDI via the I<sup>2</sup>C unit. The PMA on the customer circuit is programmed by the PMA on the Starterkit. Therefore the PMA on the Starterkit uses a software implementation of the I<sup>2</sup>C and the GPIOs PP2, PP3, PP4 and PP5. The PMA on the customer circuit uses the I<sup>2</sup>C unit.

The KEIL driver software for the PMA Starterkit and a User Guide which shows how to use the PMA Starterkit as a programmer can be downloaded from <a href="http://www.infineon.com/PMA\_Starterkit">http://www.infineon.com/PMA\_Starterkit</a>.

Figure 17 Usage of PMA Starterkit as programmer

References

# References

[1] PMA71xx/PMA51xx Data Sheet

www.infineon.com