# Design Tips

## モノリシック高耐圧ゲート・ドライバ

A. Merello、A. Rugginenti、M. Grasso著

### 目次

|                                               |    |

|-----------------------------------------------|----|

| はじめに .....                                    | 1  |

| ブートストラップ回路 .....                              | 2  |

| ブートストラップ・コンデンサの容量の決定 .....                    | 2  |

| ブートストラップ回路に関する考察 .....                        | 4  |

| ゲート抵抗 .....                                   | 5  |

| ターン・オン時のゲート抵抗の値 .....                         | 5  |

| スイッチング時間 .....                                | 5  |

| 出力電圧変化率 .....                                 | 6  |

| ターン・オフ時のゲート抵抗の値 .....                         | 7  |

| 寄生要素の効果 .....                                 | 8  |

| COM電位がグラウンド以下になる場合 ( $V_{ss}$ -COM) .....     | 9  |

| $V_s$ 電位がグラウンド以下になる場合 ( $V_s$ -COM/VSS) ..... | 12 |

| $V_s$ と $V_{out}$ 間の抵抗 .....                  | 13 |

| $V_s$ 用クランプ・ダイオード .....                       | 15 |

| PCBレイアウトのアドバイス .....                          | 16 |

| 高電圧部と低電圧部を遠ざける .....                          | 16 |

| 接地面 .....                                     | 16 |

| 電源コンデンサ .....                                 | 16 |

| ゲート駆動ループ .....                                | 16 |

| ルーティングおよび配置例 .....                            | 17 |

### はじめに

本書の目的は、モーター駆動アプリケーション（モノリシックIC ゲート・ドライバを使用）でのハーフ・ブリッジ・パワー段の駆動における最も一般的な問題を取り上げ、その問題に対する適切な解決法を提案することです。

以降の章では、ブートストラップ回路やオン／オフ・ゲート抵抗などの基本素子の値の決定について説明し、ハーフ・ブリッジ寄生要素の影響と、考えられる解決法について提案します。さらに、最後の章ではレイアウトについていくつかのアドバイスを紹介します。

提示されている状況および解決法はすべて、特に断りのない限り、フローティング・ブートストラップ電源を使用した標準的なIRモノリシック・ゲート・ドライバを対象としています。

## ブートストラップ回路

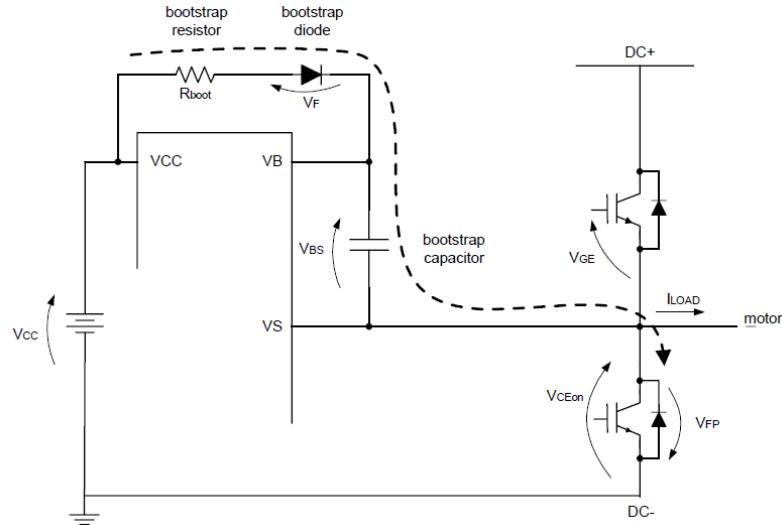

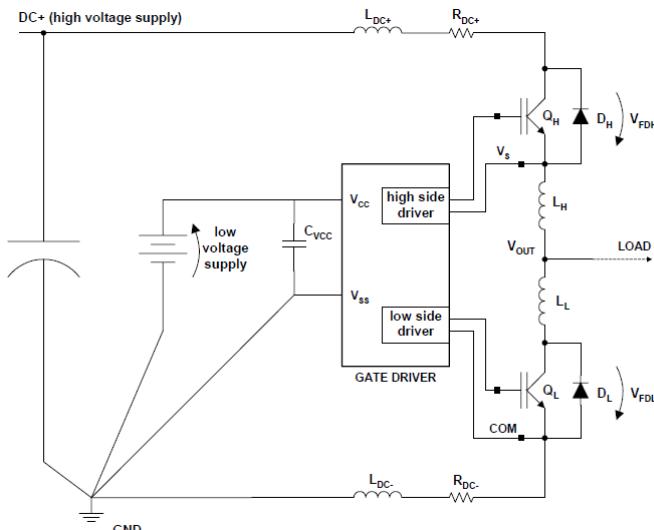

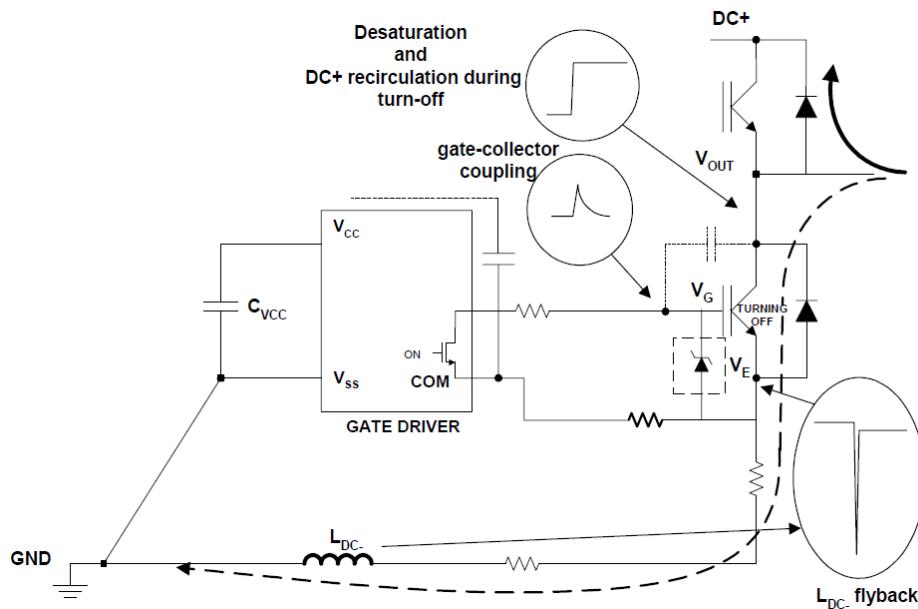

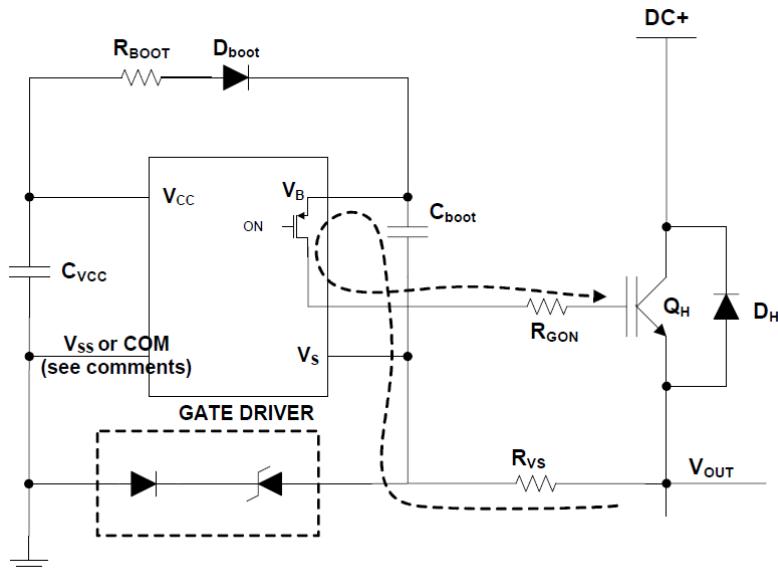

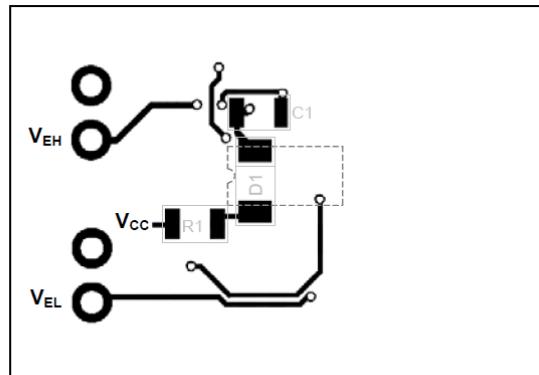

ブートストラップ電源は、図1のように接続されたダイオードとコンデンサで構成されます。

図1: ブートストラップ電源回路図

この方法には、簡単で低コストであるという利点がありますが、ブートストラップ・コンデンサを充電する必要があるので、デューティ・サイクルとオンタイムが制限される可能性があります。

これらの制限は、適切なコンデンサを選択することでほとんど解消できます。

## ブートストラップ・コンデンサの容量の決定

ブートストラップ・コンデンサの容量を決定するために、まずハイサイドIGBTがオンの場合に保証する必要がある最小電圧降下 ( $\Delta V_{BS}$ ) を設定します。

$V_{Gmin}$ を、維持する最小ゲート・エミッタ間電圧とすると、電圧降下は以下の式を満足しなければなりません。

$$\Delta V_{BS} \leq V_{CC} - V_F - V_{GE\min} - V_{CEon}$$

ただし、以下の条件が成立しているものとします。

$$V_{GE\min} > V_{BSUV-}$$

ここで、 $V_{CC}$  はIC電源電圧、 $V_F$  はブートストラップ・ダイオード順電圧、 $V_{CEon}$  はローサイドIGBTのコレクタ・エミッタ間電圧、 $V_{BSUV-}$  はハイサイド減電圧保護回路（立下り）のしきい値です。

次に、 $V_{BS}$ の減少に寄与する要因について考慮する必要があります。

- IGBTをターン・オンするために必要なゲート電荷 ( $Q_G$ )

- IGBTゲート・ソース間漏れ電流 ( $I_{LK\_GE}$ )

- フローティング部の静止電流 ( $I_{QBS}$ )

- フローティング部の漏れ電流 ( $I_{LK}$ )

- ブートストラップ・ダイオード漏れ電流 ( $I_{LK\_DIODE}$ )

- オン時飽和ダイオード・バイアス ( $I_{DS-}$ )

- IC内部のレベル・シフトに必要な電荷 ( $Q_{LS}$ )

- ブートストラップ・コンデンサ漏れ電流 ( $I_{LK\_CAP}$ )

- ハイサイド・オンタイム ( $T_{HON}$ )

$I_{LK\_CAP}$  は、電解コンデンサを使用する場合にのみ関係し、他のタイプのコンデンサを使用する場合は無視できます。少なくとも1つの低ESRセラミック・コンデンサを使用することを強くお勧めします（電解コンデンサと低ESRセラミック・コンデンサを並列接続して使用すると、効率が良くなることがあります）。

次式が得られます。

$$Q_{TOT} = Q_G + Q_{LS} + (I_{LK\_GE} + I_{QBS} + I_{LK} + I_{LK\_DIODE} + I_{LK\_CAP} + I_{DS-}) \cdot T_{HON}$$

最小のブートストラップ・コンデンサの値は：

$$C_{BOOT\ min} = \frac{Q_{TOT}}{\Delta V_{BS}}$$

以下に例を示します

a) 25A @ 125°C IGBT (IRGP30B120KD) および高耐圧ハーフ・ブリッジ・ゲート・ドライバ (IR2214) を使用：

- $I_{QBS} = 800\mu\text{A}$  (データシート IR2214)

- $I_{LK} = 50\mu\text{A}$  (データシート IR2214)

- $Q_{LS} = 20\text{nC}$

- $Q_G = 160\text{nC}$  (データシート IRGP30B120KD)

- $I_{LK\_GE} = 100\text{nA}$  (データシート IRGP30B120KD)

- $I_{LK\_DIODE} = 100\mu\text{A}$  (逆回復時間 < 100ns)

- $I_{LK\_CAP} = 0$  (セラミック・コンデンサの場合は無視できる)

- $I_{DS-} = 150\mu\text{A}$  (データシート IR2214)

- $T_{HON} = 100\mu\text{s}$

および

- $V_{CC} = 15\text{V}$

- $V_F = 1\text{V}$

- $V_{CEonmax} = 3.1\text{V}$

- $V_{GEmin} = 10.5\text{V}$

$\Delta V_{BS}$  の最大電圧低下は、

$$\Delta V_{BS} \leq V_{CC} - V_F - V_{GEmin} - V_{CEon} = 15\text{V} - 1\text{V} - 10.5\text{V} - 3.1\text{V} = 0.4\text{V}$$

およびブートストラップ・コンデンサの値は：

$$C_{BOOT} \geq \frac{290\text{nC}}{0.4\text{V}} = 725\text{nF}$$

注：

1. ここで、上の例では  $V_{CC}$  を 15V にしています。一部のIGBTで、ブートストラップ方式で正しく実施するには、より高い電圧が必要な場合があります。また、 $V_{CC}$  の変動は、上の式の範囲内にある必要があります。

2. このようなブートストラップの値を決める方法は、PWMのデューティ・サイクルや電流の基本周波数を考慮しません。ドライバの高電圧側がフローティングしており、IGBTゲートが一度駆動された場合に必要な充電量のみを考慮します。

- ブートストラップ回路の最良の値を決定するには、PWMデューティ・サイクル、変調の種類（6段階、12段階、正弦波）に関する考察を独自の特性とともに考慮する必要があります。

## ブートストラップ回路に関する考察

### a. 電圧リップル

ブートストラップ・コンデンサの充電では、以下の3つの異なる状況が発生する可能性があります（図1参照）。

-  $I_{LOAD} < 0$  :  $V_{CEon}$  を表示しているローサイドIGBTで負荷電流が流れる

$$V_{BS} = V_{CC} - V_F - V_{CEon}$$

この場合は、 $V_{BS}$  の値が最小になります。これは、ブートストラップ・コンデンサの値では、最悪のケースです。IGBTがターン・オフされた時に、ハイサイド・フリーホイール・ダイオードが順方向バイアスされるまで、 $V_s$  部が負荷電流によって上昇します。

-  $I_{LOAD} = 0$  : オン中にIGBTに負荷がかからず、 $V_{CE}$  を無視できる

$$V_{BS} = V_{CC} - V_F$$

-  $I_{LOAD} > 0$  : 負荷電流がフリーホイール・ダイオードを流れる

$$V_{BS} = V_{CC} - V_F + V_{FP}$$

この場合は、 $V_{BS}$  の値が最大になります。ハイサイドIGBTをターン・オンすると、 $I_{LOAD}$  がそれを流れ、 $V_s$  が上昇します。

減電圧のリスクを最小限に抑えるには、 $I_{LOAD} < 0$  の場合に応じてブートストラップ・コンデンサの値を決定する必要があります。

### b. ブートストラップ抵抗

抵抗 ( $R_{boot}$ ) は、ブートストラップ・ダイオードと直列に接続されるため（図1参照）、ブートストラップ・コンデンサが初めて充電される場合、電流を制限します。ブートストラップ抵抗値の選定は、 $V_{BS}$  の時定数に厳密に関係します。ブートストラップ・コンデンサの充電または充電のリフレッシュの最小オンタイムは、この時定数に対して検証する必要があります。

### c. ブートストラップ・コンデンサ

高  $T_{HON}$  設計時に使用する電解コンデンサは、そのESRを考慮する必要があります。この寄生抵抗は、ブートストラップ・コンデンサの最初の充電時に  $R_{boot}$  と分割抵抗となり、 $V_{BS}$  が階段状になります。電圧が階段状になると、電圧上昇率 ( $dV_{BS}/dt$ ) を制限する必要があります。一般に、ESRは以下の制約を満たす必要があります。

$$\frac{ESR}{ESR + R_{BOOT}} \cdot V_{CC} \leq 3 V$$

通常、小さいセラミック・コンデンサと大きな電解コンデンサの並列の組み合わせが最良の妥協案です。最初のコンデンサがゲート充電のみの高速充電タスクとして動作し、等価抵抗を削減することで  $dV_{BS}/dt$  を制限し、2番目のコンデンサが目的の  $\Delta V_{BS}$  内で  $V_{BS}$  の値を保ちます。

### d. ブートストラップ・ダイオード

ブートストラップ・コンデンサから $V_{CC}$ 電源にフィード・バックされる充電量を最小限に抑えるために、ダイオードの耐圧 $BV$ は、 $BV > DC+$ という条件と高速逆回復時間 ( $t_{rr} < 100\text{ns}$ ) が必要です。

## ゲート抵抗

出力トランジスタのスイッチング速度は、抵抗を適切な値にすることで、ターン・オンおよびターン・オフ・ゲート電流を制御することにより制御できます。次の章では、目的のスイッチング時間と速度を得るための抵抗の値を決めるいくつかの基本的な規則を、ゲート・ドライバの等価出力抵抗 ( $p$ および $n$ チャネルのそれぞれ $R_{DRp}$ および $R_{DRn}$ ) を導入することで、説明します。

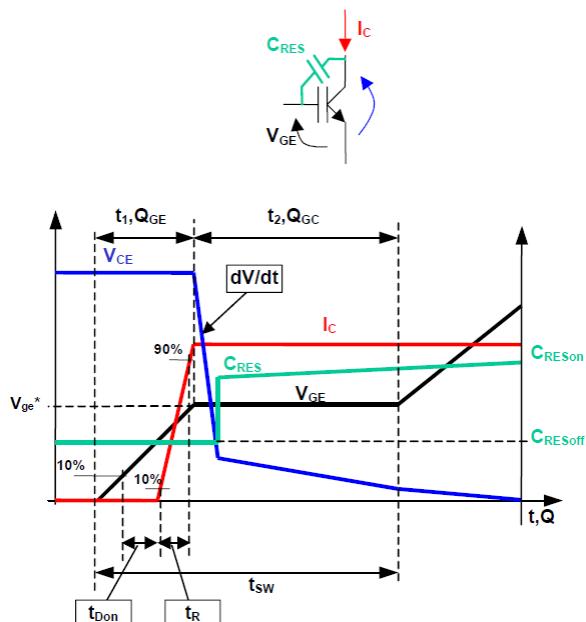

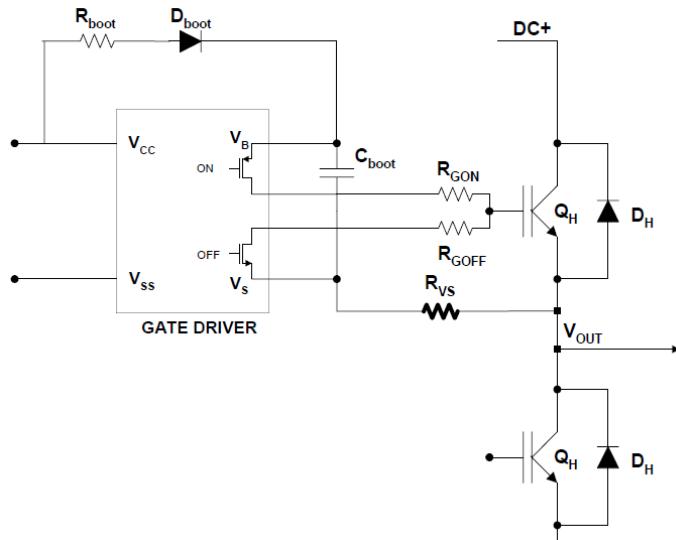

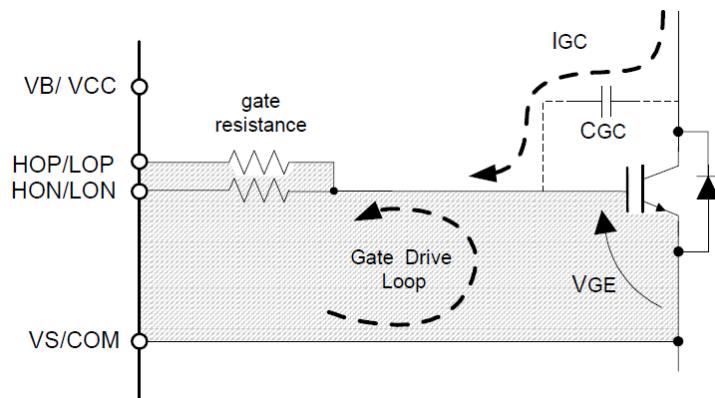

例では、常にIGBTパワー・トランジスタを使用します。図2は、次の段落で使用する用語を示します。さらに、 $V_{ge}^*$ は、 $V_{GE}$ が平坦になった電圧を示し、 $Q_{gc}$ および $Q_{ge}$ は、それぞれゲート・コレクタ電荷とゲート・エミッタ電荷を示します。

図2: 各部の名称

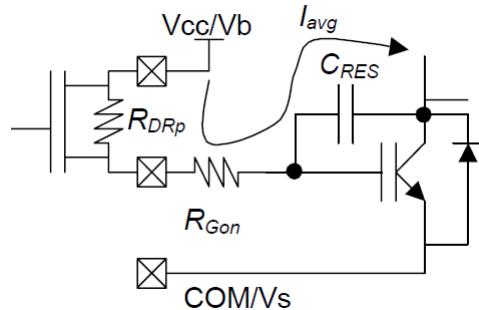

## ターン・オン時のゲート抵抗の値

ゲート抵抗は、スイッチング時間または出力電圧変化率のいずれかを固定するために選定します。以降では、両方の方法を示します。

## スイッチング時間

これ以降の計算では、スイッチング時間 $t_{sw}$ を $V_{ge}^*$ の端にするまでの時間と定義します ( $Q_{gc} + Q_{ge}$  の合計値がIGBTゲートに供給された)。目的のスイッチング時間を得るには、ゲート抵抗を $Q_{ge}$ および $Q_{gc}$ 、 $V_{cc}$ 、 $V_{ge}^*$ から始めて決定します (図3参照) :

$$I_{avg} = \frac{Q_{gc} + Q_{ge}}{t_{sw}}$$

および

$$R_{TOT} = \frac{V_{cc} - V_{ge}^*}{I_{avg}}$$

ここで、 $R_{TOT} = R_{DRp} + R_{Gon}$ 、 $R_{Gon}$  = ターン・オン時のゲート抵抗、および $R_{DRp}$  = ドライバ等価オン抵抗（ゲート・ドライバ・データシートから）

図3 :  $R_{Gon}$  の値

表1は、2つのよく使用されるIGBTのゲート抵抗値を示します（計算は、典型的なデータシート値を使用し、 $V_{cc} = 15V$ と仮定して行われた）。

### 出力電圧変化率

ターン・オン時のゲート抵抗 $R_{Gon}$  値で、出力電圧変化率（ $dV_{out}/dt$ ）を制御できます。

出力電圧の動作が非線形の間、最大出力電圧変化率は、概略以下のように計算できます。

$$\frac{dV_{out}}{dt} = \frac{I_{avg}}{C_{RESoff}}$$

$I_{avg}$  を算出する式を代入し、整理すると

$$R_{TOT} = \frac{V_{cc} - V_{ge}^*}{C_{RESoff} \cdot \frac{dV_{out}}{dt}}$$

例として、表2は、2つの一般的なIGBT、典型的なデータシート値を使用し、 $V_{cc} = 15V$  と仮定して、 $dV_{out}/dt = 5V/ns$  を得るためのゲート抵抗の値を示します。

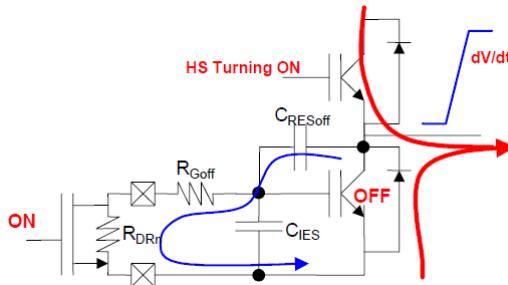

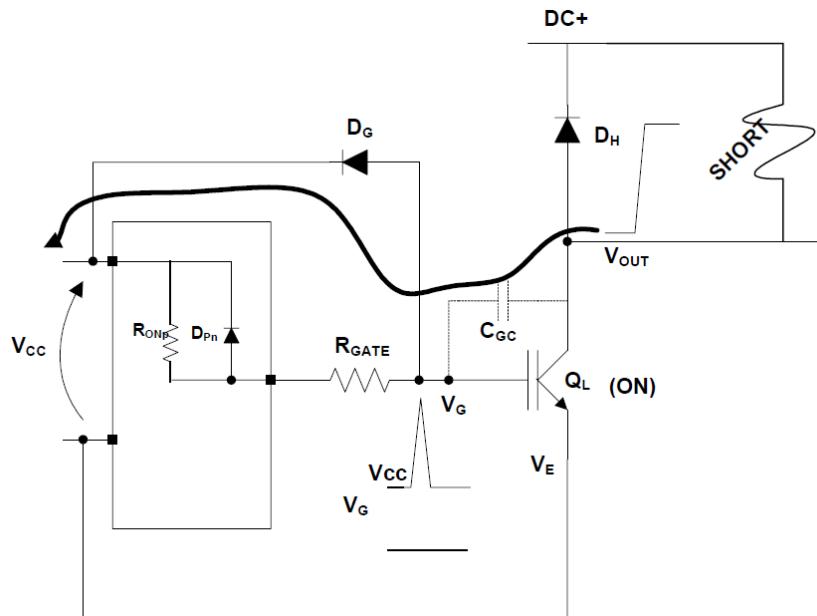

## ターン・オフ時のゲート抵抗の値

ゲート抵抗  $R_{Goff}$  の値で最悪のケースは、オフ状態のIGBTのコレクタが外部の要因により強制的に反転される場合です。

この場合、出力部の  $dV/dt$  により、 $C_{RESoff}$  から  $R_{Goff}$  および  $R_{DRn}$  に流れる寄生電流が発生します(図4 参照)<sup>1</sup>。

ゲートの電圧降下がIGBTのしきい電圧を超えると、デバイスはセルフ・ターン・オンし大きく振動しそれに関連した上下短絡が発生することがあります。

図4 :  $R_{Goff}$  の値 : ローサイドがオフでハイサイドがターン・オン時の電流経路

これ以降では、片方のIGBTのターン・オンで出力  $dV/dt$  が発生する場合に、ターン・オフ時の抵抗値を決める方法について説明します(図4参照)。

他の  $dV/dt$  が存在する場合もあり、考慮する必要があります。例としては、長いモーター・ケーブル結合で発生する  $dV/dt$  (高周波スパイク) があります。

このため、アプリケーションの最悪のケースに応じて、オフ抵抗値を正しく決める必要があります。

以下の式は、IGBTゲートしきい電圧とコレクタ  $dV/dt$  の関係です。

$$V_{th} \geq (R_{Goff} + R_{DRn}) \cdot I = (R_{Goff} + R_{DRn}) \cdot C_{RESoff} \frac{dV_{out}}{dt}$$

整理すると :

$$R_{Goff} \leq \frac{V_{th}}{C_{RESoff} \cdot \frac{dV}{dt}} - R_{DRn}$$

例として、表3では、 $dV_{out}/dt = 5V/ns$  に耐えうる2つの一般的なIGBTの  $R_{Goff}$  を示します。

注： 上で説明した式の目的は、ゲート抵抗値を決める大まかな方法を示すことです。より正確な値の決定に際しては、より正確なデバイス・モデリング、PCBおよびパワーレイアウトによる寄生コンポーネントを考慮することが必要です。

ゲート抵抗値を決める別の方法は、電力消費からの制約です。ただし、ここではこの方法の調査は行いません。

<sup>1</sup>  $dV/dt$  の間、ゲート電圧が一定だとする仮定のもとでは正しいです。  $C_{IES}$  が  $C_{RES}$  の100倍以上である場合は、この結果は常に妥当です。

表1 :  $R_{G(on)}$ の値による $t_{sw}$  ( $R_{DRp}=7\Omega$  の場合)

| IGBT           | Qge  | Qgc  | Vge* | tsw   | lavg  | Rtot | $R_{Gon} \rightarrow$ std commercial value    | Tsw    |

|----------------|------|------|------|-------|-------|------|-----------------------------------------------|--------|

| IRGP30B120K(D) | 19nC | 82nC | 9V   | 400ns | 0.25A | 24Ω  | $RTOT - RDRp = 17\Omega \rightarrow 18\Omega$ | →420ns |

| IRG4PH30K(D)   | 10nC | 20nC | 9V   | 200ns | 0.15A | 40Ω  | $RTOT - RDRp = 33\Omega \rightarrow 33\Omega$ | →200ns |

表2 :  $R_{G(on)}$ の値による $dV_{OUT}/dt$  ( $R_{DRp}=7\Omega$  の場合)

| IGBT           | Qge  | Qgc  | Vge* | CRESoft | Rtot | $R_{Gon} \rightarrow$ std commercial value    | $dV_{out}/dt$ |

|----------------|------|------|------|---------|------|-----------------------------------------------|---------------|

| IRGP30B120K(D) | 19nC | 82nC | 9V   | 85pF    | 14Ω  | $RTOT - RDRp = 7\Omega \rightarrow 8.2\Omega$ | →4.5V/ns      |

| IRG4PH30K(D)   | 10nC | 20nC | 9V   | 14pF    | 85Ω  | $RTOT - RDRp = 78\Omega \rightarrow 82\Omega$ | →5V/ns        |

表3 :  $R_{Goff}$ の値

| IGBT           | $V_{th(min)}$ | CRESoft | $R_{Goff}$               |

|----------------|---------------|---------|--------------------------|

| IRGP30B120K(D) | 4             | 85pF    | $R_{Goff} \leq 4\Omega$  |

| IRG4PH30K(D)   | 3             | 14pF    | $R_{Goff} \leq 35\Omega$ |

## 寄生要素の効果

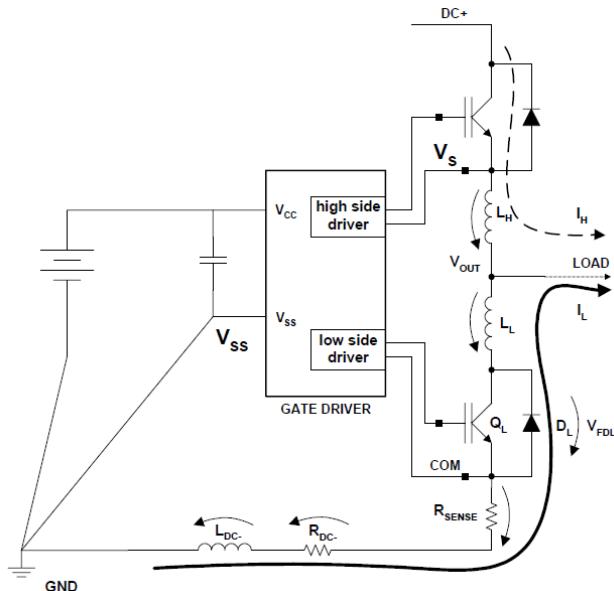

図5では、単相モーター・ドライブのパワーワンとそのドライバを示します。ドライバの特性のいくつかとパワーワンを分析します。

図5 : パワーワンの寄生要素

パワーワンを正しくドライブするには、誘導寄生要素の効果を理解していることが非常に重要です。通常動作モードでは、電流の急激な変化によって誘起される電圧の急激な変化は、ゲート・ドライバのパフォーマンスに影響する場合があります。

ロード側とハイ側の電力信号の両方が同じグランド基準の場合、基板上に接地ループがないこと、および基板のスイッチング部分の近くに接地板がないことが重要です。この解決策は、ドライバのローカル・グラウンドに結合されるノイズを削減します。さらに、すべてのゲート・ドライバの基板グラウンドとグラウンドピン間はでY結線を行うことをお勧めします（レイアウトのアドバイスを参照）。

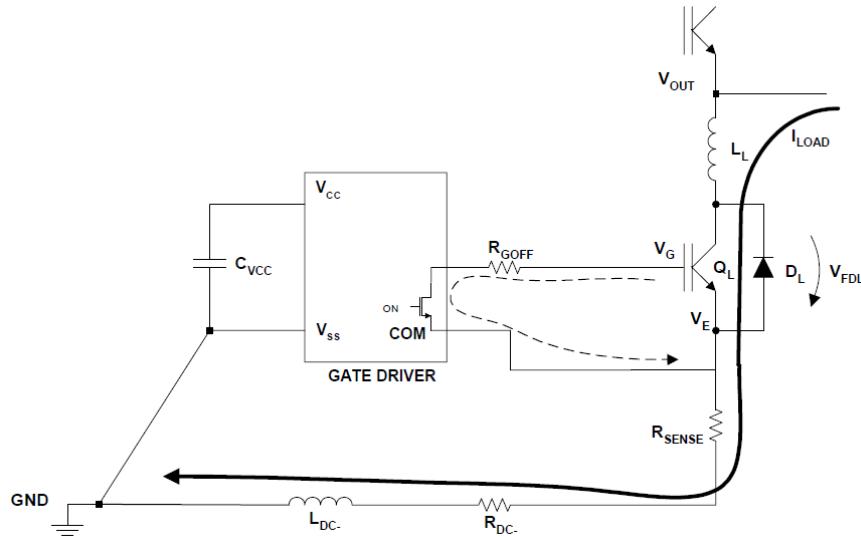

### COM電位がグラウンド以下になる場合 ( $V_{ss}$ -COM)

ローサイドIGBTは、COMが $V_{ss}$ を下回る事象の原因になると考えられます。図6は、ハーフ・ブリッジ構成での寄生要素の可能性のある配置の1つを示しています（ここで、エミッタシャント抵抗は、完璧を期すために入れています）。

図6：ローサイド・ターン・オフ時の寄生要素

負荷電流が流れているときに（太線の矢印）、ローサイドIGBTをターン・オフする場合（点線の矢印）を考えます。パワー・デバイスがターン・オフすると、寄生インダクタンス内を流れる電流（ $L_{DC-}$ ）が急激に変化し、誘起された電圧によりCOMがグラウンド以下になります。この電圧の値は、よく知られた以下の法則によって決まります。

$$V_{L_{DC-}} = L_{DC-} \cdot \frac{dI_{L_{DC-}}}{dt}$$

この式は、COMのアンダーシュート（厳密には、インダクタンス電圧によって決まる）を負荷電流の変化率に関連付けます。

このため、第一の解決策は、ローサイドのターン・オフ時のゲート抵抗を大きくすることで（上限については、ターン・オフ時ゲート抵抗の値の章を参照）、IGBTをゆるやかにターン・オフさせて、 $dI_L/dt$ を抑えることです。

この解決策は、相-DC+ 短絡が存在する場合、十分でない可能性があります。

この種の短絡は、ターン・オフしているローサイドIGBTを破壊します。ターン・オフ時に、正常動作時の定格電流を数倍上回る電流が流れ、より高速な電流の変化が誘発された場合、短絡検出が反応する場合があります。

その場合、図7に示した解決策は、 $V_{ss}$ 以下のスパイクをフィルタして、COMピンがIGBTエミッタに従うのを防ぎます。

図7:  $C_{COM}$  と  $R_{COM}$  の追加

$R_{COM}$  は、ターン・オフ時の抵抗値 ( $R_{GOFF} + R_{COM}$  の値になる) を決める際に、検討する必要があります。

$R_{COM}$  と  $C_{COM}$  の値により、数百nsのCOMピンの時定数が設定可能です。

$V_{CC}$  へのノイズ・カップリングを防ぐために、アプリケーションの必要に応じて、 $C_{COM} \neq C_{VCC} \ll 1$  という規則に従って値を決めてください。

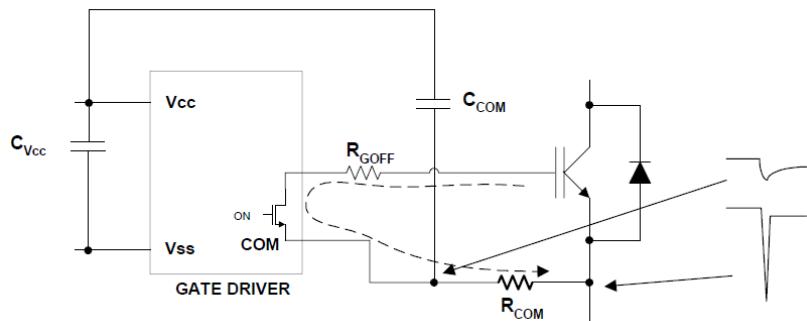

注：IGBT短絡時の過飽和は、容易に高いコレクタ  $dV/dt$  を生成します。IGBT ゲートは、ゲート-コレクタ浮遊キャパシタンスにより、電源電圧を超えて上昇します。

場合によっては（通常、ターン・オン時の抵抗値が低い場合）、ドライバ出力を保護するために、IGBTゲートと電源の間に高速ダイオードが必要です（図8）。

図8：IGBT過飽和の場合のドライバ出力保護

代替の解決策として、IGBTゲートとエミッタの間にツェナーダイオードを接続することもできます。その場合、ツェナー電圧は、IGBTゲート-エミッタ間絶対最大定格に応じて値を決定する必要があります。

ツエナーダイオードの利点は、コレクタdV/dtによって誘起された電流を吸い込み、ドライバ出力を保護できると同時に、IGBTゲート-エミッタ間電圧を制御できることにあります。

これは、特に、IGBTエミッタがDC- 寄生インダクタンス ( $L_{DC-}$ 、図9参照) が原因で  $V_{SS}$  以下になる、短絡検出後のIGBTターン・オフ時に重要です。

図9：IGBTゲート-エミッタ間ツェナー保護

## V<sub>s</sub>電位がグラウンド以下になる場合 (V<sub>s</sub>-COM/V<sub>SS</sub>)

V<sub>s</sub>電位 がV<sub>SS</sub> 電位またはCOM電位より下回る引き金となる事象としてよく知られているのは、ローサイド・フリーホール・ダイオードの順方向バイアスです。これは、通常、電流がハーフ・ブリッジから負荷へ向かって流れるときに起こります。

定常状態では、V<sub>s</sub>電位は、以下の式で示される値に近いV<sub>SS</sub>電位 以下にクランプされます。

$$V_s^{steady} - V_{SS} = -V_{FDL} - (R_{SENSE} + R_{DC-}) \cdot I_{LOAD}$$

COM電位以下の場合

$$V_s^{steady} - COM = -V_{FDL}$$

ここで、I<sub>LOAD</sub> は、負荷へ向かう正方向の電流です。

V<sub>s</sub> とV<sub>SS</sub> またはCOMとの最大電圧差は、データシートでV<sub>s</sub> の絶対最大定格と推奨動作条件でわかります。

フリーホール・ダイオードがクランプを開始する直前、転流時に大きな問題が発生する可能性があります。この場合、図10に示した誘導性寄生要素 (L<sub>dc-</sub>、L<sub>L</sub> および L<sub>H</sub>) が、前述した定常状態条件の場合以上にV<sub>s</sub> をV<sub>SS</sub> より下に押し下げる可能性があります。

以下の式の微分項は、転流過渡現象時に最も高い要因となる可能性があります。

V<sub>SS</sub> の場合

$$V_s^{tran} - V_{SS} = -V_{FDL} - (R_{SENSE} + R_{DC-}) \cdot I_L - (L_{DC-} + L_L) \cdot \frac{dI_L}{dt} - L_H \cdot \frac{dI_H}{dt}$$

COMの場合

$$V_s^{tran} - COM = -V_{FDL} - L_L \cdot \frac{dI_L}{dt} - L_H \cdot \frac{dI_H}{dt}$$

寄生インダクタンス内を流れる電流の変化率を低くして微分項を最小化するために、前述した制約 (R<sub>GOFF</sub> の値に関する章) に従い、R<sub>GOFF</sub> を大きくすることができます。

図10 :  $V_s$  を  $V_{ss}$  より下げる要素

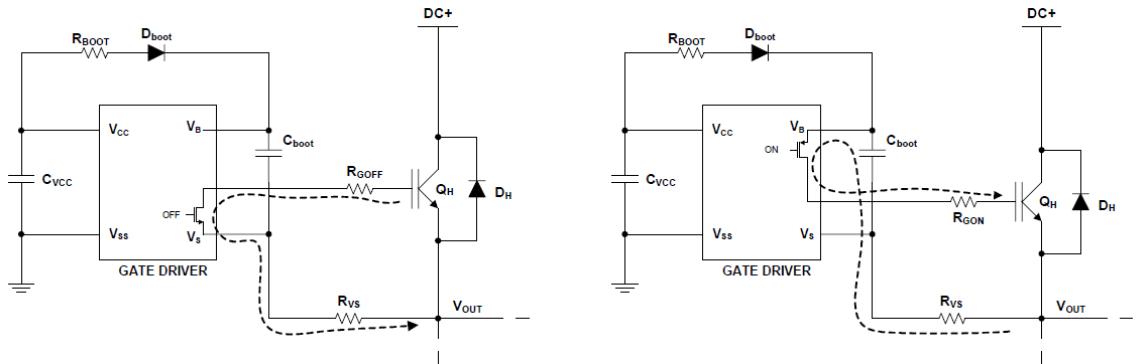

### $V_s$ と $V_{out}$ 間の抵抗

前述の解決策は、正常な動作条件ではうまくいくかもしれません、例えば、ハイサイドIGBTがオンのときに、相とグラウンド間で短絡が発生した場合などは、十分でない可能性があります。ハイサイドIGBTがターン・オフすると、そこを流れていた大きい電流がローサイド・フリー・ホイール・ダイオードを流れ始めます。

高い  $\frac{dI}{dt}$  は、ブートストラップ・コンデンサにより、VB（フローティングの電源）をグラウンド以下に下げる可能性があります。これは以下のようないくつかの原因で発生します。

$$V_s^{tran} - V_{ss} < -V_{cc}$$

ここで検討しているのは発生頻度が高い事象についてであり、そのためブートストラップ・ダイオードはターン・オフされているものとしていることに注意してください。

モノリシック IC の実際の損傷は、(CbootのVSとのカップリングを通じて) VBピンから流れ出す電流の量によって引き起こされます。この電流を最小化するために、図11に示すように、VSと  $V_{out}$  間に抵抗 ( $R_{VS}$ ) を接続することができます。

$R_{VS}$  の推奨値は、数オームの範囲です。

### 注 :

1.  $R_{VS}$  は、ブートストラップ抵抗と直列接続として機能し、ブートストラップ抵抗値を決める際に考慮を入れる必要があります ( $R_{BOOT}^* = R_{BOOT} + R_{VS}$  ) 。

2. 最初のブートストラップ・コンデンサ充電時に  $R_{VS}$  に流れる電流により、ハイサイドIGBTエミッタとVSピンの間で電流に応じた電圧が発生することにも注意する必要があります。この電圧は、HO-VS ESD保護ダイオードを通してハイサイド出力（通常、HO）に送られる場合があります。

- この場合、ブートストラップ回路の起動時にIGBTのゲートがターン・オンしないことを確認する必要があります（ゲート抵抗とゲート-エミッタ間容量は、このパルスを除去するのに役立ちます）。これにより、インバータ出力部に短いシート・スルーは発生する場合があります。

3.  $R_{VS}$  は、図12に示すように、ターン・オン時抵抗の値 ( $R_{GON} + R_{VS}$ ) およびターン・オフ時抵抗の値 ( $R_{GOFF} + R_{VS}$ ) にも関与します。

図11 :  $R_{VS}$  の接続

図12 :  $R_{VS}$  を使用したゲートのターン・オンおよびターン・オフ

## V<sub>s</sub>用クランプ・ダイオード

前段では、高頻度で発生するこのような事象について検討する際、D<sub>BOOT</sub> は電源がオフの状態を前提としていました。

V<sub>s</sub> がV<sub>OUT</sub> に応じて変化する場合で、この前提がないときはいつでも、V<sub>B</sub> はブーストアップ・ダイオードによりV<sub>CC</sub> に接続されます。この場合、V<sub>B</sub> とV<sub>s</sub> の電位差は、以下に示すように絶対最大定格以内に保たれる必要があります (ICデータシートを参照)。

$$V_B - V_s < V_{VBS\_abs\ max}$$

定格内に保つためには、図13に示すように、クランプ用のデバイスをV<sub>SS</sub> とV<sub>s</sub> の間に接続する必要があります。図では、ツエナーダイオードと600Vダイオードが接続されています。

ツエナー電圧は、以下の規則に従って値を決める必要があります。

$$V_Z \leq V_{V_B\_abs\ max} - V_{CC}$$

ほとんどの場合、ツエナーダイオードの使用は必要なく、高耐圧ダイオードだけが使用されます。

クランプは、デバイスのデータシートに従ってCOMピン (場合によってはV<sub>SS</sub> ピン) に接続する必要があります。この情報は、通常、絶対最大定格の項に記載されています。

## Absolute Maximum Ratings

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions. Additional information is shown in Figures 28 through 35.

| Symbol         | Definition                        | Min. | Max. | Units |

|----------------|-----------------------------------|------|------|-------|

| V <sub>R</sub> | High Side Floating Supply Voltage | -0.3 | 625  |       |

## Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to V<sub>s</sub>, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol         | Definition               | Min.                | Max.                 | Units |

|----------------|--------------------------|---------------------|----------------------|-------|

| V <sub>s</sub> | High side offset voltage | V <sub>R</sub> - 25 | V <sub>R</sub> + 0.3 |       |

図13：ツエナーダイオードを使用したクランプ構成

## PCBレイアウトのアドバイス

### 高電圧部と低電圧部を遠ざける

グラウンド基準の信号とフローティング信号間でのノイズ・カップリングを最小化するため、フローティング電圧に接続される部品をデバイスの高電圧側 ( $V_B$ 、 $V_S$  側) に配置し、他の部品を反対側に配置することを強くお勧めします。

### 接地面

ノイズ・カップリングを最小化するため、接地面を高電圧フローティング側の下または近くに配置しないでください。

### 電源コンデンサ

出力段が、大きい電流値でIGBTを迅速にターン・オンできる場合は、寄生インダクタンス／抵抗を最小化するため、電源コンデンサをできるだけデバイス・ピン（グラウンド接続電源の場合は $V_{CC}$  と $V_{SS}$ 、フローティング電源の場合は $V_B$  と $V_S$ ）の近くに配置する必要があります。

### ゲート駆動ループ

電流ループは、EMノイズを送受信できるアンテナのような動作をします。EMカップリングを低減させ、スイッチング素子のターン・オン／ターン・オフの性能を改善するために、ゲート駆動ループができるだけ減らす必要があります。図14は、ハイサイドおよびローサイド・ゲート・ループを示しています。

さらに、IGBTコレクタ-ゲート間寄生容量を介して、ゲート駆動ループ内に電流が注入される可能性があります。ゲート・ループの寄生インダクタンスは、ゲート-エミッタ間で電圧が生じる原因となり、セルフ・ターン・オンの可能性を増加させます。このため、ゲート抵抗を近接して配置し、ループ領域を最小化することを強くお勧めします（図14参照）。

図14: ゲート駆動ループ

### ルーティングおよび配置例

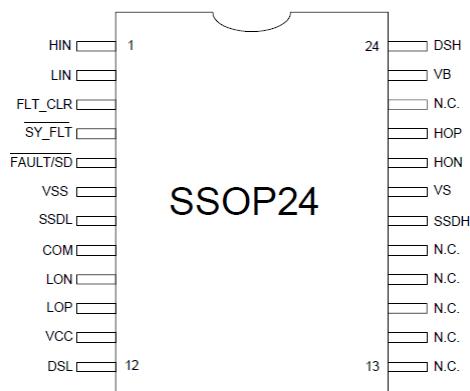

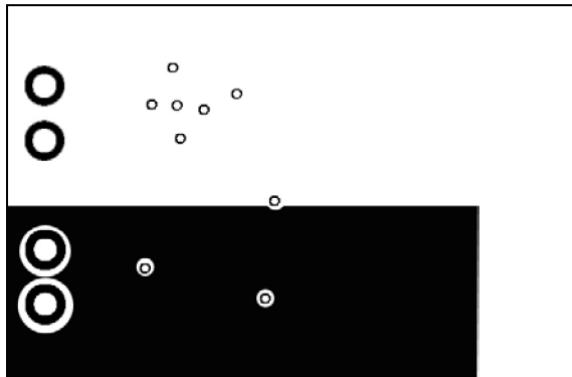

例として、高電圧、高電流出力のゲート・ドライバであるIR2214を取り上げます。図15のピン配置を参考してください。

図15 : IR2214ピン配置

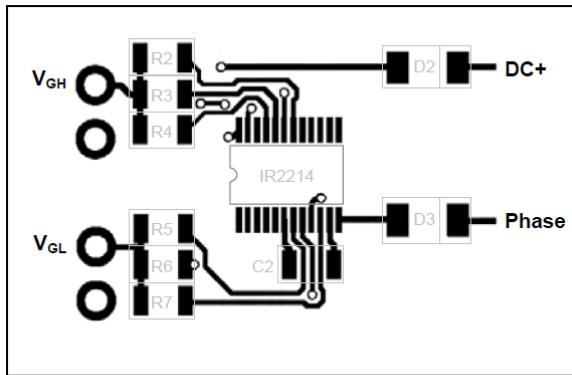

図16は、3層PCBを使用したレイアウトの1つを示しています。この例は、これまでの検討事項をすべて考慮に入れたものです。高電圧側および低電圧側における、電源コンデンサとゲート抵抗の配置およびルーティングはそれぞれ、供給経路とゲート駆動ループを最小限にしています。ブートストラップ・ダイオードはデバイスの下に配置され、カソードはブートストラップ・コンデンサにできるだけ近付け、アノードは高電圧から離し、V<sub>CC</sub>には近付けるようにしています。

図16(a)：表面

Figure 16(b) : 裏面

図16凡例

ブートストラップ部 : R1、C1、D1

ハイサイド・ゲート : R2、R3、R4

ハイサイド過飽和 : D2

ローサイド電源 : C2

ローサイド・ゲート : R5、R6、R7

ローサイド過飽和 : D3

図16(c) : 接地面