Special Report: ALTERNATE ENERGY, THE IOT, AND THE SMART GRID (pg 29)

# Designing for optimum power conversion

Driver ICs, MOSFETs, and gate drivers play key roles in SMPS and Inverter designs

By: Tobias Gerber, Infineon Technologies

oday's power conversion and power management applications demand compact yet robust power switching circuitry that supports high-voltage, high-frequency operation with the minimum of losses from the smallest possible PCB area.

By definition, the choice of MOSFET technology has a significant impact on how successfully this demand can be addressed. However, the best performance will only be achieved through carefully combining the chosen MOSFETs with all the other components in the circuit. Among the most important tasks in this facing the designer is identifying MOSFET gate driver ICs that are optimized for the target application.

### Power conversion requirements

Designing systems for modern power switching applications such as switched-mode power supplies (SMPS), DC/DC converters, industrial motor drives, and solar panel inverters that convert voltages from a

photovoltaic cell are driven by a variety of factors. There are commercial, legislative and environmental pressures to improve efficiency and drive down losses so as to reduce operational costs and minimize both energy use and harmful greenhouse gas emissions. There are end user demands for constantly improved performance without any increase in product or system size, and there is the need to build in safeguards that protect both users and critical components.

At the same time, high component densities put pressure on real estate and the need to effectively manage thermal performance, while budget constraints demand the smallest possible bill of materials (BOM) and the use of less costly components.

Finally, all of this must typically be achieved with the shortest possible time between development and final production.

It is these factors that have led to a significant growth in the

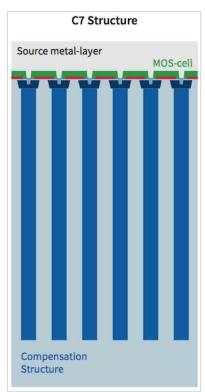

Figure 1: CoolMOS C7 Superjunction

Structure

use of high-current, high-speed switching power conversion circuits. Increased switching speeds not only contribute to improved performance and efficiency but also have the significant advantage that they allow the use of smaller and less costly inductive components for filtering. Such circuits will typically be built around

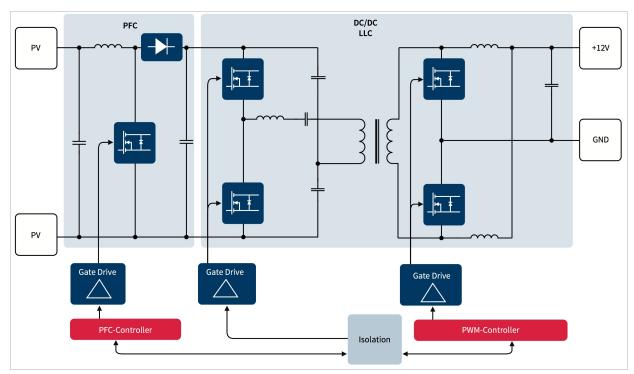

Figure 2: Power Converter Stage Based on Controller, Driver IC and SJ MOSFETs

controller or regulator ICs that provide the requisite high-frequency input signal and power MOSFETs that physically switch the load.

## **Driving superjunction MOSFETs**

Achieving the switching and efficiency performance demanded by modern power conversion applications demands highperformance MOSFETs and this typically means devices based on superjunction (SJ) semiconductor processes. This is because SJ MOSFETs employ a drain structure that supports much lower area-specific on-state resistance without compromising the requisite voltage-blocking capabilities. Together with several cell geometry considerations, SJ technology also reduces all device capacitances, thus

improving the switching-related Figures of Merit (FoM) and other application performance characteristics.

Figure 1 shows a schematic of the latest evolution of SJ technology – CoolMOS C7 – in which a seven-column, high-aspect ratio compensation structure has been deployed. The significant performance improvements that this structure offers can be seen in the latest CoolMOS C7 600V series, which are the first MOSFETs to break the  $1\Omega$  per mm2 RDS(ON)\*A limit.

There are many cases where it is not practical for the controller IC to directly drive the chosen MOSFET, not least that many controllers simply don't have a high enough output capability

for today's high-performance power devices. SJ MOSFETs, for example, typically require a gate source voltage (Vgs) of at least 8V. At the same time, high efficiency demands fast switching transients and high currents, typically in excess of 1A peak. As a result, it is neither technically (thanks largely to heat dissipation issues) or commercially viable to monolithically integrate the driver circuitry into the controller IC.

In addition, a designer may wish to mitigate potential EMI problems caused by high-speed switching by ensuring that the drive circuitry is as close to the load as possible. For these reasons, a growing number of designers are having to choose a dedicated driver IC that sits

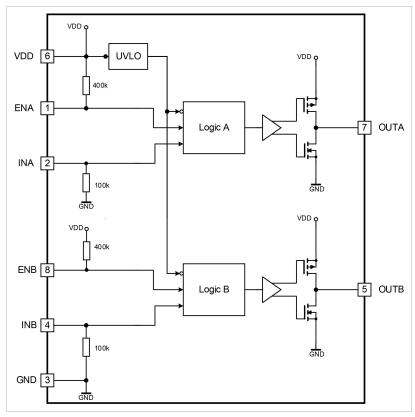

Figure 3: Block Diagram of Infineon 2EDNx52x Gate Driver ICs

between the controller and the MOSFET. Such a set-up is illustrated in **Figure 2** for a typical power conversion stage.

Criteria for the designer to consider when selecting a suitable gate driver IC technology will include current capabilities, switching speeds, form factor, level of integration (e.g. how many driver channels are available and what safety features are built in), and how well the process and package technologies are matched to the efficiency and thermal performance requirements of the target application.

**MOSFET driver IC technology**

A good example of a driver IC technology that is ideally suited to the requirements of SJ MOSFETs can be found in the form of a new series of dualchannel, high-speed, high-current devices from Infineon. Figure 3 shows a block diagram of the key functional elements of these 2EDNx52x driver ICs.

The new drivers provide two independent, non-isolated, low-side gate drivers, each offering a 5A peak source or sink current. Both channels operate with typical rise and fall times of just 5ns. Despite the high current, the output stage still offers a very low on resistance, meaning that there is very low power dissipation in

the driver even if a very small (or no) external gate resistor is used.

The high-current, high-speed performance of the 2EDNx52x family supports rapid Miller Plateau transitions (the flat, horizontal portion of a MOSFET gate charge characteristic where the voltage stays until sufficient charge has been added or removed for the device to switch), with peak current available throughout the transition. Precise timing is also ensured, which is another key criteria for high-performance, high-power-efficiency SJ-based MOSFET designs such as power factor correction (PFC) circuitry, half bridges and synchronous rectifiers.

While independent, the two driver channels have less than a 1ns channel-to-channel mismatch. As a result designers can choose to configure simultaneous switching. Such switching is particularly useful in applications where outputs are being paralleled to increase the overall drive current available.

### Ground bounce

Another issue when it comes to the design of modern high-frequency power conversion platforms is that the greater MOSFET switching speeds lead to an increased possibility of problems resulting from ground bounce. Ground bounce occurs when the MOSFET gate voltage appears to be lower than the

local ground potential, leading to current flowing through the ground network. This, in turn, can lead to the possibility of system unreliability or failure as a result of unstable operation at the control and enable inputs.

To avoid the reliability issues associated with ground bounce, devices in the 2EDNx52x series can all handle maximum voltages as low as -10V at both the input and enable control pins without operational failure. Furthermore, stability is assured even if the negative voltages exist permanently (e.g. DC conditions).

Where it is not possible to completely prevent an abnormal condition that falls outside of the tolerance of the device, a fast typical propagation delay of 19ns for both the control and enable inputs facilitates rapid emergency shutdown. It is worth noting that the propagation delay could be lower but is intentionally designed to be 19ns. This is because poor circuit layouts and other parasitics can sometimes be a cause of ringing – something that can be mitigated against with propagation delays in excess of 15ns.

The new MOSFET gate driver ICs can operate from a supply voltage of between 4.5V and 20V and feature an under voltage lockout (UVLO) function that will protect an SJ MOSFET from destructive linear mode operation. A selection of industry standard

8-pin packages allows designers to easily upgrade to the new technology without necessitating costly and time-consuming board re-design, while extended temperature operation is made possible thanks to the ability to function with junction temperatures from -40°C to 150°C.

# Looking forward

As switching speeds and currents continue to increase, integrated gate driver ICs are becoming increasingly critical components in modern power conversion applications. Careful selection of these – including pairing with a suitable SJ MOSFET technology such as the latest CoolMOS C7 600V series – can help designers to optimize the performance of their application in terms of efficiency, size, robustness and total cost of ownership.

Finally, it should be noted that as well as the gate driver ICs themselves, Infineon is also providing comprehensive development and prototyping support in the form of application-specific evaluation boards and reference designs. Built around the 2EDNx52x drivers and the new CoolMOS C7 600V MOSFETs, these evaluation and development tools include a 130kHz 800W CCM PFC board, a 3.5kW PFC design, and a halfbridge 600W LLC board with a 12V, 50A output.

www.infineon.com