User's Manual, V 1.0, August 2001

THEREP

## C166S V1 Multiply-Accumulate Unit C166S V1 MAC

Microcontrollers

Never stop thinking.

Edition 2001-08

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# C166S V1 Multiply-Accumulate Unit

C166S V1 MAC

## Microcontrollers

Never stop thinking.

#### C166S V1 MAC

| Revision History:<br>Previous Version: |          | 2001-08                             | V 1.0 |  |  |

|----------------------------------------|----------|-------------------------------------|-------|--|--|

|                                        |          |                                     |       |  |  |

| Page                                   | Subjects | (major changes since last revision) |       |  |  |

|                                        |          |                                     |       |  |  |

|                                        |          |                                     |       |  |  |

|                                        |          |                                     |       |  |  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

ce.cmd@infineon.com

## User's Manual C166S V1 MAC Unit

#### **Table of Contents**

## Page

| <b>1</b><br>1.1<br>1.2<br>1.3                                    | MAC Unit Features3Enhanced Addressing Capabilities5Multiply-Accumulate Unit5Program Control5                                                                                                                                              |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4                             | MAC Unit Operation6Instruction Pipelining6Address Generation6CoReg Addressing Mode9Number Representation and Rounding9                                                                                                                    |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | MAC Unit Components1016 x 16 Signed/Unsigned Parallel Multiplier10Concatenation Unit10Sign Extension Unit and Scaler1040-bit Signed Arithmetic Unit1140-bit Signed Accumulator Register12Data Limiter12Accumulator Shifter13Repeat Unit13 |

| 4                                                                | MAC Unit Interrupt                                                                                                                                                                                                                        |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5                      | MAC Unit Register Set18MAC Unit Address Registers19Accumulator Registers20MAC Unit Status Word (MSW)21MAC Unit Control Word (MCW)24MAC Unit Repeat Word (MRW)25                                                                           |

| <b>6</b><br>6.1<br>6.2                                           | MAC Unit Instruction Set26Syntax26List of MAC Unit Instructions28                                                                                                                                                                         |

| 7                                                                | Instruction Index 123                                                                                                                                                                                                                     |

| 8                                                                | Keyword Index 125                                                                                                                                                                                                                         |

## List of Tables

## Page

| Table 1 | Pointer Post-modification Combinations for IDXi and Rwn | 7         |

|---------|---------------------------------------------------------|-----------|

| Table 2 | Parallel Data Move Addressing                           | 8         |

| Table 3 | CoReg 5-bit Addressing Mode                             | 9         |

| Table 4 | Data Limiter Output 1                                   | 2         |

| Table 5 | MAC Unit Instruction Set Summary 2                      | <u>29</u> |

#### **MAC Unit Features**

## 1 MAC Unit Features

The Multiply-Accumulate (MAC) Unit is a specialized co-processor added to the C166S CPU core to improve the performance of signal processing algorithms. It includes:

- a multiply-accumulate unit

- an address generation unit capable of feeding the MAC Unit with 2 operands per cycle

- a repeat unit to execute a series of multiply-accumulate instructions

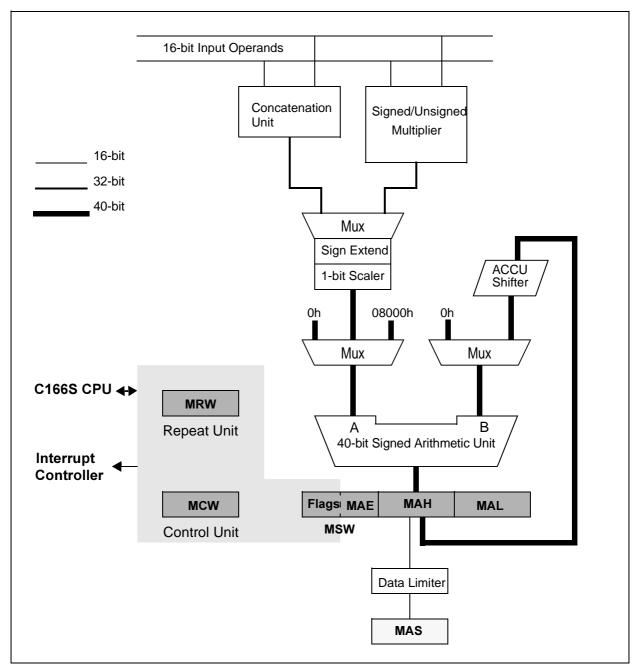

The architecture of the MAC Unit is outlined in Figure 1.

## User's Manual C166S V1 MAC Unit

**MAC Unit Features**

**MAC Unit Architecture**

#### **MAC Unit Features**

The MAC Unit includes the following features.

## 1.1 Enhanced Addressing Capabilities

- New addressing modes, including a double indirect addressing mode with pointer post-modification.

- Parallel Data Move allows one operand move during multiply-accumulate instructions without penalty.

- New transfer instructions CoSTORE (for fast access to the MAC Unit SFRs) and CoMOV (for fast memory to memory table transfer).

## 1.2 Multiply-Accumulate Unit

- Execution of all MAC Unit operations within one CPU instruction cycle

- 16 x 16 signed/unsigned parallel multiplier

- 40-bit signed arithmetic unit with automatic saturation mode

- 40-bit signed accumulator

- 8-bit left/right shifter

- Scaler (one-bit left shifter)

- Data limiter

- Full instruction set with multiply and multiply-accumulate, 32-bit signed arithmetic, and compare instructions

- Three 16-bit status and control registers:

- MSW MAC Unit Status Word

- MCW MAC Unit Control Word

- MRW MAC Unit Repeat Word

## 1.3 **Program Control**

- Repeat Unit to allow some MAC Unit co-processor instructions to be repeated up to 8192 times. Repeated instructions may be interrupted.

- MAC Unit interrupt (implemented as Class B hardware trap) on MAC Unit condition flags.

## 2 MAC Unit Operation

MAC Unit operation is based on the cores instruction pipeline and extended addressing modes.

## 2.1 Instruction Pipelining

All MAC Unit instructions use a 4-stage pipeline. During each stage the following tasks are performed:

- **FETCH** All new instructions are double-word instructions.

- **DECODE** If required, operand addresses are calculated and the resulting operands are fetched. IDX and GPR pointers are post-modified if necessary.

- **EXECUTE** Performs the MAC Unit operation. At the cycle end the accumulator and the MAC Unit condition flags are updated if required. Modified GPR pointers are written-back during this stage, if required.

- WRITEBACK Operand write-back in the case of parallel data move.

- Note: At least one instruction not using the MAC Unit must be inserted between two instructions that read from a MAC Unit register. This is because the accumulator and the status of the MAC Unit are modified during the Execute stage. The CoSTORE instruction has been added to allow access to the MAC Unit registers immediately after a MAC Unit operation.

## 2.2 Address Generation

MAC Unit instructions can use some of the standard C166 addressing modes such as GPR direct or #data4 for immediate shift value. New addressing modes were added to supply the MAC Unit with two new operands per instruction cycle. These allow indirect addressing with **address pointer post-modification**.

**Double indirect addressing** requires two pointers. Any GPR can be used for one pointer, the other pointer is provided by one of two specific SFRs IDX0 and IDX1. Two pairs of offset registers QR0/QR1 and QX0/QX1 are associated with each pointer (GPR or IDX<sub>i</sub>). The GPR pointer allows access to the entire memory space, but accesses via IDX<sub>i</sub> are limited to the internal dual-port RAM, except for the CoMOV instruction. The various combinations of pointer post-modification for each of the two new addressing modes are shown in Table 1. Symbols [Rw<sub>n</sub> $\otimes$ ] and [IDX<sub>i</sub> $\otimes$ ] refer to these addressing modes.

| Symbol                          | Mnemonic                              | Address Pointer Operation                                         |

|---------------------------------|---------------------------------------|-------------------------------------------------------------------|

| [IDX <sub>i</sub> ⊗] stands for | [IDX <sub>i</sub> ]                   | $(IDX_{i}) \leftarrow (IDX_{i}) \text{ (no-op)}$                  |

|                                 | [IDX <sub>i</sub> +]                  | $(IDX_i) \leftarrow (IDX_i)$ +2 (i=0,1)                           |

|                                 | [IDX <sub>i</sub> -]                  | $(IDX_i) \gets (IDX_i) \text{ -2 } (i{=}0{,}1)$                   |

|                                 | [IDX <sub>i</sub> + QX <sub>j</sub> ] | $(IDX_j) \gets (IDX_j) + (QX_j) \ (i, j = 0, 1)$                  |

|                                 | [IDX <sub>i</sub> - QX <sub>j</sub> ] | $(IDX_i) \gets (IDX_i) \text{ - } (QX_j)  (i, j = 0, 1)$          |

| $[Rw_n \otimes]$ stands for     | [Rw <sub>n</sub> ]                    | $(Rw_{n}) \leftarrow (Rw_{n}) \text{ (no-op)}$                    |

|                                 | [Rw <sub>n</sub> +]                   | $(Rw_{n}) \leftarrow (Rw_{n})$ +2 (n=0-15)                        |

|                                 | [Rw <sub>n</sub> -]                   | $(Rw_{n}) \leftarrow (Rw_{n})$ -2 (k=0-15)                        |

|                                 | [Rw <sub>n</sub> +QR <sub>j</sub> ]   | $(Rw_{n}) \leftarrow (Rw_{n}) + (QR_{j}) \text{ (n=0-15; j=0,1)}$ |

|                                 | [Rw <sub>n</sub> - QR <sub>j</sub> ]  | $(Rw_{n}) \leftarrow (Rw_{n})$ - $(QR_{j})$ (n=0-15; j =0,1)      |

#### Table 1Pointer Post-modification Combinations for IDXi and Rwn

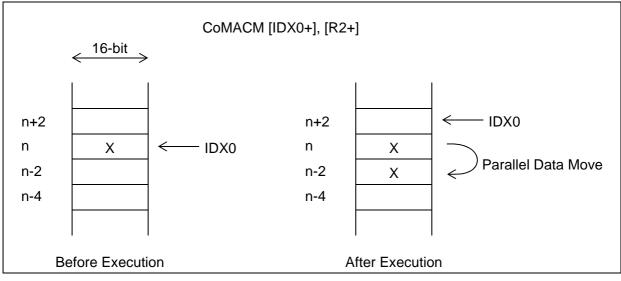

The CoMACM class of instructions is a certain set of instructions that implement a mechanism called **Parallel Data Move**. The CoMACM instructions exclusively use double indirect addressing mode. Parallel Data Move allows the operand pointed to by  $IDX_i$  to be moved to a new location in parallel with the MAC Unit operation. The writeback address for the Parallel Data Move is calculated depending on the post-modification of  $IDX_i$ .

It is obtained by the operation "reverse" to the pointer post-modification of  $IDX_i$ , as explained in **Table 2**.

#### Table 2 Parallel Data Move Addressing

| Instruction                                  | Writeback Address for Parallel Data<br>Move |

|----------------------------------------------|---------------------------------------------|

| CoMACM [IDX <sub>i</sub> +],                 | <idx<sub>i-2&gt;</idx<sub>                  |

| CoMACM [IDX <sub>i</sub> -],                 | <idx<sub>i+2&gt;</idx<sub>                  |

| CoMACM [IDX <sub>i</sub> +QX <sub>j</sub> ], | <idx<sub>i-QX<sub>j</sub>&gt;</idx<sub>     |

| CoMACM [IDX <sub>i</sub> -QX <sub>j</sub> ], | <idx<sub>i+QX<sub>j</sub>&gt;</idx<sub>     |

The Parallel Data Move shifts a table of operands in parallel with a computation on those operands. Its specific use is for signal processing algorithms like filter computation.

An example of Parallel Data Move using the CoMACM instruction is shown in Figure 2.

Figure 2 Example of Parallel Data Move

## 2.3 CoReg Addressing Mode

The MAC Unit accumulator and control registers (MAL, MAH, MSW, MCW, MRW) can be addressed by the regular instruction set as any other SFR. In addition, they can be addressed by the *CoSTORE* instruction. The CoSTORE instruction utilizes a specific 5-bit addressing mode called *CoReg* which allows the immediate storage of MAC Unit registers after an operation. Addresses of MAC Unit registers in CoReg addressing mode are shown in Table 3.

| Register | Description                              | 5-bit Address |

|----------|------------------------------------------|---------------|

| MSW      | MAC Unit Status Word                     | 00000         |

| MAH      | MAC Unit Accumulator High Word           | 00001         |

| MAS      | "limited" MAC Unit Accumulator High Word | 00010         |

| MAL      | MAC Unit Accumulator Low                 | 00100         |

| MCW      | MAC Unit Control Word                    | 00101         |

| MRW      | MAC Unit Repeat Word                     | 00110         |

#### Table 3 CoReg 5-bit Addressing Mode

MAS is a **virtual** register. If MAS is specified as a source operand for CoSTORE, the MAH register is read through the data limiter. MAS cannot be addressed by regular SFR/ESFR addressing.

## 2.4 Number Representation and Rounding

The MAC Unit supports the **two's-complement** representation of binary numbers. In this format the sign bit is the MSB of the binary word. This is set to zero for positive numbers and set to one for negative numbers. Unsigned numbers are supported only by multiply/multiply-accumulate instructions which specify whether each operand is signed or unsigned.

In two's complement fractional format the N-bit operand is represented using the 1.[N-1] format (1 signed bit, N-1 fractional bits). This format can represent numbers between -1 and  $+1-2^{-[N-1]}$  and is supported when the shift mode bit MP of register MCW is set.

The MAC Unit implements 'two's complement rounding', where one is added to the bit to the right of the rounding point (bit 15 of MAL) before truncation (MAL is cleared).

## 3 MAC Unit Components

The major components of the MAC Unit are shown in **Figure 1**. In the following, all of these components are described in detail.

## 3.1 16 x 16 Signed/Unsigned Parallel Multiplier

The multiplier executes 16 x 16-bit parallel signed/unsigned fractional and integer multiplications. The multiplier has two 16-bit input ports for the two operands and a 32-bit product output port. The result is always presented in a signed fractional or integer format.

## 3.2 Concatenation Unit

The concatenation unit enables the MAC Unit to perform 32-bit arithmetic operations in one CPU instruction cycle. It concatenates the two 16-bit operands to a 32-bit operand before the 32-bit operation is executed in the 40-bit arithmetic unit. The second required operand is always the current accumulator content. The concatenation unit is also used to pre-load the accumulator with a 32-bit value.

## 3.3 Sign Extension Unit and Scaler

Prior being fed to the 40-bit signed arithmetic unit, the result of the multiplier (or of the concatenation unit) is sign extended to a 40-bit number. This sign extension replicates the sign bit (MSB) of the word 8 times. With unsigned/unsigned instructions, (e.g. CoMULu, CoMACu) 8 zero bits are extended regardless of the MSB of the word to be extended.

The one-bit scaler can shift the sign extended result one bit to the left. Depending on the type of instruction, the scaler is controlled either by the Product Shift Mode Bit MP (bit 10 in MAC Unit Control Word - MCW) or by the instruction itself. For multiply instructions (if the MP bit is set), the product is automatically shifted left by one bit to compensate for the extra sign bit gained in multiplying two signed 2's complement numbers. The scaler is also active for instructions such as CoADD2, CoSUB2, etc., where the 32-bit operand is doubled before being fed to the arithmetic unit.

## 3.4 40-bit Signed Arithmetic Unit

The 40-bit signed arithmetic unit allows intermediate overflows in a series of multiply/ accumulate operations. There are two 40-bit input ports, A and B. The A-input port accepts data as 00'0000'0000h, 00'0000'8000h (round), or the sign extended and scaled result of the multiplier or of the concatenation unit.

The B-input port is the feedback of the accumulator output sent through the 8-bit left/right shifter. The B-input port can also receive 00'0000'0000h to allow direct transfer from the A-input port to the accumulator.

If, during accumulation, a 40-bit overflow of the accumulator occurs, the sticky overflow flag SV will be set in the MAC Unit Status Word (MSW).

The result of the addition/subtraction can be rounded or saturated on a 32-bit value automatically after every accumulation.

The rounding is performed by adding 00'0000'8000h to the result and clearing the Accumulator Low Word MAL. Automatic saturation is enabled by setting the saturation bit MS in the MAC Unit Control Word (MCW).

When the accumulator is in the saturation mode and a 32-bit overflow occurs, the accumulator is loaded with either the highest positive or the lowest negative value that can be represented with a 32-bit 2's complement number, depending on the direction of the overflow. Thus the value of the accumulator upon saturation is 00'7fff'ffffh (positive) or ff'8000'0000h (negative). Automatic saturation sets the sticky limit flag (SL) in the MAC Unit Status Word (MSW).

- Note: If automatic saturation and rounding is performed, MAL will be cleared on the saturated value and the result after saturating and rounding positive numbers will be 00'7fff 0000h.

- Note: If the accumulator contains a value that can not be represented by a 32-bit 2-s complement number (i.e. MS was previously set to 0), then saturation can only be achieved by setting MS to 1 and one MAC Unit instruction executing. If this instruction causes a 40-bit overflow (or underflow), then the value of the accumulator upon saturation is 00'7fff'ffffh (or ff'8000'0000h).

## 3.5 40-bit Signed Accumulator Register

Most co-processor operations specify the 40-bit accumulator register as a source and/or destination operand. The accumulator is comprised of three SFR registers:

- MAL (MAC Unit Accumulator Low Word),

- MAH (MAC Unit Accumulator High Word) and

- MAE (ACCU Extension).

While MAH and MAL are 16-bit wide, MAE consist of only 8-bits, which are accessed as the least significant byte of the MAC Unit Status Word MSW. MAE is the most significant byte of the accumulator.

When writing to MAH by regular SFR addressing, the value in the accumulator is automatically adjusted to a sign extended 40-bit 2's complement format. MAL acquires zero value and MAE is automatically loaded with zeros in case of a positive number (MAH has 0 in the most significant bit) and with ones in case of a negative number (MAH has 1 in the most significant bit). Note that the values represented by the 32-bit number and the extended 40-bit number are the same and the MAE register does not contain significant bits. This is true whenever the highest 9 bits of the signed 40-bit result are identical.

During accumulator operations an overflow may occur and the result may not fit into 32bits. The accumulator then exceeds the 32-bit boundary and changes the contents of MAE. Consequently there are significant (non-sign) bits in the top 8 bits of the accumulator. To indicate this extension, extension flag E, contained in the most significant byte of the MAC Unit Status Word MSW, is set to 1.

## 3.6 Data Limiter

Saturation arithmetic is also provided to selectively limit overflow when reading the accumulator by means of a *CoSTORE <destination>, MAS* instruction. If the contents of the accumulator cannot be represented by 32 bits without overflow, the limiter is enabled and MAS is modified to a limited value. Otherwise MAS is equal to MAH, as shown in Table 4.

| E bit | N bit | Limiter Output (MAS) |  |

|-------|-------|----------------------|--|

| 0     | X     | equal to MAH         |  |

| 1     | 0     | 7fffh                |  |

| 1     | 1     | 8000h                |  |

#### Table 4Data Limiter Output

Note: The MAS value is only readable by means of a **CoSTORE <destination>, MAS** instruction. If executed, the accumulator and the status register are not affected.

## 3.7 Accumulator Shifter

The accumulator shifter is a parallel shifter with 40-bit input and 40-bit output. The source operand of the shifter is an accumulator and possible shifting operations are:

- no shift (unmodified)

- up to 8-bit arithmetic left shift

- up to 8-bit arithmetic right shift

Note that left shift operations affect flags E, SV, SL, and C of the MAC Unit Status Word MSW. Therefore, if the automatic saturation mechanism is enabled (MS-bit set to 1), the behavior is similar to that of the 40-bit arithmetic unit.

Note: Certain precautions are required in cases of a left shift in conjunction with automatic saturation enabled (MS bit set to 1). If the MS bit is being set directly before the left shift instruction, correct saturation is not guaranteed under all circumstances since significant bits may have been shifted out before saturation is performed. To avoid this situation, switch on automatic saturation earlier so that the left shift instruction is already operating on a saturated value.

## 3.8 Repeat Unit

The MAC Unit includes a repeat unit which repeats some co-processor instructions up to  $2^{13}$  (=8192) times. The repeat count is specified either by an immediate value (up to 31) or by the content of the repeat count (bits 12 to 0) in the MAC Unit Repeat Word (MRW). If the repeat count in MRW equals **N**, the instruction will be executed **N+1** times. At each iteration of a repeated instruction the repeat count is tested for zero. If zero, the instruction is terminated, otherwise the repeat count is decremented and the instruction is repeated. During such repeated sequences, the Repeat Flag MR (bit 15 of the MAC Unit Repeat Word (MRW)) is set until the last execution of the repeated instruction.

The syntax of repeated instructions is shown in the following examples:

Repeat #24 times CoMAC[IDX0+],[R0+] ; performed 24 times

In this example, the instruction is repeated according to a 5-bit immediate value. The repeat count in MRW is automatically loaded with this value minus one.

```

MOV MRW, #00FFh ; load MRW

NOP ; instruction latency

Repeat MRW times

CoMACM [IDX1-],[R2+] ; performed 256 times

```

The instruction is repeated according to the repeat count in MRW. Note that, due to the pipeline processing, at least one instruction should be inserted between MRW write and the next repeated instruction.

Repeat sequences may be interrupted. When an interrupt occurs during a repeat sequence, the sequence is stopped and the interrupt routine is executed. The repeat sequence resumes at the end of the interrupt routine. During the interrupt the repeat flag MR remains set, indicating that a repeated instruction has been interrupted and the repeat count holds the number of repetitions (minus 1) that remain to complete the sequence. If the repeat unit is used in the interrupt routine, MRW must be saved by the user and restored before the end of the interrupt routine.

Note: The MRW register must be used with caution. Except for restoring MRW after an interrupt, the MR bit should not be set by user. Otherwise correct instruction processing cannot be guaranteed.

#### **MAC Unit Interrupt**

## 4 MAC Unit Interrupt

The MAC Unit can generate an interrupt corresponding to the value of the status flags C (Carry), SV (Sticky Overflow), E (Extension) or SL (Sticky Limit) of the MSW register.

The MAC Unit Interrupt is globally enabled if the MIE flag in MCW is set. When enabled, the flags C, SV, E, or SL can trigger a MAC Unit Interrupt, provided that the corresponding mask flags CM, VM, EM, and LM in MCW are also set. The MIR flag in MSW is set upon the first interrupt condition. This flag must be cleared during interrupt processing. If this flag is set already, a new interrupt condition cannot trigger an interrupt.

The MAC Unit Interrupt is implemented as a Class B hardware trap (trap number  $A_H$ , trap priority I). The associated trap flag in the Trap Flag Register TFR is MACTRP (bit 6). Note that when a MAC Unit interrupt request occurs, this flag must be cleared by the user.

The layout of the Trap Flag Register TFR in the C166S V1.1 is as follows:

| TFR<br>Trap | Flag      | Regi      | ster |    |    | SFI | SFR(FFAC <sub>H</sub> ,D6 <sub>H</sub> ) |            |            |   |   |            | Reset value: 0000 <sub>H</sub> |            |            |  |  |

|-------------|-----------|-----------|------|----|----|-----|------------------------------------------|------------|------------|---|---|------------|--------------------------------|------------|------------|--|--|

| 15          | 14        | 13        | 12   | 11 | 10 | 9   | 8                                        | 7          | 6          | 5 | 4 | 3          | 2                              | 1          | 0          |  |  |

| NMI         | STK<br>OF | STK<br>UF | 0    | 0  | 0  | 0   | 0                                        | UND<br>OPC | MAC<br>TRP | 0 | 0 | PRT<br>FLT | ILL<br>OPA                     | ILL<br>INA | ILL<br>BUS |  |  |

| -           |           |           | r    | r  | r  | r   | r                                        | rwh        | rwh        | r | r |            |                                |            |            |  |  |

| Field                | Bits | Туре | Description                                                                                                                                                          |

|----------------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILLBUS               | [0]  | rwh  | <ul> <li>ILLegal External BUS Access</li> <li>No illegal external bus access detected</li> <li>An external access has been attempted with no bus defined.</li> </ul> |

| ILLINA <sup>1)</sup> | [1]  | rwh  | <ul> <li>ILLegal INstruction Access</li> <li>0 No illegal instruction access detected</li> <li>1 A branch to an odd address has been attempt.</li> </ul>             |

| ILLOPA <sup>1)</sup> | [2]  | rwh  | <ul> <li>ILLegal word OPerand Access</li> <li>No illegal word operand access event</li> <li>detected</li> <li>1 Ilegal word operand access event detected</li> </ul> |

| PRTFLT <sup>1)</sup> | [3]  | rwh  | <ul> <li>PRoTection FauLT</li> <li>0 No protection fault event detected</li> <li>1 Protection fault event detected</li> </ul>                                        |

#### **MAC Unit Interrupt**

| Field                | Bits                           | Туре | Description                                                                                                                              |  |  |  |  |  |  |

|----------------------|--------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MACTRP               | [6]                            | rwh  | <ul> <li>MAC Unit Interrupt</li> <li>No MAC Unit interrupt detected</li> <li>MAC Unit interrupt detected</li> </ul>                      |  |  |  |  |  |  |

| UNDOPC <sup>1)</sup> | [7]                            | rwh  | <ul><li>UNDefined OPCode</li><li>0 No undefined opcode event detected</li><li>1 Undefined opcode event detected</li></ul>                |  |  |  |  |  |  |

| STKUF <sup>1)</sup>  | [13]                           | rwh  | <ul> <li>STacK UnderFlow flag</li> <li>No stack underflow event detected</li> <li>Stack underflow event detected</li> </ul>              |  |  |  |  |  |  |

| STKOF <sup>1)</sup>  | [14]                           | rwh  | <ul> <li>STacK OverFlow flag</li> <li>No stack overflow event detected</li> <li>Stack overflow event detected</li> </ul>                 |  |  |  |  |  |  |

| NMI <sup>1)</sup>    | [15]                           | rwh  | <ul> <li>Non-Maskable Interrupt flag</li> <li>0 No non-maskable interrupt detected</li> <li>1 Non-maskable interrupt detected</li> </ul> |  |  |  |  |  |  |

| 0                    | [12, 11,<br>10, 9, 8,<br>5, 4] | r    | Reserved read as '0'; writing to these bit positions has no effect.                                                                      |  |  |  |  |  |  |

<sup>1)</sup> This bit supports bit protection

## Note: The trap service routine must clear the respective trap flag. Otherwise, a new trap will be requested after exiting the service routine. Setting a trap request flag by software causes the same effects as if it had been set by hardware.

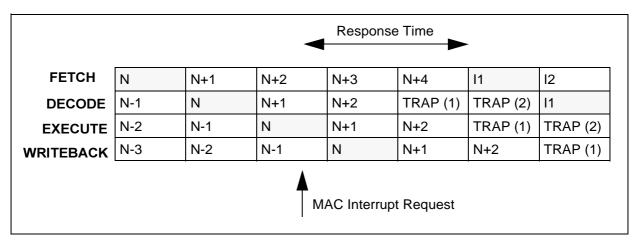

As MAC Unit status flags are updated (or written by software) during the execute stage of the pipeline, the response time of a MAC Unit Interrupt Request is 3 instruction cycles, as illustrated in **Figure 3**. It is the number of instruction cycles required between the time the request is sent and the time the first instruction located at the interrupt vector location enters the pipeline.

Note: The instruction pointer value stacked after a MAC Unit Interrupt does not point to the instruction that triggered the interrupt. Therefore, it is not possible to specify exactly the entry point of the interrupt. Furthermore, due to the interrupt response time, it may not be possible to determine the source of the interrupt request since the status of flags C, SV, E, or SL may have changed once the interrupt routine has started.

#### **MAC Unit Interrupt**

## 5 MAC Unit Register Set

All MAC Unit registers are mapped into the SFR/ESFR memory space. Registers can be accessed using the regular instruction set and the co-processor instruction called CoSTORE. The following sections list the MAC Unit registers and their corresponding SFR/ESFR addresses.

Note: With CPU Core SFRs, any write operation with the regular instruction set to a single byte of a MAC SFR, clears the non-addressed complementary byte within the specified SFR. Non-implemented SFR bits cannot be modified and always supply a read value of '0'.

## 5.1 MAC Unit Address Registers

The double indirect addressing modes require additional (E)SFRs: 2 address pointers IDX0/IDX1 and 4 offset registers QX0/QX1 and QR0/QR1.

The address pointer registers IDX0 and IDX1 are located in the SFR space.

| IDX0 (FF08h/84h)<br>IDX1 (FF0Ah/85h) |    |    |    |    |    | SFR<br>SFR |      |   |   |   |   | Reset Value: 0000h<br>Reset Value: 0000h |   |   |   |  |

|--------------------------------------|----|----|----|----|----|------------|------|---|---|---|---|------------------------------------------|---|---|---|--|

| 15                                   | 14 | 13 | 12 | 11 | 10 | 9          | 8    | 7 | 6 | 5 | 4 | 3                                        | 2 | 1 | 0 |  |

|                                      | 1  |    |    |    |    | 1          | IDXi | 1 |   | ļ | ļ | 1                                        |   |   | 0 |  |

|                                      |    |    |    |    |    |            | rw   | I | 1 |   |   |                                          |   |   | r |  |

| Field | Bits   | Туре | Description                                                   |

|-------|--------|------|---------------------------------------------------------------|

| IDXi  | [15:1] | rw   | Modifiable portion of address pointer                         |

| 0     | [0]    | r    | As IDXi may only contain even values, bit 0 is fixed to zero. |

The offset registers QX0, QX1, QR0, and QR1 are located in the ESFR space.

| QX0 (F000h/00h)<br>QX1 (F002h/01h)<br>QR0 (F004h/02h)<br>QR1 (F006h/03h) |    |    |    |    |    |   | ES<br>ES | FR<br>FR<br>FR<br>FR |   |   |   | Res<br>Res | et Va<br>et Va | lue: (<br>lue: ( | 0000h<br>0000h<br>0000h<br>0000h |

|--------------------------------------------------------------------------|----|----|----|----|----|---|----------|----------------------|---|---|---|------------|----------------|------------------|----------------------------------|

| 15                                                                       | 14 | 13 | 12 | 11 | 10 | 9 | 8        | 7                    | 6 | 5 | 4 | 3          | 2              | 1                | 0                                |

|                                                                          | 1  | 1  | 1  | 1  | 1  | G | QXi/QF   | Ri                   | 1 | 1 | I |            | 1              | 1                | 0                                |

| L                                                                        |    |    | 1  | 1  | 1  | 1 | rw       |                      |   |   |   |            |                |                  | r                                |

| Field   | Bits   | Туре | Description                                                                                                                 |

|---------|--------|------|-----------------------------------------------------------------------------------------------------------------------------|

| QRi/QXi | [15:1] | rw   | Modifiable portion of offset registers<br>Specifies 16-bit address offset for IDXi pointers<br>(QXi) or GPR pointers (QRi). |

| 0       | [0]    | r    | As MAC Unit instructions handle word operands only, bit 0 is fixed to '0'.                                                  |

### 5.2 Accumulator Registers

The 40-bit accumulator consists of the registers MAL, MAH and the low byte of MSW, which is described in **Chapter 5.3**.

MAL and MAH are located in the non bit-addressable SFR space.

| MAH          | (FE5                 | Eh/2F    | <sup>-</sup> h) |    |                                              |                                                                               | SF          | R  |          |          |          | Res | et Va | lue: 0   | 000h     |

|--------------|----------------------|----------|-----------------|----|----------------------------------------------|-------------------------------------------------------------------------------|-------------|----|----------|----------|----------|-----|-------|----------|----------|

| 15           | 14                   | 13       | 12              | 11 | 10                                           | 9                                                                             | 8           | 7  | 6        | 5        | 4        | 3   | 2     | 1        | 0        |

|              |                      |          |                 |    |                                              |                                                                               | M           | ٩H |          |          |          |     |       | •        |          |

|              | <u> </u>             | <u>I</u> | <u>I</u>        | I  | <u>                                     </u> |                                                                               | r           | w  | <u> </u> | <u>I</u> | <u> </u> | 1   | I     | <u> </u> | <u> </u> |

| Field        | Field Bits Ty        |          |                 |    |                                              |                                                                               | Description |    |          |          |          |     |       |          |          |

| MAH          | <b>MAH</b> [15:0] rv |          |                 |    |                                              | rw <b>MAC Unit Accumulator</b><br>Contains bits 31 to 16 of t<br>Accumulator. |             |    |          |          |          |     |       | Unit     |          |

| MAL          | (FE5                 | Ch/2E    | Eh)             |    |                                              | SFR                                                                           |             |    |          |          |          | Res | et Va | lue: 0   | 000h     |

| 15           | 14                   | 13       | 12              | 11 | 10                                           | 9                                                                             | 8           | 7  | 6        | 5        | 4        | 3   | 2     | 1        | 0        |

|              |                      |          |                 |    |                                              |                                                                               | M           | AL |          |          |          |     |       |          |          |

| L            | 1                    | I        | I               | I  | II                                           |                                                                               | rv          | vh | I        | I        | I        | 1   | I     | 1        |          |

| Field Bits T |                      |          |                 |    | <b>T</b>                                     | - Decemination                                                                |             |    |          |          |          |     |       |          |          |

| Field | Bits   | Туре | Description                                                                                   |

|-------|--------|------|-----------------------------------------------------------------------------------------------|

| MAL   | [15:0] | rwh  | MAC Unit Accumulator Low Word<br>Contains bits 15 to 0 of the 40-bit MAC Unit<br>Accumulator. |

Note: MAL is automatically cleared when MAH is written by regular SFR addressing.

## 5.3 MAC Unit Status Word (MSW)

The bit-addressable register MSW reflects the current state of the MAC Unit. It is located in the SFR space and includes the 8-bit accumulator extension MAE and the 7 additional flags as shown below.

| MSW            | (FFC | DEh/E | Fh) |                      |                                                                                                                                          | SFR                                                                                                                      |                         |                     |         |                                 |         | Reset Value: 0200h |        |        |   |  |  |

|----------------|------|-------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------|---------|---------------------------------|---------|--------------------|--------|--------|---|--|--|

| 15             | 14   | 13    | 12  | 11                   | 10                                                                                                                                       | 9                                                                                                                        | 8                       | 7                   | 6       | 5                               | 4       | 3                  | 2      | 1      | 0 |  |  |

| MIR            | -    | SL    | Е   | sv                   | С                                                                                                                                        | z                                                                                                                        | N                       |                     | I       | MAE (                           | ACCL    | l Exte             | nsion  | )      | 1 |  |  |

| rwh            | -    | rwh   | rwh | rwh                  | rwh                                                                                                                                      | rwh                                                                                                                      | rwh rwh                 |                     |         |                                 |         |                    |        |        |   |  |  |

| Field          |      |       | В   | its                  | Туре                                                                                                                                     | De                                                                                                                       | Description             |                     |         |                                 |         |                    |        |        |   |  |  |

| MAE            |      |       | [7  | :0]                  | rwh                                                                                                                                      | Th                                                                                                                       | CUE<br>e eigh<br>it acc | nt mos              | st sig  | nifican                         | it bits | of the             | e 40-b | oit MA | С |  |  |

| N              |      |       |     |                      |                                                                                                                                          | <ul> <li>h Negative Result Flag</li> <li>0 MAC Unit result is negative</li> <li>1 MAC Unit result is positive</li> </ul> |                         |                     |         |                                 |         |                    |        |        |   |  |  |

| Z              |      |       | [9  | ]                    | rwh                                                                                                                                      | Zero Flag0MAC Unit result is not zero1MAC Unit result is zero                                                            |                         |                     |         |                                 |         |                    |        |        |   |  |  |

| С              |      |       | [1  | 0]                   | rwh                                                                                                                                      | <b>Ca</b><br>0<br>1                                                                                                      |                         | o carr              |         | row pr<br>/ prodi               |         | əd                 |        |        |   |  |  |

| SV             |      |       | [1  | 1]                   | rwh                                                                                                                                      | <b>Sti</b><br>0<br>1                                                                                                     |                         | o 40-b              | oit ove | i <b>lag</b><br>erflow<br>w occ |         |                    |        |        |   |  |  |

| E [12]         |      |       |     | rwh                  | <ul> <li>wh</li> <li>Extension Flag</li> <li>0 MAE does not contain significant bits</li> <li>1 MAE contains significant bits</li> </ul> |                                                                                                                          |                         |                     |         |                                 |         |                    |        |        |   |  |  |

| <b>SL</b> [13] |      |       | rwh | <b>Sti</b><br>0<br>1 |                                                                                                                                          | o auto                                                                                                                   | matio                   | c 32-bi<br>2-bit sa |         |                                 |         |                    |        |        |   |  |  |

| MIR [15] rwh   |      |       |     |                      |                                                                                                                                          | <b>M/</b><br>0<br>1                                                                                                      | 1 1                     |                     |         |                                 |         |                    |        |        |   |  |  |

#### ACCU Extension MAE

These 8 bits are part of the 40-bit accumulator register. The MAC Unit implicitly uses these bits during a MAC Unit operation. When writing to MAH by regular SFR addressing, MAE is automatically sign extended with the most significant bit of MAH and MAL is cleared.

#### Negative Result Flag N

The N flag is set if the most significant bit of the accumulator equals '1', otherwise it is cleared. With integer operations, the N Flag can be interpreted as the sign bit of the MAC Unit Accumulator (N=1 for negative, N=0 for positive). Negative numbers are always represented as the 2's complementation of the corresponding positive.

#### Zero Flag Z

The Z flag is set if the content of the MAC Unit Accumulator is equal to zero, otherwise it is cleared.

#### Carry Flag C

After a MAC Unit addition, the C flag indicates that a carry from the accumulator's most significant bit (bit 7 of MAE) has been generated. After a MAC Unit subtraction, the C flag indicates a "Borrow", which represents the logical negation of a "Carry" for the addition. During a subtraction, the C flag is set, if **no** carry from the most significant bit of the accumulator has been generated. Subtraction is performed by the MAC Unit as a 2's complement addition and the C flag is cleared when this complement addition caused a "Carry".

For left shift operations, the C flag represents the value of the bit shifted out last. Right shift operations always clear the C flag.

#### Sticky Overflow Flag SV

The SV flag indicates an arithmetic overflow. The SV flag is set if, during a MAC Unit operation, the accumulator exceeds the maximum range of 40-bit signed numbers. In the case of signed arithmetic, the SV flag is set if the carry into the sign bit differs from the carry out of the sign bit. With a left shift operation, the SV flag is set if the last bit shifted out is different from the new N flag.

If the SV flag is set then the result of the MAC Unit operation is invalid. Once set, other MAC Unit operations cannot affect the status of the SV flag. Only a direct write operation can clear it.

#### Extension Flag E

The E flag is set if the accumulator extension MAE contains significant bits, i.e., if the highest 9 bits of the accumulator are not identical.

C166S V1 MAC, User's Manual

#### Sticky Limit Flag SL

The SL flag is set if an automatic 32-bit saturation occurred. Automatic saturation is enabled by setting bit MS of the MAC Unit Control Word (MCW). The SL flag can also be set by a CoMIN or CoMAX operation. In such cases, the SL flag is set when the contents of the accumulator is greater than the operand of the CoMAX operation, or less than the operand of the CoMIN operation.

The SL flag is a sticky flag and, once set, is not affected by any other MAC Unit operation until cleared by a direct write operation.

#### MAC Unit Interrupt Request Flag MIR

The MIR flag indicates a MAC Unit Interrupt request. The interrupt mask bits of the MAC Unit Control Word (MCW) determine which flags of the MSW register can generate a MAC Unit Interrupt request. The MIR flag must be cleared during the interrupt routine.

Note: The MAC Unit status flags are modified (if needed) by executing the instruction. They are **not affected by any instruction from the regular set** and thus their values may not be consistent with the accumulator content. For example, loading the accumulator with MOV instructions will not modify the status flags.

## 5.4 MAC Unit Control Word (MCW)

The bit-addressable register (MCW) controls the operation of the MAC Unit and determines the functionality of the MAC Unit Interrupt. (MCW) is located in the SFR space.

| MCW | MCW (FFDCh/EEh) |    |    |    |    |    | SF | R |   | Reset Value: 0000h |   |   |   |   |   |

|-----|-----------------|----|----|----|----|----|----|---|---|--------------------|---|---|---|---|---|

| 15  | 14              | 13 | 12 | 11 | 10 | 9  | 8  | 7 | 6 | 5                  | 4 | 3 | 2 | 1 | 0 |

| MIE | LM              | EM | VM | СМ | MP | MS |    |   |   |                    | - | - | - | - | - |

| rw  | rw              | rw | rw | rw | rw | rw |    |   |   |                    |   |   |   |   |   |

| Field | Bits | Туре | Description                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| MS    | [9]  | rw   | Saturation Control0Automatic saturation disabled1Automatic saturation enabled                                                            |

| MP    | [10] | rw   | One-bit Scaler Control0Multiplier product shift disabled1Multiplier product shift enabled                                                |

| СМ    | [11] | rw   | Carry Mask0C flag cannot generate interrupt request1C flag can generate interrupt request                                                |

| VM    | [12] | rw   | Overflow Mask0SV flag cannot generate interrupt request1SV flag can generate interrupt request                                           |

| EM    | [13] | rw   | Extension Mask0E flag cannot generate interrupt request1E flag can generate interrupt request                                            |

| LM    | [14] | rw   | Limit Mask0SL flag cannot generate interrupt request1SL flag can generate interrupt request                                              |

| MIE   | [15] | rw   | <ul> <li>MAC Unit Interrupt Enable</li> <li>MAC Unit interrupt globally disabled</li> <li>MAC Unit interrupt globally enabled</li> </ul> |

#### Saturation Control Bit MS

If the MS bit is set, the accumulator is automatically saturated to 32 bits.

#### One-bit Scaler Control Bit MP

If the MP bit is set and both operands of a multiplication are signed, then the multiplier output is automatically shifted left by one bit. With multiply-accumulate operations the multiplier output is shifted before it is added to the accumulator.

#### Interrupt Mask Flags CM, VM, EM, LM

These bits are interrupt mask bits for the corresponding MAC Unit status bits. If a status flag and the corresponding mask bit are set, then the MIR flag of MSW will be set and a MAC Unit interrupt will be activated (provided that interrupts are enabled).

#### MAC Unit Interrupt Enable Bit MIE

The MIE bit globally enables or disables the MAC Unit interrupt. When set, the flags C, SV, E and SL from the MSW register can trigger an interrupt (provided that the corresponding mask flags CM, VM, EM, and LM of the (MCW) register are also set).

## 5.5 MAC Unit Repeat Word (MRW)

The MRW contains the number of repetitions an instruction is to be executed and is located in the SFR space.

| MRW (FFDAh/EDh) |    |    |    |    |     |   | SF | R   |        | Reset Value: 0000h |   |   |   |          |          |

|-----------------|----|----|----|----|-----|---|----|-----|--------|--------------------|---|---|---|----------|----------|

| 15              | 14 | 13 | 12 | 11 | 10  | 9 | 8  | 7   | 6      | 5                  | 4 | 3 | 2 | 1        | 0        |

| MR              | -  | -  |    | Ι  | 1 1 |   | Ι  | Rep | eat Co | ount               | Ι | Ι | Ι | Ι        |          |

| rwh             | -  |    |    | I  | 11  |   | I  | I   | rwh    |                    | I | I | I | <u>I</u> | <u> </u> |

| Field        | Bits   | Туре | Description                                                                                                                |

|--------------|--------|------|----------------------------------------------------------------------------------------------------------------------------|

| Repeat Count | [12:0] | rwh  | <b>13-bit unsigned integer value</b><br>Indicates the number of times minus one a<br>repeated instruction must be executed |

| MR           | [15]   | rwh  | Repeat Flag<br>Set when a repeated instruction is being executed                                                           |

## 6 MAC Unit Instruction Set

The MAC Unit instruction set contains the following groups of instructions:

- multiply and multiply-accumulate instructions

- 32-bit arithmetic instructions

- shift instructions

- compare instructions

- transfer instructions

All MAC Unit instructions are 32-bit instructions with 4 bytes used to encode each instruction.

## 6.1 Syntax

#### Operands:

| орХ     | specifies the immediate constant value of opX                                                    |

|---------|--------------------------------------------------------------------------------------------------|

| (opX)   | specifies the contents of opX                                                                    |

| (opXn)  | specifies the contents of bit n of opX                                                           |

| ((opX)) | specifies the contents of the contents of opX, i.e. opX is used as pointer to the actual operand |

#### **Operations:**

| (opX)← (opY)      | (opY) <b>moved</b> into (opX)            |

|-------------------|------------------------------------------|

| +                 | added to                                 |

| -                 | subtracted from                          |

| *                 | multiplied by                            |

| $\Leftrightarrow$ | compared against                         |

| <<                | logically <b>shifted</b> left            |

| >>                | logically shifted right                  |

| >> <sub>a</sub>   | arithmetically shifted right             |

| (opX)    (opY)    | (opX) (MSW) and (opY) (LSW) concatenated |

#### Data Addressing Modes:

| Rw <sub>n</sub> or Rw <sub>m</sub> | General Purpose (Word) Registers (GPRs), where "n" and "m" can be any value between 0 and 15. |

|------------------------------------|-----------------------------------------------------------------------------------------------|

| []                                 | indirect word memory location                                                                 |

| Mxx                                | MAC Unit Register (MSW, MAH, MAL, MAS, MRW, MCW)                                              |

| ACC:                               | MAC Unit Accumulator consisting of lowest byte of MSW, MAH and MAL.                           |

| #datax:                            | Immediate constant (the number of significant bits is represented by 'x').                    |

#### Flag States:

| - | unchanged |  |  |

|---|-----------|--|--|

| * | modified  |  |  |

#### Address Register Operations for double indirect addressing:

| any GPR   | first address pointer, allows to access the entire memory space |

|-----------|-----------------------------------------------------------------|

| QR0/QR1   | offset registers for first address pointer (GPR)                |

| IDX0/IDX1 | second address pointer, limited to internal dual-port RAM       |

|           | (except for CoMOV instruction)                                  |

| QX0/QX1   | offset registers for second address pointer                     |

The symbols  $[\mathbf{Rw}_n \otimes]$  and  $[\mathbf{IDX}_i \otimes]$  refer to the various combinations of pointer post modifications, and are listed in Table 1.

#### **Repeated Instruction Syntax:**

Repeatable instructions, CoXXX, when repeated are expressed as follows:

repeat #data5 times CoXXX...

or

repeat MRW times CoXXX...

If MRW is invoked, the instruction is repeated (MRW[12:0]) + 1 times. Therefore, the maximum number an instruction can be repeated is  $2^{13} = 8192$ .

The integer value #data5 specifies the number of times an instruction is repeated. Hence #data5 must be less than 32, and CoXXX can only be repeated up to 31 times.

#### Shift Value:

The shifter allows left/right shift operations up to 8-bit. A shift value larger than 8 invokes an 8 bit shift.

#### **Instruction Encoding:**

| Х      | 4-bit IDX addressing mode encoding           |

|--------|----------------------------------------------|

| qqq    | 3-bit GPR offset encoding                    |

| rrrr:r | 5-bit repeat field                           |

| wwww:w | 5-bit CoReg address for CoSTORE instructions |

| SSSS:  | 4-bit immediate shift value                  |

## 6.2 List of MAC Unit Instructions

The MAC Unit instruction set is summarized in **Table 5**. Individual instructions are described in detail alphabetically.

## User's Manual C166S V1 MAC Unit

#### **MAC Unit Instruction Set**

| Mnemonic     | Addressing                            | Rep | Mnemonic      | Addressing                            | Rep |

|--------------|---------------------------------------|-----|---------------|---------------------------------------|-----|

|              | Modes                                 |     |               | Modes                                 | •   |

| CoMUL        | Rw <sub>n</sub> , Rw <sub>m</sub>     | No  | CoMACM        | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | Yes |

| CoMULu       | [IDXi⊗], [Rw <sub>m</sub> ⊗]          |     | CoMACMu       |                                       |     |

| CoMULus      | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] |     | CoMACMus      |                                       |     |

| CoMULsu      |                                       |     | CoMACMsu      |                                       |     |

| CoMUL-       | _                                     |     | CoMACM-       |                                       |     |

| CoMULu-      |                                       |     | CoMACMu-      |                                       |     |

| CoMULus-     |                                       |     | CoMACMus-     |                                       |     |

| CoMULsu-     |                                       |     | CoMACMsu-     |                                       |     |

| CoMUL+rnd    |                                       |     | CoMACM+rnd    |                                       |     |

| CoMULu+rnd   |                                       |     | CoMACMu+rnd   |                                       |     |

| CoMULus+rnd  |                                       |     | CoMACMus+rnd  |                                       |     |

| CoMULsu+rnd  | -                                     |     | CoMACMsu+rnd  |                                       |     |

| CoMAC        | Rw <sub>n</sub> , Rw <sub>m</sub>     | No  | CoMACMR       |                                       |     |

| CoMACu       | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | Yes | CoMACMRu      |                                       |     |

| CoMACus      | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] |     | CoMACMRus     |                                       |     |

| CoMACsu      |                                       |     | CoMACMRsu     |                                       |     |

| CoMAC-       |                                       |     | CoMACMR+rnd   |                                       |     |

| CoMACu-      |                                       |     | CoMACMRu+rnd  |                                       |     |

| CoMACus-     |                                       |     | CoMACMRus+rnd |                                       |     |

| CoMACsu-     |                                       |     | CoMACMRsu+rnd |                                       |     |

| CoMAC+rnd    |                                       |     | CoADD         | Rw <sub>n</sub> , Rw <sub>m</sub>     | No  |

| CoMACu+rnd   |                                       |     | CoADD2        | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | Yes |

| CoMACus+rnd  |                                       |     | CoSUB         | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] |     |

| CoMACsu+rnd  |                                       |     | CoSUB2        |                                       |     |

| CoMACR       |                                       |     | CoSUBR        |                                       |     |

| CoMACRu      |                                       |     | CoSUB2R       |                                       |     |

| CoMACRus     |                                       |     | CoMAX         |                                       |     |

| CoMACRsu     |                                       |     | CoMIN         |                                       |     |

| CoMACR+rnd   |                                       |     | CoLOAD        | Rw <sub>n</sub> , Rw <sub>m</sub>     | No  |

| CoMACRu+rnd  |                                       |     | CoLOAD-       | [IDXi⊗], [Rw <sub>m</sub> ⊗]          |     |

| CoMACRus+rnd |                                       |     | CoLOAD2       | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] |     |

| CoMACRsu+rnd |                                       |     | CoLOAD2-      |                                       |     |

| CoNOP        | [Rw <sub>n</sub> ⊗]                   | Yes | CoCMP         |                                       |     |

|              | [IDXi⊗]                               |     | CoSHL         | #data4                                | No  |

|              | [IDXi⊗], [Rw <sub>m</sub> ⊗]          |     | CoSHR         | Rw <sub>m</sub>                       | Yes |

| CoNEG        |                                       | No  | CoASHR        | [Rw <sub>m</sub> ⊗]                   |     |

| CoNEG+rnd    |                                       |     | CoASHR+rnd    |                                       |     |

| CoRND        |                                       |     | CoABS         | Rw <sub>n</sub> , Rw <sub>m</sub>     | No  |

| CoSTORE      | Rw <sub>n</sub> , CoReg               | No  |               | [IDXi⊗], [Rw <sub>m</sub> ⊗]          |     |

|              | [Rw <sub>n</sub> ⊗], CoReg            | Yes |               | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] |     |

| CoMOV        | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | Yes |               |                                       |     |

#### Table 5MAC Unit Instruction Set Summary.

| CoABS | Absolute Value          | CoABS |

|-------|-------------------------|-------|

| Group | Arithmetic Instructions |       |

Group Arithmetic Instructions

## Syntax CoABS

Source Operand(s)  $ACC \rightarrow 40$ -bit signed value

Destination Operand(s) ACC  $\rightarrow$  40-bit signed value

Operation

$(ACC) \leftarrow Abs(ACC)$

#### Description

Computes the absolute value of the 40-bit ACC contents.

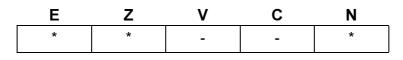

#### **MAC Flags**

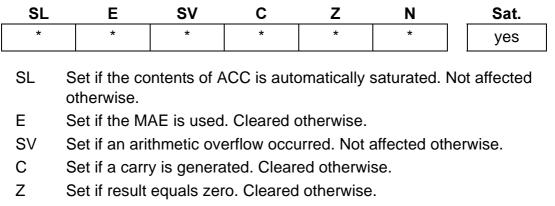

| SL | Е | SV | С | Z | Ν | Sat. |

|----|---|----|---|---|---|------|

| *  | * | *  | 0 | * | * | yes  |

- SL Set if the contents of ACC is automatically saturated. Not affected otherwise.

- E Set if the MAE is used. Cleared otherwise.

- SV Set if the ACC contents was 80 0000 0000H. Not affected otherwise.

- C Always cleared.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.

Note: SV flag behavior has been changed to guarantee arithmetic correctness.

#### Encoding

| Mnemonic | Format      | Repeat |

|----------|-------------|--------|

| CoABS    | A3 00 1A 00 | no     |

| CoABS |  |

|-------|--|

|-------|--|

Absolute Value

# CoABS

Group Arithmetic Instructions

# Syntax CoABS op1, op2

Source Operand(s) op1, op2  $\rightarrow$  WORD

Destination Operand(s) ACC  $\rightarrow$  40-bit signed value

Operation

$(ACC) \leftarrow Abs((op2) || (op1))$

### Description

Computes the absolute value of a 40-bit source operand and loads the result in the 40-bit ACC register. The 40-bit operand is a sign-extended result of the concatenation of the two source operands, op1 (LSW) and op2 (MSW).

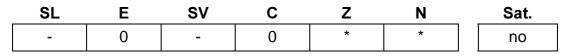

### **MAC Flags**

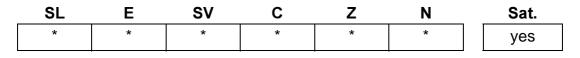

| SL | Е | SV | С | Z | Ν | Sat. |

|----|---|----|---|---|---|------|

| *  | * | -  | 0 | * | * | yes  |

- SL Set if the contents of ACC is automatically saturated. Not affected otherwise.

- E Set if the MAE is used. Cleared otherwise.

- SV Not affected.

- C Always cleared.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.

| Mnemonic |                                       | Format          | Repeat |

|----------|---------------------------------------|-----------------|--------|

| CoABS    | Rw <sub>n</sub> , Rw <sub>m</sub>     | A3 nm CA 00     | no     |

| CoABS    | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] | 83 nm CA 0:0qqq | no     |

| CoABS    | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | 93 Xm CA 0:0qqq | no     |

# CoADD

Add

CoADD

Group Arithmetic Instructions

# Syntax CoADD op1, op2

Source Operand(s) op1, op2  $\rightarrow$  WORD

Destination Operand(s) ACC  $\rightarrow$  40-bit signed value

### Operation

$(tmp) \leftarrow (op2) \mid\mid (op1)$  $(ACC) \leftarrow (ACC) + (tmp)$

### Description

Adds a 40-bit operand to the 40-bit ACC register contents and stores the result in the ACC register. The 40-bit operand is a sign-extended result of the concatenation of the two source operands, op1 (LSW) and op2 (MSW). This instruction is repeatable with indirect addressing modes and allows up to two parallel memory reads.

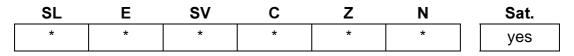

### MAC Flags

| SL | E                           | SV           | С           | Z          | Ν            | Sat.         |

|----|-----------------------------|--------------|-------------|------------|--------------|--------------|

| *  | *                           | *            | *           | *          | *            | yes          |

| SL | Set if the co<br>otherwise. | ontents of A | ACC is auto | omatically | saturated. N | Not affected |

- E Set if the MAE is used. Cleared otherwise.

- SV Set if an arithmetic overflow occurred. Not affected otherwise.

- C Set if a carry is generated. Cleared otherwise.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.

| Mnemonic |                                       | Format             | Repeat |

|----------|---------------------------------------|--------------------|--------|

| CoADD    | Rw <sub>n</sub> , Rw <sub>m</sub>     | A3 nm 02 00        | no     |

| CoADD    | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] | 83 nm 02 rrrr:rqqq | yes    |

| CoADD    | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | 93 Xm 02 rrrr:rqqq | yes    |

# CoADD2

Add

CoADD2

Group Arithmetic Instructions

Syntax CoADD2 op1, op2

Source Operand(s) op1, op2  $\rightarrow$  WORD

Destination Operand(s) ACC  $\rightarrow$  40-bit signed value

Operation

$\begin{array}{l} (tmp) \leftarrow 2 * ((op2) \mid\mid (op1)) \\ (ACC) \leftarrow (ACC) + (tmp) \end{array}$

### Description

Adds a 40-bit operand to the 40-bit ACC register contents and stores the result in the ACC register. The 40-bit operand is a sign-extended result of the concatenation of the two source operands, op1 (LSW) and op2 (MSW). The 40-bit operand is then multiplied by two before being added to ACC register. This instruction is repeatable with indirect addressing modes and allows up to two parallel memory reads.

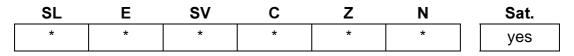

### **MAC Flags**

| SL | Е | SV | С | Z | Ν | Sat. |

|----|---|----|---|---|---|------|

| *  | * | *  | * | * | * | yes  |

- SL Set if the contents of ACC is automatically saturated. Not affected otherwise.

- E Set if the MAE is used. Cleared otherwise.

- SV Set if an arithmetic overflow occurred. Not affected otherwise.

- C Set if a carry is generated. Cleared otherwise.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.

| Mnemonic |                                       | Format             | Repeat |

|----------|---------------------------------------|--------------------|--------|

| CoADD2   | Rw <sub>n</sub> , Rw <sub>m</sub>     | A3 nm 42 00        | no     |

| CoADD2   | Rw <sub>n</sub> , [Rw <sub>m</sub> ⊗] | 83 nm 42 rrrr:rqqq | yes    |

| CoADD2   | [IDXi⊗], [Rw <sub>m</sub> ⊗]          | 93 Xm 42 rrrr:rqqq | yes    |

| _                  | Accumulator Arithmetic Shift Right with Round <b>CoASHR</b>                                                                |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|

| Group              | Shift Instructions                                                                                                         |

| Syntax             | CoASHR op1, rnd                                                                                                            |

| Source Operand(s)  | op1 $\rightarrow$ shift counter                                                                                            |

| Destination Operar | nd(s) ACC $\rightarrow$ 40-bit signed value                                                                                |

| END WH             | $LE (count) \neq 0$ $(ACC[n]) \leftarrow (ACC[n+1]) [n=0-38]$ $(count) \leftarrow (count) -1$ $HLE$ $- (ACC) + 0000 8000h$ |

| Description        |                                                                                                                            |

Arithmetically shifts the ACC register right by the number of bits as specified by operand op1. Then the obtained result is 2's complement rounded before being stored in the 40-bit ACC register. To preserve the sign of the ACC register, the most significant bits of the result are filled with sign 0 if the original most significant bit was a 0 or with sign 1 if the original most significant bit was 1. Only shift values from 0 to 8 (inclusive) are allowed. op1 can be either a 4-bit unsigned immediate data or the 4 least significant bits (considered as unsigned data) of a directly or indirectly addressed operand.

| SL | Е                                                                        | SV           | С           | Z          | Ν            | Sat.         |  |

|----|--------------------------------------------------------------------------|--------------|-------------|------------|--------------|--------------|--|

| *  | *                                                                        | *            | *           | *          | *            | yes          |  |

| SL | Set if the co<br>otherwise.                                              | ontents of A | ACC is auto | omatically | saturated. N | lot affected |  |

| Е  | Set if the M                                                             | AE is used   | . Cleared o | otherwise. |              |              |  |

| SV | Set if an arithmetic overflow occurred. Not affected otherwise.          |              |             |            |              |              |  |

| С  | Set if a carry is generated when rounding. Cleared otherwise.            |              |             |            |              |              |  |

| Z  | Set if result equals zero. Cleared otherwise.                            |              |             |            |              |              |  |

| Ν  | Set if the most significant bit of the result is set. Cleared otherwise. |              |             |            |              |              |  |

# User's Manual C166S V1 MAC Unit

### **MAC Unit Instruction Set**

| Mnemonic |                          | Format             | Repeat |

|----------|--------------------------|--------------------|--------|

| CoASHR   | #data4, rnd              | A3 00 B2 0sss:s000 | no     |

| CoASHR   | Rw <sub>n</sub> , rnd    | A3 nn BA rrrr:r000 | yes    |

| CoASHR   | [Rw <sub>m</sub> ⊗], rnd | 83 mm BA rrrr:rqqq | yes    |

| CoASHR<br>Group     | Accumulator Arithmetic Shift Right<br>Shift Instructions                   | CoASHR |

|---------------------|----------------------------------------------------------------------------|--------|

| Syntax              | CoASHR op1                                                                 |        |

| Source Operand(s)   | op1 $\rightarrow$ shift counter                                            |        |

| Destination Operanc | $ACC \rightarrow 40$ -bit signed value                                     |        |

| (/                  | E (count) $\neq$ 0<br>ACC[n]) ← (ACC[n+1]) [n=0-38]<br>count) ← (count) -1 |        |

### Description

Arithmetically shifts the ACC register right by the number of bits as specified by operand op1. To preserve the sign of the ACC register, the most significant bits of the result are filled with sign 0 if the original most significant bit was a 0 or with sign 1 if the original most significant bit was 1. Only shift values from 0 to 8 (inclusive) are allowed. op1 can be either a 4-bit unsigned immediate data or the 4 least significant bits (considered as unsigned data) of a directly or indirectly addressed operand. The MS bit of the MCW register does not affect the result.

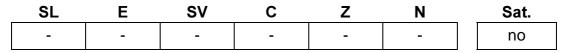

| SL | Е | SV | С | Z | Ν | Sat. |

|----|---|----|---|---|---|------|

| -  | * | -  | 0 | * | * | no   |

- SL Not affected.

- E Set if the MAE is used. Cleared otherwise.

- SV Not affected.

- C Always cleared.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.

| Mnemonic |                     | Format             | Repeat |

|----------|---------------------|--------------------|--------|

| CoASHR   | #data4              | A3 00 A2 0sss:s000 | no     |

| CoASHR   | Rw <sub>n</sub>     | A3 nn AA rrrr:r000 | yes    |

| CoASHR   | [Rw <sub>m</sub> ⊗] | 83 mm AA rrrr:rqqq | yes    |

# CoCMP

CoCMP

Compare

Group Compare Instructions

Syntax CoCMP op1, op2

$Source \ Operand(s) \qquad \quad op1, \ op2 \rightarrow WORD$

Destination Operand(s) none

Operation

$tmp \leftarrow (op2) || (op1)$  $(ACC) \Leftrightarrow (tmp)$

### Description

Subtracts a 40-bit signed operand from the 40-bit ACC contents and updates the N, Z and C flags of the MSW register leaving the ACC register unchanged. The 40-bit operand is a sign-extended result of the concatenation of the two source operands, op1 (LSW) and op2 (MSW). The MS bit of the MCW register does not affect the result. This instruction allows up to two parallel memory reads.

### **MAC Flags**

- E Not affected.

- SV Not affected.

- C Set if a borrow is generated. Cleared otherwise.

- Z Set if result equals zero. Cleared otherwise.

- N Set if the most significant bit of the result is set. Cleared otherwise.