# **Errata Sheet**

V1.1, 2005-09-23

Device C164SV-2R

Marking/Step Step (E)ES-AA, AA

Package P-TQFP-64

This Errata Sheet describes the deviations from the current user documentation.

The module oriented classification and numbering system uses an ascending sequence over several derivatives, including already solved deviations. So gaps inside this enumeration can occur.

#### **Current Documentation**

- C164SV Data Sheet V1.0, Apr. 2003

- C164CM/SM User's Manual, V1.0, Feb. 2002

- Instruction Set Manual, V2.0, Mar. 2001

Note: Devices marked with EES- or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only. The specific test conditions for EES and ES are documented in a separate Status Sheet.

Note: For simplicity all versions are referred to by the term C164SV-2R throughout this document.

#### Contents

| section                                              | Page |

|------------------------------------------------------|------|

| listory List/Change Summary                          | 2    |

| unctional Problems                                   | 4    |

| Peviations from Electrical- and Timing Specification | 15   |

| application Hints                                    | 16   |

| Occumentation Update                                 | 21   |

# **History List/Change Summary**

# 1 History List/Change Summary

(from step AA, previous errata sheet: V1.0, step: AA)

# Table 1 Functional Deviations

| Functional<br>Problem | Short Description                                   | Fixed in step | Change |

|-----------------------|-----------------------------------------------------|---------------|--------|

| ADC.11                | Modifications of ADM field while bit ADST = 0       |               |        |

| SSC.9                 | Data Transmission in Slave Mode                     |               | new    |

| CAPCOM6.4             | Spike when enabling alternate Port Function         |               |        |

| X9                    | Read Access to XPERs in Visible Mode                |               |        |

| CPU.22                | Z Flag after PUSH and PCALL                         |               |        |

| PLL.3.6               | Increased PLL Jitter caused by external Access      |               |        |

| PWRDN.1               | Execution of PWRDN instruction while Pin NMI = high |               |        |

| ADCC.2.10             | ADC Overload Current                                |               |        |

# Table 2 AC/DC Deviations

| AC/DC<br>Deviations | Short Description   | Fixed in step | Change |

|---------------------|---------------------|---------------|--------|

|                     | no deviations found |               |        |

# **History List/Change Summary**

# Table 3 Application Hints

| Hint       | Short Description                                                 | Change |

|------------|-------------------------------------------------------------------|--------|

| SSC.H1     | Handling of the SSC Busy Flag (SSCBSY)                            |        |

| SSC.H2     | Timing of flag SSCTIR (SSC Transmit Interrupt Request)            |        |

| EMUL.H1    | Adapt Mode Setting                                                |        |

| INT.H1     | Substitution of CC28IC CC31IC by CC8IC CC11IC                     |        |

| BSL.H1     | Bootstrap Loader: Baudrate Detection in Single Chip Boot Mode     |        |

| MainOsc.H1 | Oscillator Type_LP2: Negative Resistance and Start-up Reliability |        |

| MainOsc.H2 | Maximum (Type_LP2) Oscillator Frequency = 16 MHz                  |        |

| OWD.H2     | Oscillator Watchdog and Prescaler Mode                            |        |

| ISNC.H1    | Maintenance of ISNC Register                                      |        |

# Table 4 Documentation Update

| Name         | Short Description                                | Change |

|--------------|--------------------------------------------------|--------|

| C164SV.D1    | Functionality Comparison C164SV-2R vs. C164CM-4R |        |

| ADC.D1       | 12-bit ADC Extensions                            |        |

| PLL.D1       | PLL goes to Unlocked State after Configuration   | new    |

| ID-Registers | ID-Registers                                     | new    |

# 2 Functional Problems

## ADC.11 Modifications of ADM field while bit ADST = 0

The A/D converter may unintentionally start one auto scan single conversion sequence when the following sequence of conditions is true:

- the A/D converter has finished a fixed channel single conversion of an analog channel n > 0 (i.e. contents of ADCH (ADCON.3-0) = n during this conversion)

- 2. the A/D converter is idle (i.e. ADBSY (ADCON.8) = 0)

- 3. then the conversion mode in the ADC Mode Selection field ADM (ADCON.5-4) is changed to Auto Scan Single (ADM = 10<sub>B</sub>) or Continuous (ADM = 11<sub>B</sub>) mode without setting bit ADST = 1 with the same instruction

Under these conditions, the A/D converter will unintentionally start one auto scan single conversion sequence, beginning with channel n-1, down to channel number 0.

When no interrupt or PEC is servicing the A/D Conversion Complete Interrupt, interrupt request flag ADCIR (ADCIC.7) will be set, and for n > 1 also the A/D Overrun Error interrupt request flag will be set, unless the wait for ADDAT read mode had been selected. When ADWR (ADCON.9) = 1 (wait for ADDAT read), the converter will wait after 2 conversions until ADDAT is read.

In case the channel number ADCH has been changed before or with the same instruction which selected the auto scan mode, this channel number has no effect on the unintended auto scan sequence (i.e. it is not used in this auto scan sequence).

#### Note:

When a conversion is already in progress, and then the configuration in register ADCON is changed,

- the new conversion mode in ADM is evaluated after the current conversion

- the new channel number in ADCH and new status of bit ADST are evaluated after the current conversion when a conversion in fixed channel conversion mode is in progress, and after the current conversion sequence (i.e. after conversion of channel 0) when a conversion in an auto scan mode is in progress.

In this case, it is a specified operational behaviour that channels n-1 .. 0 are converted when ADM is changed to an auto scan mode while a fixed channel conversion of channel n is in progress (see e.g. C164Cl User's Manual, V1.0, p.18-4)

## Workaround:

When an auto scan conversion is to be performed, always start the A/D converter with the same instruction which sets the configuration in register ADCON.

#### SSC.9 Data Transmission in Slave Mode

During data reception in slave mode of the SSC module, sporadically the shift clock supplied by the external master on pin SCLK may not be properly recognized due to a synchronization problem when all of the following conditions are true:

- the latching edge for the serial data is the falling edge of SCLK (i.e. both bit SSCPO = 1 and bit SSCPH = 1, or SSCPO = 0 and SSCPH = 0 in register SSCCON), and

- the transmit buffer SSCTB of the slave has not been written prior to the start of the reception (initiated by the master asserting the shift clock SCLK), and

- 3. a specific time window (phase delay) is hit by the serial shift clock SCLK in relation to the internal system clock of the slave. Therefore, this synchronization problem will occur in particular when the slave device is clocked (on XTAL1) by an external clock generation circuit which is independent from the clock generation circuit of the master (i.e. slave and master clocks are asynchronous).

When the problem occurs, this results in missing bits in the character received in SSCTB, and in duplicated bits in the character transmitted on pin MRST of the slave. As a consequence, interrupt generation in the slave is delayed by the number of missed bits.

#### Workaround

For systems using the falling edge of SCLK as latching edge (see condition 1. above), always write to the transmit buffer SSCTB prior to any reception in slave mode of the SSC module. For the second and all following characters, e.g. write a (dummy) character to SSCTB in the receive interrupt routine, or use a PEC transfer triggered by the transmit interrupt request to write to SSCTB. In this case, the critical synchronization path is not used, and the problem will not occur.

# **CAPCOM6.4** Spike when enabling alternate Port Function

When switching a port from I/O mode to compare mode during the low state of the PWM by setting bits in register CC6MSEL, a spike is generated for one TCL before the PMW signal starts.

#### Workaround:

When the port configuration is changed during the high phase of the compare output the spike is suppressed. Two different interrupts can be used for this synchronization depending on the initial value bits in the register CC6MCON (CCxI and COUTxI represent the passive output level for the enabled compare channels). The first high

phase of the PWM signal is delayed by the corresponding interrupt latency and the execution time of the necessary instructions:

- If the initial value is 0, the compare interrupt service routine switches the port to compare output. So the spike is pushed in the high phase of the PWM.

- If the initial value is 1, the Timer 12 period match interrupt service routine switches the port to compare mode with the same result.

## X9 Read Access to XPERs in Visible Mode

The data of a read access to an XBUS-Peripheral (CAN) in Visible Mode (SYSCON.1 = 1) is not driven to the external bus. PORT0 is tristated during such read accesses.

Note that in Visible Mode PORT1 will drive the address for an access to an XBUS-Peripheral, even when only a multiplexed external bus is enabled.

# CPU.22 Z Flag after PUSH and PCALL

The Z flag in the PSW is erroneously set to '1' by **PUSH reg** or **PCALL reg, rel** instructions when all of the following conditions are true:

## a) for **PUSH reg** instructions:

- the contents of the high byte of the GPR or (E)SFR which is pushed is 00<sub>H</sub>, and

- the contents of the low byte of the GPR or (E)SFR which is pushed is > 00<sub>H</sub>, and

- the contents of GPR Rx is odd, where x = 4 msbs of the 8-bit 'reg' address of the pushed GPR or (E)SFR

#### **Examples:**

```

PUSH R1 ;(coding: F1 EC):

; incorrect setting of Z flag if contents of R15 is odd,

; and 00FFh ≥ contents of R1 ≥ 0001h

PUSH DPP3 ;(coding: 03 EC):

; incorrect setting of Z flag if contents of R0 is odd,

; and 00FFh ≥ contents of DPP3 ≥ 0001h

```

## b) for **PCALL reg, rel** instructions:

- when the contents of the high byte of the GPR or SFR which is pushed is 00<sub>H</sub>, and

- when the contents of the low byte of the GPR or SFR which is pushed is odd

This may lead to wrong results of instructions following PUSH or PCALL if those instructions explicitly (e.g. BMOV .. , Z; JB Z, ..; ..) or implicitly (e.g. JMP cc\_Z, ..; JMP cc\_NET, ..; ..) evaluate the status of the Z flag before it is newly updated.

Note: Some instructions (e.g. CALL, ...) have no effect on the status flags, such that the status of the Z flag remains incorrect after a PUSH/PCALL instruction until an instruction that correctly updates the Z flag is executed.

## Example:

#### Effect on Tools:

- The Hightec C166 tools (all versions) don't use the combination of PUSH/PCALL and the evaluation of the Z flag. Therefore, these tools are not affected.

- The code generated by the Keil C166 Compiler evaluates the Z flag only after MOV, CMP, arithmetic, or logical instructions. It is never evaluated after a PUSH instruction.

PCALL instructions are not generated by the C166 Compiler.

This has been checked with all C166 V3.xx and V4.xx compiler versions. Even the upcoming V5.xx is not affected by the CPU.22 problem.

The assembler portions of the C166 V3.xx and V4.xx Run-Time Libraries, the RTX166 Full and TX166 Tiny Real Time Operating system do also not contain any evaluation of the Z flag after PUSH or PCALL.

The TASKING compiler V7.5r2 never generates a PCALL instruction, nor is it used in the libraries.

The PUSH instruction is only used in the entry of an interrupt frame, and sometimes on exit of normal functions. The zero flag is not a parameter or return value, so this does not give any problems.

Previous versions of TASKING tools:

V3.x and higher are not affected, versions before 3.x are most likely not affected. Contact TASKING when using versions before V3.x.

Since code generated by the C166 compiler versions mentioned before is not affected, analysis and workarounds are only required for program parts written in assembler, or instruction sequences inserted via inline assembly.

## Workaround (for program parts written in assembler):

Do not evaluate the status of the Z flag generated by a PUSH or PCALL instruction. Instead, insert an instruction that correctly updates the PSW flags, e.g.

#### or

```

PCALL reg, procedure_1

...

procedure_1:

MOV   ONES, reg

JMPR   cc_NET, label_1 ; implicitly tests flags Z and E

```

#### Hints for Detection of Critical Instruction Combinations

Whether or not an instruction following PUSH reg or PCALL reg, rel actually causes a problem depends on the program context.

In most cases, it will be sufficient to just analyze the instruction following PUSH or PCALL. In case of PCALL, this is the instruction at the call target address.

# Support Tool for Analysis of Hex Files

For complex software projects, where a large number of assembler source (or list) files would have to be analyzed, Infineon provides a tool aiScan22 which scans hex files for critical instruction sequences and outputs diagnostic information. This tool is available as part of the Application Note ap1679 'Scanning for Problem CPU.22' on the 16-bit microcontroller internet pages of Infineon Technologies.

Follow the link: 'Application Notes - 16-bit Microcontrollers' in:

www.infineon.com/16-bit-microcontrollers

## **Individual Analysis of Assembler Source Code**

With respect to problem CPU.22, all instructions of the C166 instruction set can be classified into the following groups:

Arithmetic/logic/data movement instructions as successors of PUSH/PCALL (correctly) modify the condition flags in the PSW according to the result of the operation.

These instructions may only cause a problem if the PSW is a source or source/ destination operand:

ADD/B, ADDC/B, CMP/B, CMPD1/2, CMPI1/2, SUB/B, SUBC/B

AND/B, OR/B, XOR/B

**ASHR**

MOV/B. MOVBZ/MOVBS

**SCXT**

PUSH, PCALL → analysis must be repeated for successor of PUSH/PCALL

The following instructions (most of them with immediate or register (Rx) addressing modes) can never cause a problem:

CPL/B, NEG/B

DIV/U, DIVL/U, MUL/U

SHL/SHR, ROL/ROR

PRIOR

POP

RETP

updates condition flags

PWRDN → program restarts after reset

SRST → program restarts

Conditional branch instructions which may evaluate the Z flag:

JB/JNB Z, rel; directly evaluates Z flag

CALLA/CALLI, JMPA/JMPI/JMPR with the following condition codes

cc Z, cc EQ, cc NZ, cc NE

cc ULE, cc UGT, cc SLE, cc SGT

cc NET

- → For these branch conditions, the branch may be performed in the wrong way.

- → For other branch conditions, the branch target as well as the linear successor of the branch instruction must be analyzed (since these branch instruction don't modify the PSW flags).

- For instructions that have no effect on the condition flags and that don't evaluate the Z flag, the instruction that follows this instruction must be analyzed.

These instructions are:

NOP

ATOMIC, EXTxx

DISWDT, EINIT, IDLE, SRVWDT

CALLR, CALLS, JMPS → branch target must be analyzed

RET, RETS → return target must be analyzed

(value pushed by PUSH/PCALL = return IP, Z flag contains information whether intra-segment target address = 0000<sub>H</sub> or not)

TRAP → both trap target and linear successor must be analyzed, since Z flag may be incorrect in PSW on stack as well as in PSW at entry of trap routine

• For **bit modification instructions**, the problem may only occur if a source bit is the Z flag, and/or the destination bit is in the PSW, but not the Z flag.

These instructions are:

BMOV/BMOVN

BAND/BOR/BXOR

**BCMP**

BFLDH

BFLDL → problem only if bit 3 of @@ mask = 0, i.e. if Z is not selected

BCLR/BSET → problem only if operand is not Z flag

JBC/JNBS → wrong branch if operand is Z flag

# PLL.3.6 Increased PLL Jitter caused by external Access

## Problem description:

In systems were the PLL is used for generation of the CPU clock frequency, the PLL jitter can increase in certain circumstances and exceed the specified value.

The value of the additional jitter is not a fixed one but it depends on the kind of activity on the external bus or output pins. The additional jitter increases with the number of output/bus pins which are switched at the same time to a new voltage level because the problem is caused by noise on the on-chip power supply.

The capacitive load of the used pins has also an influence to the additional jitter. A high capacitive load can increase the additional jitter.

# Effects to the system:

All PLL factors are affected (PLL factor 1,5 / 2 / 2,5 / 3 / 4 / 5). The PLL jitter increases when access to the external bus or output pins is performed. This phenomenon has no influence to direct drive- prescaler- and SDD mode.

The problem does not affect the functionality of the CPU and the on-chip peripherals.

The additional jitter has the maximum effect if only one TCL is considered (period jitter). This can have an influence to the bus timings with one TCL.

The additional jitter decreases with the number of consecutive TCLs (accumulated jitter). The accumulated jitter has an effect on timings with more than one TCL (certain bus timings, CAN bus timing, serial interface).

## Value of the additional jitter:

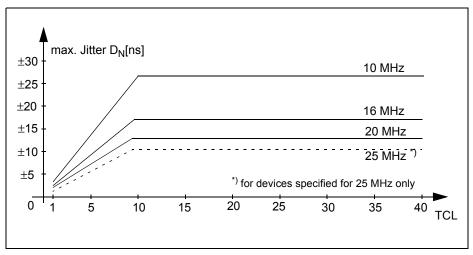

For an accumulated period of N\*TCL the new maximum jitter  $D_N[ns]$ , which exceeds the specified value in the Data Sheet, is computed using the formula:

$$D_N[ns] = \pm (266 / f_{CPU}) * N / T_m$$

Were N = number of consecutive TCL,  $f_{CPU}$  = CPU frequency in MHz and  $T_m$  = 11.3 -  $f_{CPU}$  \* 0.13. This approximated formula is valid for a CPU frequency 10 MHz  $\leq f_{CPU} \leq$  20 MHz with the conditions:

$$T_m = 11.3 - f_{CPU} * 0.13$$

for  $N \le T_m$

$T_m = N$  for  $N > T_m$

The accumulated jitter is in the specified range for accumulated periodes longer than N = 40 TCL.

Figure 1 Additional Jitter

#### Workaround:

In the case that the additional jitter causes problems in the system which cannot be relaxed with software adapted timing parameters the following workarounds are possible:

- If the clock generation is done with the on-chip oscillator then direct drive- or prescaler mode can be used.

- If the maximum frequency of the on-chip oscillator in not sufficient then an external clock generator can be used.

# PWRDN.1 Execution of PWRDN Instruction while pin $\overline{NMI}$ = high

When instruction PWRDN is executed while pin \( \overline{NMI} \) is at a high level, power down mode should not be entered, and the PWRDN instruction should be ignored. However, under the conditions described below, the PWRDN instruction may not be ignored, and no further instructions are fetched from external memory, i.e. the CPU is in a quasi-idle state. This problem will only occur in the following situations:

- a) the instructions following the PWRDN instruction are located in external memory, and a multiplexed bus configuration with memory tristate waitstate (bit MTTCx = 0) is used, or b) the instruction preceding the PWRDN instruction writes to external memory or an XPeripheral (e.g. CAN or XRAM), and the instructions following the PWRDN instruction are located in external memory. In this case, the problem will occur for any bus

- APeripheral (e.g. CAN or XRAM), and the instructions following the PWRDN instruction are located in external memory. In this case, the problem will occur for any bus configuration.

Note: The on-chip peripherals are still working correctly, in particular the Watchdog

Note: The on-chip peripherals are still working correctly, in particular the Watchdog Timer will reset the device upon an overflow. Interrupts and PEC transfers, however, can not be processed. In case NMI is asserted low while the device is in this quasi-idle state, power down mode is entered.

#### Workaround:

Ensure that no instruction which writes to external memory or an XPeripheral preceeds the PWRDN instruction, otherwise insert e.g. a NOP instruction in front of PWRDN. When a muliplexed bus with memory tristate waitstate is used, the PWRDN instruction should be executed out of internal RAM.

## ADCC.2.10 ADC Overload Current

During exceptional conditions in the application system an overload current  $I_{OV}$  can occur on the analog inputs of the A/D converter when  $V_{AIN}$  >  $V_{DD}$  + 0.5 V or  $V_{AIN}$  <  $V_{SS}$  - 0.5 V. For this case, the following conditions are specified in the Data Sheet:

$I_{OVmax} = | \pm 5 \text{ mA} |$

The specified total unadjusted error  $TUE_{max} = | \pm 2 LSB |$  is only guaranteed if the

absolute sum of input overload currents on Port5 pins does not exceed 10 mA.

Due to an internal problem, the specified TUE value is only met for a **positive** overload current 0 mA  $\leq$  I<sub>OV</sub>  $\leq$  +5 mA (all currents flowing into the microcontroller are defined as positive and all currents flowing out of it are defined as negative).

If the exceptional conditions in the application system cause a **negative** overload current, then the maximum TUE can be exceeded (depending on value of  $I_{OV}$  and  $R_{AREF}$ ):

## **Problem Description in Detail:**

# Overload Current at Analog Channel AN(0, 1, 4 - 7) and Influence to V<sub>AREF</sub>

If a **negative** overload current  $I_{OV}$  occurs on analog input channel AN(0, 1, 4 - 7) then an additional current  $I_{ARFF}$  (crosstalk current) is caused at pin  $V_{ARFF}$ .

Depending on  $R_{AREF}$ , the resistance between voltage reference and input  $V_{AREF}$ , the crosstalk current  $I_{AREF}$  at pin  $V_{AREF}$  can cause an additional unadjusted error AUE to all other analog channels.

# 1.1 Overload Current at Analog Channel AN0

In case  $R_{AREF} \le 610$  Ohm  $[R_{AREF} \le ((LSB_{10}/2) / (|I_{OVmax}| * ovf-3.1)]$  the maximum possible additional error to all other channels is smaller than 0.5 LSB<sub>10</sub> with the condition of  $I_{OVmax} = |-5 \text{ mA}|$  at ANO.

Relation between I<sub>AREE</sub> and I<sub>OV</sub> at AN0:

$$I_{ARFF} = \text{ovf-3.1} * I_{OVO}$$

# 1.2 Overload Current at Analog Channel AN(1, 4 - 7)

In case  $R_{AREF} \leq$  1400 Ohm  $[R_{AREF} \leq ((LSB_{10}/2) / (|I_{OVmax}| * ovf-3.2)]$  the maximum possible additional error to all other channels is smaller than 0.5 LSB<sub>10</sub> with the condition of  $I_{OVmax} = |-5 \text{ mA}|$  at AN(1, 4 - 7).

Relation between  $I_{AREF}$  and  $I_{OV}$  at AN(1, 4 - 7):

$$I_{AREF} = ovf-3.2 * I_{OVn}$$

(n = 1, 4 - 7)

Note: The influence to the reference voltage  $V_{AREF}$  caused by  $I_{OV}$  (shift of  $V_{AREF}$ ) is maximum for  $V_{AIN} = V_{AREF}$  and the influence is minimum for  $V_{AIN} = 0V$ . The conditions  $R_{AREF} \le 610$  Ohm @ 0.5 LSB<sub>10</sub> and  $R_{AREF} \le 1400$  Ohm @ 0.5 LSB<sub>10</sub> are calculated for the worst case at  $V_{AIN} = V_{AREF}$ .

In standard systems the typical value for  $R_{AREF}$  is less than 10 Ohm. In that case the  $V_{AREF}$  shift error is **negligible**!

#### 2 Values of ovf-3.1 and ovf-3.2

| Parameter           | Symbol  | Min       | Max |  |

|---------------------|---------|-----------|-----|--|

| Overload factor-3.1 | ovf-3.1 | - 0.0008  | 0   |  |

| Overload factor-3.2 | ovf-3.2 | - 0.00035 | 0   |  |

These Values are the absolute maximum values measured in the lab and not tested!

# **Deviations from Electrical- and Timing Specification**

# 3 Deviations from Electrical- and Timing Specification

| Problem    | Parameter           | Symbol | Limit | Values | Unit |           |

|------------|---------------------|--------|-------|--------|------|-----------|

| Short Name |                     |        | min.  | max.   |      | Condition |

|            | no deviations found |        |       |        |      |           |

# 4 Application Hints

## SSC.H1 Handling of the SSC Busy Flag (SSCBSY)

In master mode of the High-Speed Synchronous Serial Interface (SSC), when register SSCTB has been written, flag SSCBSY is set to '1' when the baud rate generator generates the next internal clock pulse. The maximum delay between the time SSCTB has been written and flag SSCBSY=1 is up to 1/2 bit time. SSCBSY is cleared 1/2 bit time after the last latching edge.

When polling flag SSCBSY after SSCTB has been written, SSCBSY may not yet be set to '1' when it is tested for the first time (in particular at lower baud rates). Therefore, e.g. the following alternative methods are recommended:

test flag SSCRIR (receive interrupt request) instead of SSCBSY (in case the receive interrupt request is not serviced by CPU interrupt or PEC), e.g.

use a software semaphore bit which is set when SSCTB is written and is cleared in the SSC receive interrupt routine

# SSC.H2 Timing of flag SSCTIR (SSC Transmit Interrupt Request)

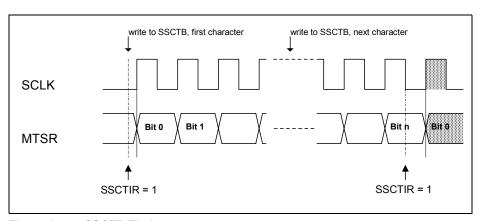

In master mode, the timing of SSCTIR is as follows:

When SSCTB has been written while the transmit shift register was empty (and the SSC is enabled), flag SSCTIR is set to '1' directly after completion of the write operation, independent of the selected baud rate. When the transmit shift register is not empty when SSCTB was written, SSCTIR is set to '1' after the last latching edge of SCLK (= 1/2 bit time before the first shifting edge of the next character). See also e.g. C167CR User's Manual V3.1, p. 12-5.

The following diagram shows these relations in an example for a data transfer in master mode with SSCPO = 0 and SSCPH = 0. It is assumed that the transmit shift register is empty at the time the first character is written to SSCTB:

Figure 2 SSCTB Timing

Typically, in interrupt driven systems, no problems are expected from the modified timing of flag SSCTIR. However, when flag SSCTIR is polled by software in combination with other flags which are set/cleared at the end or at the beginning of a transfer (e.g. SSCBSY), the modified timing may have an effect.

Another situation where a different system behaviour may be noticed is the case when only one character is transferred by the PEC into the transmit buffer register SSCTB. In this case, 2 interrupt requests from SSCTIR are expected: the 'PEC COUNT = 0' interrupt, and the 'SSCTB empty' interrupt:

When the PEC transfer is performed with sufficient margin to the next clock tick from the SSC baud rate generator, and no higher priority interrupt request has occurred in the meantime, the 'PEC COUNT = 0' interrupt will be acknowledged before the 'SSCTB empty' interrupt request is generated, i.e. two interrupts will occur based on these events. However, when the PEC transfer takes place relatively close before the next clock tick from the SSC baud rate generator, or a higher priority interrupt request has occurred while the PEC transfer is performed, the 'PEC COUNT = 0' interrupt may not be acknowledged before the 'SSCTB empty' interrupt request is generated, such that effectively only one interrupt request will be generated for two different events.

In order to achieve a defined and systematic behavior with all device steps, the SSC receive interrupt, which is generated at the end of a character transmission, may be used instead of the SSC transmit interrupt.

# **EMUL.H1** Adapt Mode setting for emulation of devices in Single Chip Mode

In Adapt Mode all target device pins are in high impedance state. This mode is mainly used for deactivation of the soldered device while an emulator probe is connected. In single chip mode ( $\overline{EA}$  = 1) Adapt Mode can not be selected via PORT0 (P0L.1) during reset, because PORT0 is not evaluated in this mode.

#### Recommendation:

- use no target device or a dummy device (package without silicon on the PCB) for emuation or

- use the target device on the PCB and:

- provide a possibility to set target device pins EA and P0L.1 to "0" during reset (now the adapt mode is enabled on the target device) and

- disconnect pin EA from the emulator probe and

- set the EA pin on the emulator-probe to "1" to configure the emulator in single chip mode.

# INT.H1 Substitution of CC28IC ... CC31IC by CC8IC ... CC11IC

Due to the fact that CC28 ... 31 and fast external interrupts 0 ... 3 share the same pins the missing interrupt nodes can be replaced:

Instead of the missing interrupt nodes for the CAPCOM registers 28 ... 31 the fast external interrupts 0 ... 3 can be used if the correspondent pin is used as capture input or compare output (compare modes 1 and 3). In this case the interrupt requesting edge is selected in register EXICON, interrupt enable and level in register CC8IC ... CC11IC. The dedicated interrupt vectors are CC8INT ... CC11INT, see Data Sheet Table 3 on page 17.

# **BSL.H1** Bootstrap Loader: Baudrate Detection in Single Chip Boot Mode

In single chip boot mode (Pin  $\overline{EA}$  = 1) the bootstrap loader mode is detected during hardware reset when pin  $\overline{RD}$  is tied to low.

In this mode  $f_{\text{CPU}} = f_{\text{OSC}}$  / 2 (default configuration) and can be controlled via register RSTCON. In case of a desired PLL mode (e.g. with a PLL factor of 5),  $f_{\text{CPU}}$  in bootstrap loader mode is 10 times slower than in normal running mode. So a communication with an external host starts with a baudrate related to  $f_{\text{CPU}} = f_{\text{OSC}}$  / 2. It is recommended to establish a 2nd level loader which adapts  $f_{\text{CPU}}$  and baudrate to a convenient transmission rate.

# <u>MainOsc.H1</u> Main Oscillator Type\_LP2: Negative Resistance and Start-up Reliability

Compared to other C16x microcontrollers the gain of the on-chip oscillator (Type\_LP2) is slightly different. It is recommended to check the negative resistance and the start-up reliability of the oscillator circuit in the original application. Please refer to the limits specified by the guartz crystal or ceramic resonator supplier.

See also Application Note AP2420 'Crystal Oscillator of the C500 and C166 Microcontroller Families' and Application Note AP2424 'Ceramic Resonator Oscillators of the C500 and C166 Microcontroller Families'.

Follow the link: 'Application Notes - 16-bit Microcontrollers' on the 16-bit microcontroller internet pages of Infineon Technologies:

www.infineon.com/16-bit-microcontrollers

## MainOsc.H2 Maximum Oscillator Frequency = 16 MHz (Main: Type\_LP2)

The main oscillator is optimized for oscillation with a crystal within a frequency range of 4...16 MHz. When driven by an external clock signal it will accept the specified frequency range (see Data Sheet, AC Characteristics, tables 'Clock Generation Modes' and 'External Clock Drive Characteristics'). Operation at lower input frequencies is possible but is guaranteed by design only (not 100% tested) (see Data Sheet, AC Characteristics, table 'External Clock Drive Characteristics').

# OWD.H2 Oscillator Watchdog and Prescaler Mode

The OWD replaces a missing oscillator clock signal with the PLL clock signal (base frequency).

In direct drive mode the PLL base frequency is used directly ( $f_{CPU} = 2...5 \text{ MHz}$ ).

In prescaler mode the PLL base frequency is divided by 2 ( $f_{CPU}$  = 1...2.5 MHz).

# ISNC.H1 Maintenance of ISNC register

The RTC and PLL interrupts share one interrupt node (XP3IC). If an interrupt request occurs the request bit in the Interrupt Subnode Control register has to be checked and cleared by software. To avoid a collision with the next hardware interrupt request of

same source it is recommended to clear the request and the enable bit first and then to set the enable bit again.

## Example for an XP3 interrupt service routine (for Tasking C compiler):

## Example for an XP3 interrupt service routine (in assembly language):

```

EXTR

#1

JNB

PLLIR, no pll request

EXTR #2

; no further interruption of this

; sequence possible

BFLDL ISNC, #0Ch, #00h

; clear PLLIE and PLLIR

BSET PLLIE

; set PLLIE

; further actions concerning PLL/OWD

no pll request:

EXTR

JNB RTCIR, no rtc request

EXTR #2 ; no further interruption of this sequence possible

BFLDL ISNC, #03h, #00h ; clear RTCIE and RTCIR

BSET RTCIE

; set RTCIE

; further actions concerning RTC

no_rtc_request:

. . .

```

# 5 Documentation Update

## C164SV.D1 Functionality Comparison C164SV-2R vs. C164CM-4R

As long as no dedicated User's Manual for the C164SV is available the C164CM/SM User's Manual can be used. The differences can be found in **Table 5**:

Table 5 Comparison C164SV-2R vs. C164CM-4R

| Topic                                                          | C164SV-2R                                                 | C164CM-4R,<br>C164CM-4E | C164CM User's<br>Manual V1.0 |

|----------------------------------------------------------------|-----------------------------------------------------------|-------------------------|------------------------------|

| On chip Mask ROM / OTP                                         | 16 Kbytes                                                 | 32 Kbytes               | 32 Kbytes                    |

| On chip internal RAM (IRAM) for data, stack and register banks | 1 Kbytes<br>(00'FA00 <sub>H</sub> 00'FDFF <sub>H</sub> )  | 2 Kbytes                | 2 Kbytes                     |

| Maximum Stack Size (circular stack)                            | 256 Words<br>(00'FBFE <sub>H</sub> 00'FA00 <sub>H</sub> ) | 512 Words               | 512 Words                    |

| A/D Converter Resolution                                       | 10-bit / 12-bit                                           | 10-bit / 12-bit         | 10-bit                       |

| CAN interface                                                  | no                                                        | CAN1                    | CAN1                         |

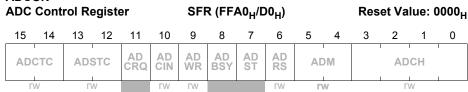

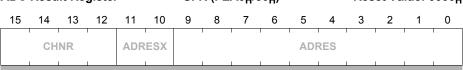

## ADC.D1 12-bit ADC Extensions

The functionality of the ADC has been extended: In addition to the 10-bit conversion a 12-bit conversion mode is implemented. In the following only the new mode and the dedicated bits are described.

The conversion time in 12-bit mode is  $t_{C12}$  = 46  $t_{BC}$  +  $t_{S}$  + 2 $t_{CPU}$

Note: For 12-bit conversions the CPU clock frequency must be limited to  $f_{\text{CPU}} \le 20 \text{ MHz}$  to achieve the specified TUE limits.

# Timing Example for 12-bit Conversion:

Assumptions:  $f_{CPU} = 20 \text{ MHz}$  (i.e.  $t_{CPU} = 50 \text{ ns}$ ), ADCTC =  $00_B$ , ADSTC =  $00_B$ .

Basic clock  $f_{BC} = f_{CPU}/4 = 5.0$  MHz, i.e.  $t_{BC} = 200$  ns.

Sample time  $t_S = t_{BC} \times 8 = 1600 \text{ ns.}$

Conversion 12-bit  $t_{C12} = t_S + 46 t_{BC} + 2 t_{CPU} = (1600 + 9200 + 100) \text{ ns} = 10.9 \mu\text{s}.$

# **Mode Selection and Operation**

## **ADCON**

| Bit  | Function                                                                                                |

|------|---------------------------------------------------------------------------------------------------------|

| ADRS | ADC Resolution Select <sup>1)</sup> 0: Convert with 10-bit resolution 1: Convert with 12-bit resolution |

<sup>1)</sup> Bit ADRS is available only after the execution of instruction EINIT. Before EINIT bit ADCON.6 controls production testmodes and must remain cleared.

# ADDAT ADC Result Register

SFR (FEA0<sub>H</sub>/50<sub>H</sub>)

Reset Value: 0000<sub>H</sub>

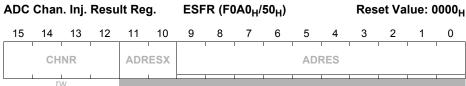

# ADDAT2

| Bit | Function                                                                                                                                         |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

|     | A/D Conversion Result Extension  The lower two bits of the 12-bit digital result of the most recent conversion. Not valid for 10-bit resolution. |

## **Representation of Conversion Results**

Depending on the selected resolution, the digital result of a conversion is represented in the result register(s). The 10 or 12 lower bits of register ADDAT(2) are valid, respectively. For 12-bit conversions the two least significant bits are returned in bits 11 and 10. The lower 10 bits (i.e. bitfield ADRES) always represents the same relative value compared to the full scale result.

A 12-bit conversion result (ADR[11:0]) looks like this:

| 15 | 14 | 13  | 12     | 11       | 10       | 9         | 8         | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|----|----|-----|--------|----------|----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|

|    | CH | INR | I<br>I | ADR<br>1 | ADR<br>0 | ADR<br>11 | ADR<br>10 | ADR<br>9 | ADR<br>8 | ADR<br>7 | ADR<br>6 | ADR<br>5 | ADR<br>4 | ADR<br>3 | ADR<br>2 |

# PLL.D1 PLL goes to Unlocked State after Configuration

When the PLL is (re-)configured via software by writing to register RSTCON, the PLL goes to an unlocked state first (CLKLOCK = SYSCON2.15 = 0) and the PLL interrupt request is set (flag PLLIR = ISNC.3 = 1) in the following cases:

- SW configuration of a PLL mode after single chip mode reset (pin EA is High) when a PLL configuration is selected in bitfield CLKCFG (RSTCON.15 ... 13), i.e. all selections except 001<sub>B</sub> and 011<sub>B</sub>.

- SW re-configuration of a PLL mode in bitfield CLKCFG (RSTCON.15 ... 13), i.e. all selections except 001<sub>B</sub> and 011<sub>B</sub>.

When the PLL is locked again, bit CLKLOCK (SYSCON2.15) is set.

A re-configuration of register RSTCON with the same CLKCFG setting does not influence the PLL.

In direct drive and prescaler mode (bitfield CLKCFG = RSTCON.15  $\dots$  13 = 001<sub>B</sub> or 011<sub>B</sub>) the PLL cannot lock and bit CLKLOCK in register SYSCON2 remains cleared.

Note: If PLLIR is set directly after reset the clock system is running on PLL base frequency (or PLL base frequency / 2) and  $f_{OSC}$  is missing or was unstable during reset. Switching to SDD mode in this state could stop the system.

To avoid an unintentional PLL interrupt during this SW configuration of RSTCON, it is recommended to disable the PLL interrupt while the PLL is in unlocked state.

The example program for PLL modes shown below assumes that instruction EINIT has not been executed yet. After EINIT, unlock sequences must be used to change RSTCON and SYSCON2.

To avoid a deadlock situation, the wait\_for\_CLKLOCK loop should be terminated after a timeout (before the WDT reset occurs).

```

PLLIR, osc clock missing ; no osc clock before configuration

JΒ

; is done, jump to emergency routine,

; don't select SDD mode!

disable PLL interrupt:

EXTR #2

BCLR XP3IE

; disabled by default after reset

BCLR PLLIE

; ISNC.3, disabled by default after reset

change_PLL_configuration:

R4, #0000110100000000b; PLL * 2.5, no CS, no SEG addr. lines

MOV

RSTCON, R4

; memory addressing mode only

EXTR #2

; (after EINIT unlock sequences are

required for RSTCON and SYSCON2)

MOV SYSCON2, #0400h

; SDD / 1 mode: enable RSTCON setting

; PLLIR is set when PLL mode is changed

MOV SYSCON2, #0000h

; basic clock mode: activate setting

... some instructions while clock is not at final state

wait for CLKLOCK:

EXTR #1

SYSCON2.15, wait for CLKLOCK; timeout recommended

JNB

PLL locked:

enable PLL interrupt:

EXTR #3

MOV

XP3IC, #0077h

; clear requests, enable XP3 interrupt,

; int. level 13, group level 3

BFLDL ISNC, #0Ch, #00h

; clear PLLIE and PLLIR

BSET PLLIE

; enable PLL interrupt

stable PLL clock

. . .

```

# **ID-Registers**

|           |      | Register: | IDMANUF           | IDCHIP            | IDMEM             | IDPROG            | IDMEM2            |

|-----------|------|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Device    | Step | Address:  | F07E <sub>H</sub> | F07C <sub>H</sub> | F07A <sub>H</sub> | F078 <sub>H</sub> | F076 <sub>H</sub> |

| C164SV-2R | -AA  |           | 1820 <sub>H</sub> | 2401 <sub>H</sub> | 1004 <sub>H</sub> | 0000 <sub>H</sub> | 0000 <sub>H</sub> |

Product and Test Engineering Group, Munich