# アプリケーション・ノート : AN-941

## パワー MOSFET の並列接続

### 目次

### ページ

|                      |    |

|----------------------|----|

| 要約 :                 | 1  |

| 概要                   | 2  |

| 回路レイアウトによるアンバランス     | 2  |

| ゲート発振                | 4  |

| 定常状態動作における電流アンバランス   | 5  |

| ターン・オン時の動的シェアリング     | 5  |

| ターン・オフ時の動的シェアリング     | 8  |

| まとめ                  | 10 |

| 付録 - 定常状態時のアンバランスの分析 | 11 |

### 要約 :

デバイスを並列接続で動作させる場合は、個々のユニットが限度内で動作するようにデバイス間のシェアリングを十分に考慮する必要があります。MOSFET の並列接続で好結果を得るために考慮すべき事項は、ゲート回路、レイアウトの検討、電流アンバランス、および温度アンバランスです。

本書ではこれらのトピックを取り扱い、並列接続に関するガイドラインを示します。

## 概要

並列接続を行うと、伝導損失と接合部・ケース間熱抵抗が減少します。ただし、スイッチング損失は変化しないか、場合によってはさらに増加します。スイッチング損失が主な損失である場合は、熱抵抗だけが並列接続によって改善されます。低価格の小型デバイスを利用するための並列接続は、技術的なリスクを十分に考慮した上で行う必要があります。半導体を並列接続する際には、製造時の最大値と最小値の両極端で実験結果を得るのが適切な方法です。

複数のディスクリートを並列接続するには、各デバイスの電力損失と（さらに重要な）接合部温度をできるだけ等しくする必要があります。各種デバイスの間には電気的特性の違いがあるため、ある程度の損失のアンバランスは避けられません。そのため、特定の量の電流ディレーティング（通常は約 20%）が必要になります。

このディレーティングを行った場合でも、各接合部の温度が相互に近い温度を保つようにするには緊密な熱結合が必要です。一般にパッケージとシンクの間に配置される絶縁シートは、接合部温度を分離し、温度差を増加させる傾向があります。この観点から見ると、並列接続されたデバイスを別々のヒートシンク上に配置するのは最悪の実装方法といえます。

共通ヒートスプレッダは、半導体を同じ温度に保つ上で非常に効果的な方法です。また、共通ヒートスプレッダはアセンブリ時の機械的なキャリアとしても機能します。電気的な絶縁が必要な場合は、絶縁バリアーをキャリアとヒートシンクの間に配置できます。

## 回路レイアウトによるアンバランス

非対称のレイアウトに起因する外部回路のアンバランスは、並列接続されたデバイス間で重大な損失の差を引き起こす可能性があります。非対称のレイアウトの最も深刻な影響は、スイッチング期間中の電流アンバランスとその結果生じるスイッチング損失のアンバランスです。これについては、後続の節で詳しく説明します。

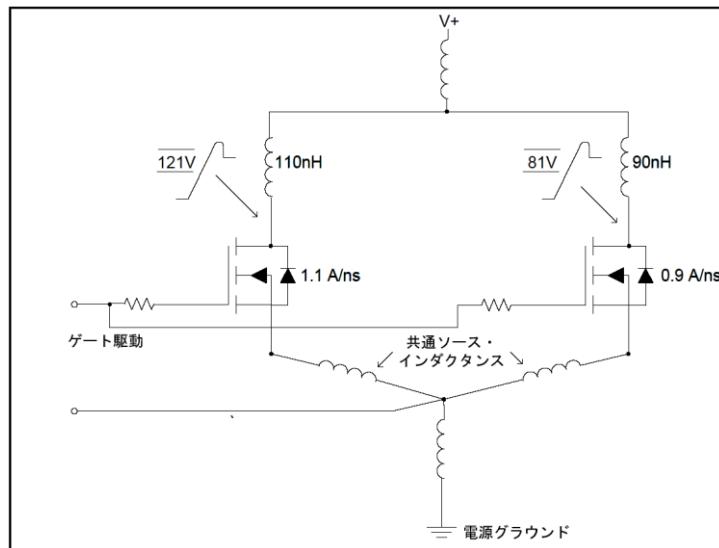

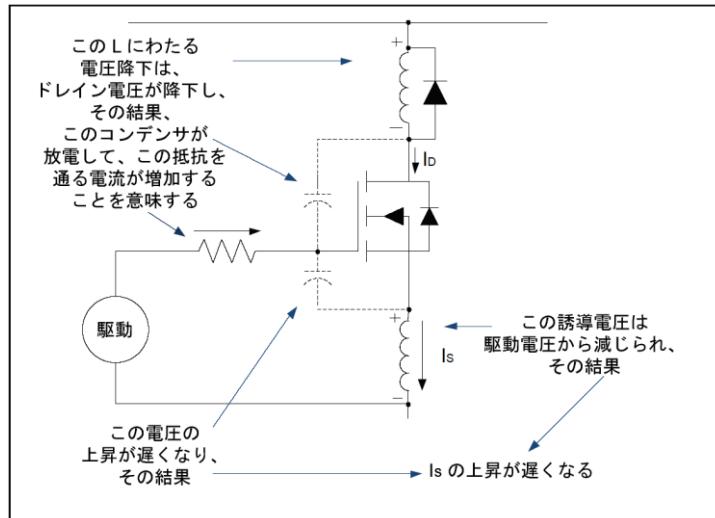

一般に、電圧値が同等であることは、デバイスが並列であることによって保証されます。ただし、過渡的な状況下では、均等化されていない浮遊インダクタンスでの  $di/dt$  効果により、電圧差がデバイス間に現れる可能性があります。バランスされなければならない浮遊回路要素は、ゲート回路に共通するソースと直列にあるインダクタンスです（「共通ソース・インダクタンス」。図 1 を参照してください）。ターン・オンおよびターン・オフ時の  $di/dt$  によってこのインダクタンス間に生じる電圧は、印加されたゲート駆動電圧を打ち消し、ソース電流の変化速度を低下させます。

図 1 共通ソース・インダクタンス

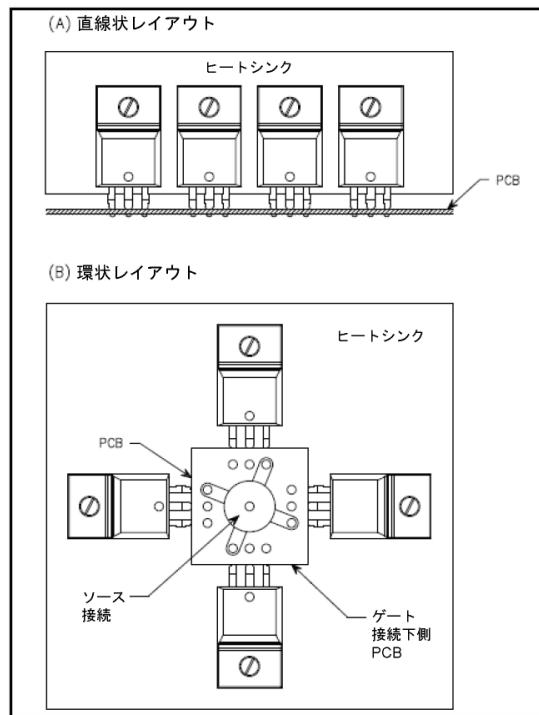

伝導損失に比べてスイッチング損失が比較的小さい場合は、回路に起因するスイッチング損失のアンバランスはある程度許容でき、レイアウトが極端に重要になることもありません。この場合は、対称型ではないものの、よく使用される単純な直線状の配置で十分に対応できます。図 2 (A) を参照してください。

スイッチング損失がかなり大きい場合は、レイアウトに十分注意を払う必要があります。図 2 (B) に示した回路レイアウトは、共通エミッタ・インダクタンスのバランスとスイッチング損失を等しくする面で、はるかに優れています。

ドレインと直列にある個々の浮遊インダクタンスは、あまり問題になることはありません。これらの浮遊分での 10% のアンバランスを 10% の  $di/dt$  アンバランスと組み合わせると、ターン・オフ時に見られるオーバーシュートでのアンバランスは 20% になります (81V 対 121V)。図 1 を参照してください。ただし、オーバーシュートが MOSFET の定格に超えない場合は、ターン・オフ損失の差は無視することができます。図 2 (B) のレイアウトは、浮遊インダクタンスとそれに関連するオーバーシュートを等しくします。 $di/dt$  の差は通常抑制されており、スイッチング・エネルギーに大きく影響することはありません。

図 2 (A) および (B) 異なるレイアウト

## ゲート発振

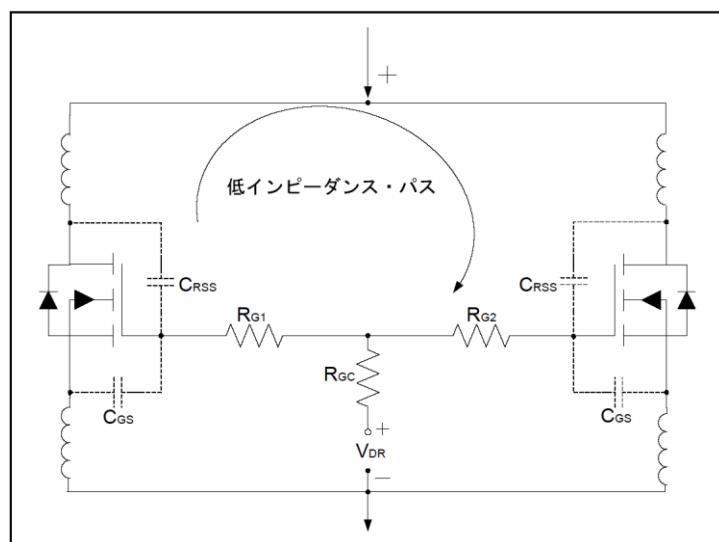

並列接続された MOSFET に個別のゲート抵抗が必要であることは一般に知られています。図 3 に示すように、並列接続された MOSFET には、寄生自己発振しやすい共通の低インピーダンス・パスがあります。これは、参考文献 [1] でさらに詳しく分析されています。個々のゲート抵抗は、発振を防止するために必要なダンピングとゲート・デカップリングを提供します。

図 3 寄生発振の低インピーダンス・パス

非常に大きいゲート抵抗は、デバイスのスイッチング性能を低下させ、スイッチングのアンバランスを増加させます。必要な値だけを使用するようにしてください。

## 定常状態動作における電流アンバランス

スイッチング期間以外では、MOSFET の並列グループ内の電流は、オン抵抗に反比例して個々のデバイスに分配されます。つまり、オン抵抗が最も低いデバイスに最も多くの電流が流れます。オン抵抗の正の温度係数は、このアンバランスを補償して電流を均等にするようにします。

この自己バランスメカニズムは、前節で推奨した緊密な熱結合によって補われます。ただし、半導体デバイスの故障は主に過剰な温度が原因であり、過剰な定常状態電流が原因になることはめったにないことに注意してください。

MOSFET の内蔵ダイオードの電圧降下は正の温度係数ではありません。したがって、大きな定常状態電流のアンバランスがダイオード伝導中に生じる可能性があります。ただし、より多くの電流を流すダイオードと一体化した MOSFET のオン抵抗は増加し、いずれにしても接合部温度が他の並列接続したデバイスから大きくずれないことが熱結合によって保証されるため、これが問題になることはほとんどありません。

「付録」では、定常状態アンバランスの特定の例を分析しています。さらに詳しい分析は、参考文献 [1] に記載されています。

## ターン・オン時の動的シェアリング

各パワー MOSFET のしきい値およびゲイン特性はそれぞれ異なります。しきい値が低くトランスクンダクタンスが高いデバイスは、他のデバイスよりも早くスイッチングし、割り当て分以上の電流を流す傾向があります。また、各デバイスに関連する回路インダクタンスも異なる可能性があるため、これもスイッチング状況下では電流のアンバランスの一因となります。ここでは、スイッチング期間中に発生するさまざまな事象の定性的な説明を簡単に示します。

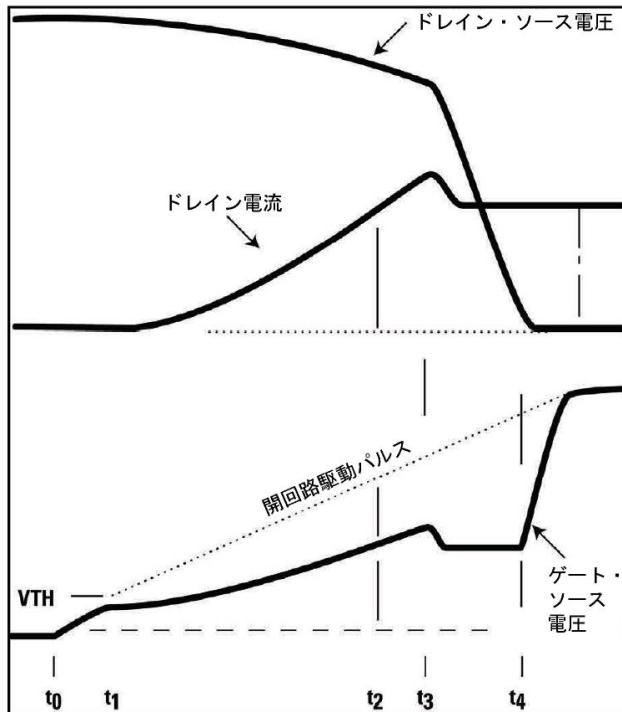

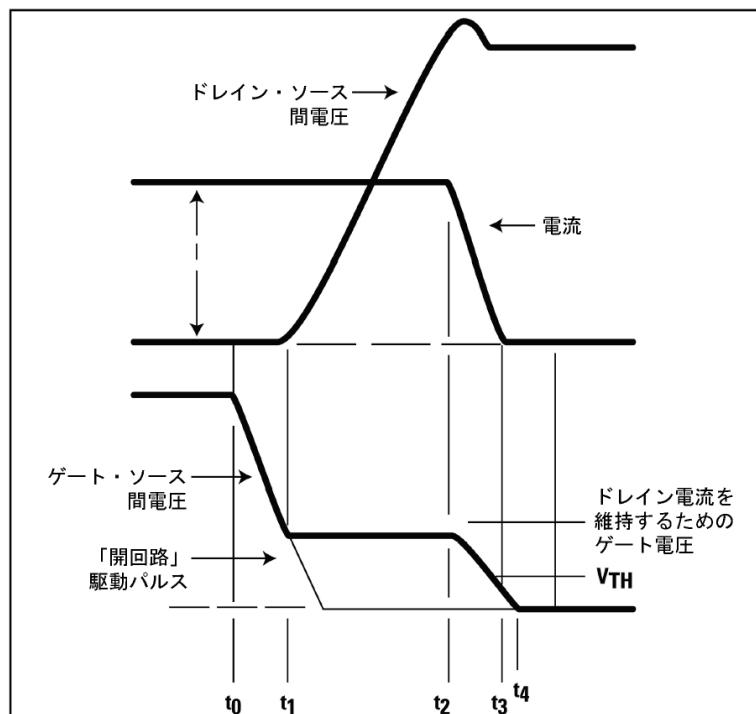

この問題は、典型的なクランプ・インダクティブ負荷のスイッチング波形を検討することによって明らかになります。図 4 は、ターン・オン期間中のドレイン電流、ドレイン・ソース間電圧、およびゲート電圧を示しています。ここでは、分かりやすくするため、比較的低速で上昇する印加駆動パルスを示しています。

図 4 ターン・オン時の波形

時間  $t_0$  では、駆動パルスが立ち上がり始めます。時間  $t_1$  では、駆動パルスが MOSFET のしきい電圧に達し、ドレイン電流が増加し始めます。この時点では、ゲート・ソース間電圧波形を元の「経路」から逸脱させる 2 つの事象が発生します。まず、ゲート回路に共通するソースと直列にあるインダクタンスは、ソース電流増加の結果として誘起電圧を発生します。この電圧は印加されたゲート駆動電圧を打ち消し、ゲート端子とソース端子間に直接現れる電圧の上昇速度を低下させます。これにより、ソース電流の上昇速度が低下します。

ゲート・ソース間電圧に影響する 2 つ目の要因は、いわゆる「ミラー」効果です。 $t_1$  から  $t_2$  の期間では、ドレインと直列の回路インダクタンスで電圧がある程度降下し、ドレイン・ソース間電圧が降下し始めます。低下中のドレイン・ソース間電圧はドレイン・ゲート間キャパシタンスに反映され、そのキャパシタンスを通じて放電電流を引き込み、駆動回路上の実効キャパシタンス負荷を増加させます。これにより、駆動回路のインピーダンスでの電圧降下量が増加し、ゲート端子とソース端子の間に現れる電圧の上昇速度が低下します。これは、負の帰還効果でもあります。つまり、ドレインの電流を増加させると、ドレイン・ソース間電圧が降下します。この電圧降下はゲート・ソース間電圧の上昇を遅くし、ドレイン電流の増加を妨げる傾向があります。これらの効果を図 5 に示します。

図 5 スイッチング ON 時の効果

この状態は期間  $t_1 \sim t_2$  の全体にわたって継続し、その一方で MOSFET の電流がフリーホイールダイオードを流れる電流のレベルまで上昇します。また、この状態は次の期間 ( $t_2 \sim t_3$ ) でも継続し、その間はフリーホイールダイオードの逆回復によって電流がさらに増加します。

時間  $t_3$  では、フリーホイールダイオードが電圧を支え始め、その一方でドレイン電流とドレイン電圧は降下し始めます。ドレイン電圧の降下速度はその後ミラー効果によって制御されるようになります。ドレイン電圧が必要なだけの比率で下降するので、ゲート・ソース間電圧が負荷で決められたドレイン電流レベルを満たし、平衡的な状態に達します。そのため、ゲート・ソース間電圧はフリーホイールダイオードの回復電流の減少につれて降下し、ドレイン電圧の降下中は負荷電流に対応するレベルで一定に保たれます。

最後に、時間  $t_4$  では、MOSFET は完全に導通状態になり、ゲート・ソース間電圧は印加された「開回路」の値に向かって急速に上昇します。

図 5 に要約されている上記の説明は、並列接続されたデバイスで起こりうる問題に対処するための手掛かりを示しています。1 つ目の潜在的な問題は、共通駆動信号を並列グループ内のすべてのゲートに印加した場合、ターン・オンする最初のデバイス（しきい電圧が最も低いデバイス）は他のデバイスのゲートで電圧の上昇を遅くし、これらのデバイスのターン・オンをさらに遅らせる傾向があるということです。この問題の原因是ミラー効果です。その一方で、誘導性帰還効果は、それ自身のデバイスのゲート電圧にのみ影響します（各ソースに別個のインダクタンスがあることを前提とします）。

2つ目の潜在的な問題は、ソース・インダクタンスが一様でない場合、デバイス自体が完全に適合していても電流の動的アンバランスが生じるということです。言うまでもなく、この問題の解決法は、個々のデバイスに関連したインダクタンスを可能な限り同じにすることです。これは、回路レイアウトに適切な注意を払うことで実現します。

参考文献 [1] で詳しく検討されているように、動的アンバランスの一因となる回路やデバイス・パラメータは他にもいくつか存在します。ただし、参考文献 [1] に記載されている結論は、本書に記載された一般的なガイドラインに従っている限り、この問題は深刻でないことを示しています。

## ターン・オフ時の動的シェアリング

ターン・オフ期間中の電流の動的シェアリングにも同様の事項が当てはまります。図 6 は、ターン・オフ期間中の理論上の波形を示しています。 $t_0$  では、ゲート駆動が降下し始めます。 $t_1$  では、ゲート電圧がドレイン電流を維持するレベルに達します。次に、ドレイン・ソース間電圧が上昇し始めます。ミラー効果はドレイン電圧の上昇速度を制御し、ゲート・ソース間電圧を一定のドレイン電流に対応するレベルで保持します。 $t_3$  では、ドレイン電圧の上昇が完了します。また、ゲート・ソース間回路インピーダンスによって決定された速度でゲート電圧が降下し始め、その一方でドレイン電流がゼロまで降下します。

図 6 ターン・オフ時の典型的な波形

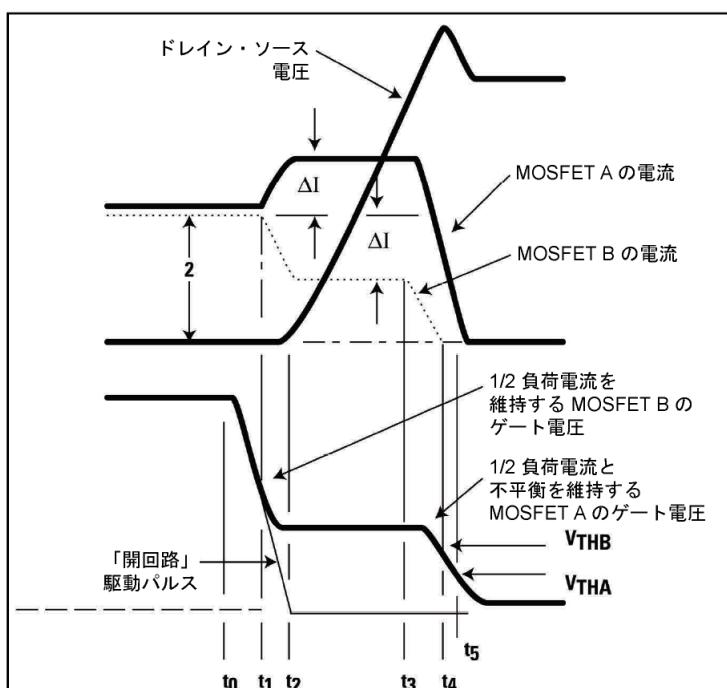

図 7 は、ゲートが互いに直接接続されている 2 つの並列接続 MOSFET の理論上の波形を示しています。ここでは、分かりやすくするため、ソース・インダクタンスはゼロであると仮定します。 $t_1$  では、ゲート電圧は MOSFET B がドレイン電流を維持できなくなるポイントに達します。

次に、負荷電流が再分配されます。つまり、MOSFET B の電流が減少し、MOSFET A の電流が増加します。 $t_2$  では、MOSFET B は電流を維持できなくなります。どちらの MOSFET もリニア領域で動作し、ドレイン電圧が上昇し始めます。ゲート・ソース間電圧はミラー効果によって実質的に一定に保たれます。2 つの MOSFET の電流は別々のレベルにとどまります。言うまでもなく、この例における電流のアンバランスは重大な問題です。

図 7 ターン・オフ波形に対する並列接続の効果

ターン・オフ時のアンバランスはより深刻な問題になる可能性がありますが、参考文献 [1] の分析は、「ハード」(非常に低いインピーダンス) ゲート駆動で MOSFET をターン・オフすることによって、この問題を十分に抑制できることを示しています。これにより、ターン・オフ時の限定された動的アンバランスがほぼ保証されます。

要約すると、ターン・オフ時に適切なシェアリングを実現するためには、「ハード」駆動に加えて、ターン・オンの場合と同じ予防策を使用する必要があります。

## まとめ

MOSFET を並列接続する場合は、以下の一般的なガイドラインに従うことをお勧めします。

- 個別のゲート抵抗を使用して、寄生発振のリスクを取り除きます。

- 並列接続されたデバイスに緊密な熱結合を確保します。

- 共通ソース・インダクタンスを等しくし、動作周波数での全体的なスイッチング損失に大きく影響しない値まで削減します。

- 浮遊インダクタンスを、最大動作電流で許容可能なオーバーシュートになる値まで削減します。

- できるだけ小さいインピーダンスの電源に MOSFET のゲートが接続されていることを確認します。

- ゲート駆動回路のツェナー・ダイオードは、発振を引き起こす可能性があります。必要な場合には、ゲート・デカップリング抵抗のドライバ側にツェナー・ダイオードを配置する。

- ゲート駆動回路のコンデンサはスイッチングを遅くし、その結果、デバイス間のスイッチングアンバランスを増加させ、発振を引き起こす可能性があります。

- 浮遊素子はタイトなレイアウトによって最小化され、対称位置の素子配置と接続経路によって等しくなる。

## 付録 - 定常状態アンバランスの分析

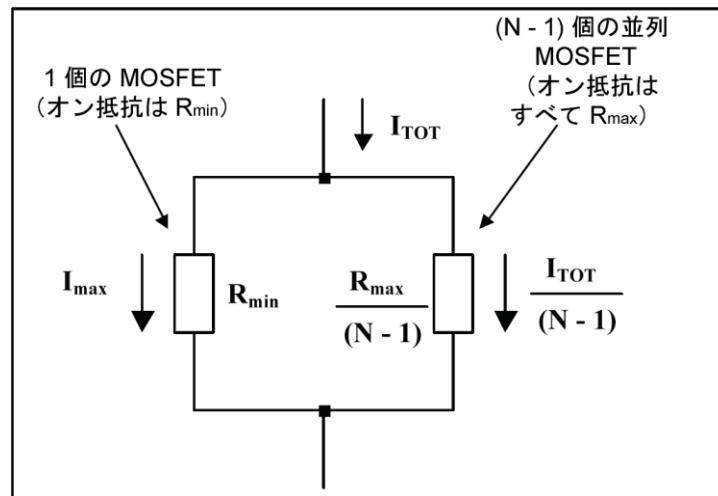

$N$  個の並列接続デバイスのグループにおける「最悪ケース」のデバイス電流は、 $(N - 1)$  個のデバイスが最高値のオン抵抗であり、1 つのデバイスにのみ最低値のオン抵抗であるという単純な仮定に基づいて分析できます。そうすることで、この 1 つのデバイスの電流に分析の的を絞ることができます。

高抵抗の各デバイスを通じて流れる電流が約  $I_{TOT}/(N-1)$  になるような十分な数のデバイスがあると仮定すると、図 A1 に示した等価電気回路によって分析がさらに単純化されます。ただ 1 つの低抵抗デバイスにわたる電圧降下とそのデバイスの電流は、この仮定に基づいて計算できます。

動作温度  $T$  における各「高抵抗」デバイスのオン抵抗は、以下の式によって求められます。

$$R_{(max)T} = R_{(max)25} \left( 1 + \left[ (T_A - 25) + \frac{\rho_{TOT}}{(N-1)^2} R_{(max)T} R_{JA} \right] K \right) \quad (1)$$

ここで、 $R_{(max)25}$  は  $25^{\circ}\text{C}$  におけるオン抵抗の最大値、 $R_{JA}$  は接合部・周囲間の全熱抵抗 ( $^{\circ}\text{C}/\text{W}$ )、 $K$  は  $1^{\circ}\text{C}$ あたりのユニットごとのオン抵抗変化です。

したがって、

$$R_{(max)T} = \frac{R_{(max)25} (1 + [T_A - 25] K)}{1 - R_{(max)25} \frac{\rho_{TOT}}{(N-1)^2} R_{JA} K} \quad (2)$$

並列グループにわたる電圧降下  $V$  は以下のようになります。

$$V = \frac{I_{TOT}}{(N-1)} \cdot R_{(max)T} \quad (3)$$

図 A1 最悪ケースの定常状態電流アンバランスを概算するための簡易等価回路

動作温度における 1 つの低抵抗デバイスの抵抗は、以下のようになります。

$$R_{(min)T} = R_{(min)25} (1 + [(T_A - 25) + V_{(max)} R_{JA}] K) \quad (4)$$

ここで、 $R_{(min)25}$  は  $25^{\circ}\text{C}$  におけるオン抵抗の最小値、 $I_{(max)}$  はこのデバイスの電流です。

ただし、

$$R_{(min)T} = \frac{V}{I_{(max)}} \quad (5)$$

したがって、

$$I_{(max)} = \frac{-b + \sqrt{(b^2 - 4aV)}}{2a}$$

ここで、

$$b = R_{(min)25} (1 + [T_A - 25] K)$$

$$a = R_{(min)25} V R_{JA} K$$

以下の例では、上記の関係を IRFP150 MOSFET に適用し、以下の値を前提とすることによって、予想される電流シェアリングの「最悪ケース」の度合いを示します。

$$R_{(max)25} = 0.045\Omega$$

$$R_{(min)25} = 0.035\Omega$$

$$R_{JA} = 3 \text{ 度 C/W}$$

$$\frac{I_{TOT}}{(N-1)} = 20A \quad (6)$$

$$K = 1^{\circ}\text{C} \text{ あたり } 0.006$$

$$T_A = 35^{\circ}\text{C}$$

1 つを除くすべてのデバイスが  $0.045\Omega$  の高いオン抵抗を持ち、それぞれ 20A を流しているのに対して、残りの 1 つのデバイスが  $0.035\Omega$  の低いオン抵抗を持っているという仮想状況では、上記の関係(2)、(3)、(5)を使用することにより、デバイス電流の「最悪ケース」の最大値が 27A であることを計算できます。

## 参考文献 :

1. J.B. Forsythe : 『Paralleling of Power MOSFETs』 IEEE-IAS Conference Record, 1981 年 10 月