## アプリケーション・ノート：AN-1139

---

### IR1168 Dual SmartRectifier<sup>TM</sup> 制御 IC を使用した 二次側整流の設計

*Adnaan Lokhandwala*

#### 目次

はじめに／デバイスの概要

LLC 共振ハーフブリッジ・コンバータ動作

共振コンバータにおける Dual SmartRectifier<sup>TM</sup> の動作

標準的な周辺回路と受動部品

設計手順及び設計例

レイアウトの指針

付録

記号の一覧

References

はじめに／デバイスの概要

IR1168 は、絶縁型 DC-DC 共振型コンバータの中で同期整流用に使われる 2 つの N チャネルパワーMOSFET を駆動するために設計した、二次側のゲート駆動 IC です。ショットキ・ダイオードによる整流動作を、1 個または並列接続した複数個の MOSFET に置き換えたときに、その MOSFET を制御するための IC です。堅牢性と雑音耐性は、先進的なブランкиング手法と二重パルス抑止を使用して実現し、これにより固定周波数、可変周波数のいずれでも高信頼の動作が可能となります。差動入力の比較器で MOSFET のドレイン-ソース間電圧  $V_{DS}$  を検出して電流レベルを決め、電流変化がゼロとなる近くでデバイスをオン／オフさせます。この IC は 8 ピン・パッケージに収めており、そのピン配置が図 1 です。

| ピン配置                               | ピン番号 | 記号    | 説明                |

|------------------------------------|------|-------|-------------------|

| 1 GATE1<br>2 VCC<br>3 VS1<br>4 VD1 | 1    | ゲート 1 | ゲート駆動出力 1         |

| IR1168<br>GND<br>VS2<br>VD2        | 2    | VCC   | 供給電圧              |

|                                    | 3    | VS1   | 同期 FET 1 ソース電圧検出  |

|                                    | 4    | VD1   | 同期 FET 1 ドレイン電圧検出 |

|                                    | 5    | VD2   | 同期 FET 2 ドレイン電圧検出 |

|                                    | 6    | VS2   | 同期 FET 2 ソース電圧検出  |

|                                    | 7    | GND   | アナログ及び電源アース       |

|                                    | 8    | ゲート 2 | ゲート駆動出力 2         |

図 1 : IR1168 Dual SmartRectifier<sup>TM</sup> 制御 IC のピン配置

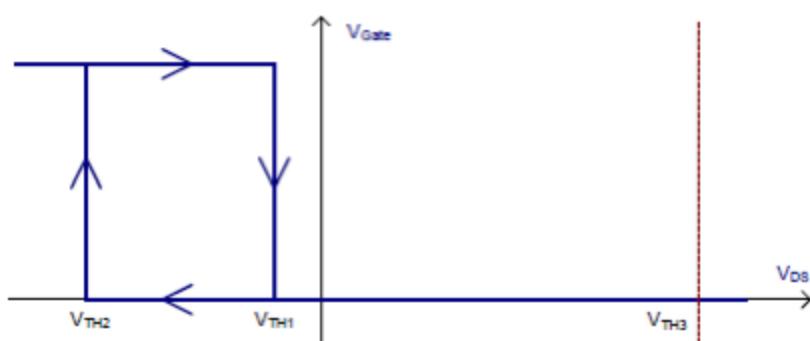

SmartRectifierコントロール技術では、MOSFETに加わる電圧を検出し、それを2種類の負のしきい電圧と比較して、MOSFETのオン／オフを決定します。大きい方の負のしきい電圧  $V_{TH2}$  がボディ・ダイオードを流れる電流を検出して、パワー・デバイスのオンへの変化を制御します。同様に、外部から設定した小さい方の負のしきい電圧  $V_{TH1}$  は、MOSFETがオフする電流レベルを決定します。

図 2 : IR1168 Dual SmartRectifier<sup>TM</sup> 制御 IC の差動電圧検出しきい値

パワー・デバイスがオンすると、検出電圧が瞬時に、オン抵抗  $R_{DSon} \times$  ドレイン電流  $I_D$  まで減少して、デバイス電流のレベルに応じてターン・オフのしきい値を下回ることがあるため、

デバイスが誤ってオフしてしまうことがあります。またデバイスのターン・オンは、トランスの漏れインダクタンスと、デバイスの出力容量との間で発生するリングングにも関係します。そのため、デバイス電流がそのボディ・ダイオードとチャネルの間を遷移する際の誤ったターン・オフやゲートチャタリングを防止するために、制御論理回路が追加されています。

## LLC ハーフブリッジ・コンバータ動作

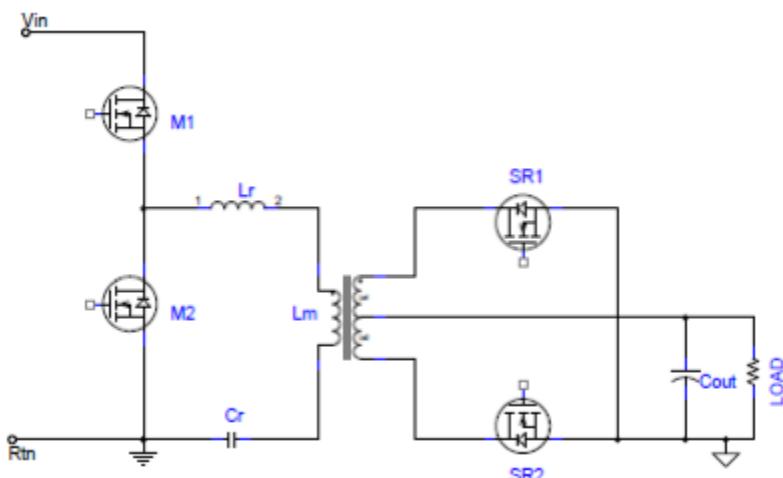

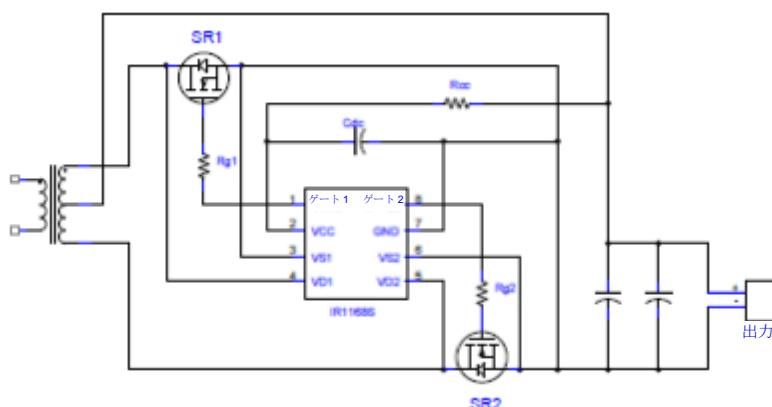

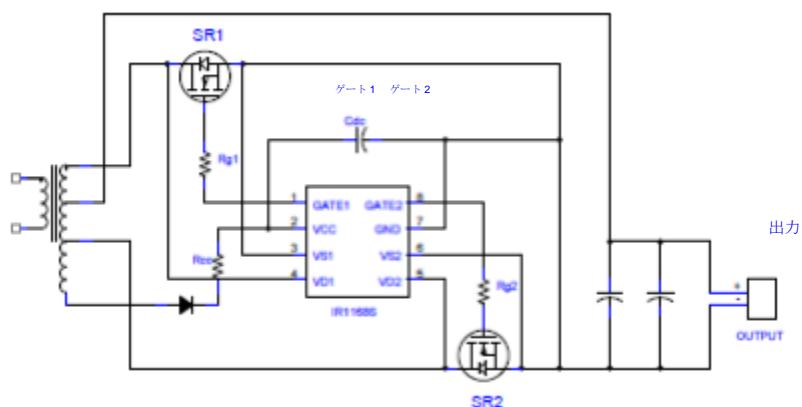

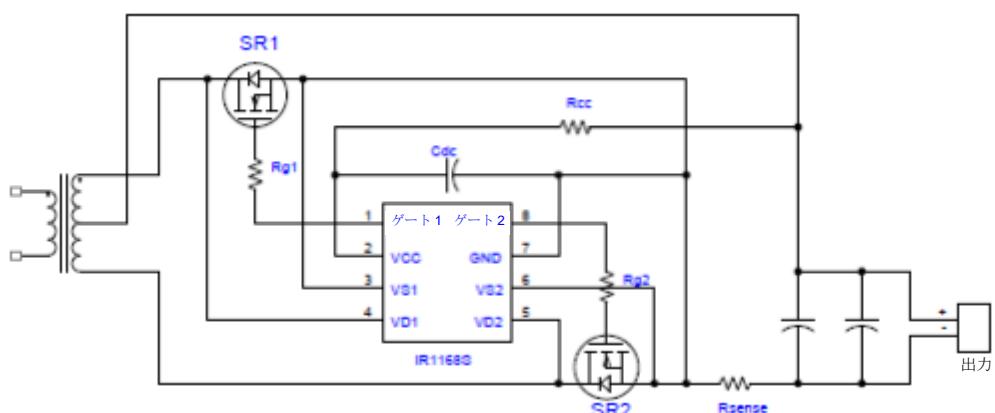

高効率、低 EMI、高い出力密度を実現できるため、ハーフブリッジ構成の LLC 共振コンバータの採用が進んでいます。このトポロジーは、フロントエンド DC バス変換において、最も魅力的なトポロジーでもあります。これはトランスの励磁インダクタンスを利用して、ソフトスイッチング領域において、降昇圧変換特性を持った複合共振タンクを構成します。同期出力整流（ローサイド構成）を持ったこのトポロジーの一般的なパワーワンの回路図を下図に示します。

図 3 : 同期整流出力をもつた DC-DC ハーフブリッジ共振コンバータの一般的な回路図

M1 と M2 は、50%のデューティサイクルで動作し、出力電圧はコンバータのスイッチング周波数を変化させてレギュレーションされます。コンバータには 2 つの共振周波数があります。低い共振周波数 ( $L_m$ 、 $L_r$ 、 $C_r$  および負荷から得られる) 及び、固定の、より高い直列共振周波数  $f_{r1}$  ( $L_r$  と  $C_r$  のみから得られます) です。コンバータを、 $f_{r1}$  を超えてまたは下回って動作させることで、2 つのブリッジデバイスを全負荷領域において、ソフトスイッチング動作とすることができます。

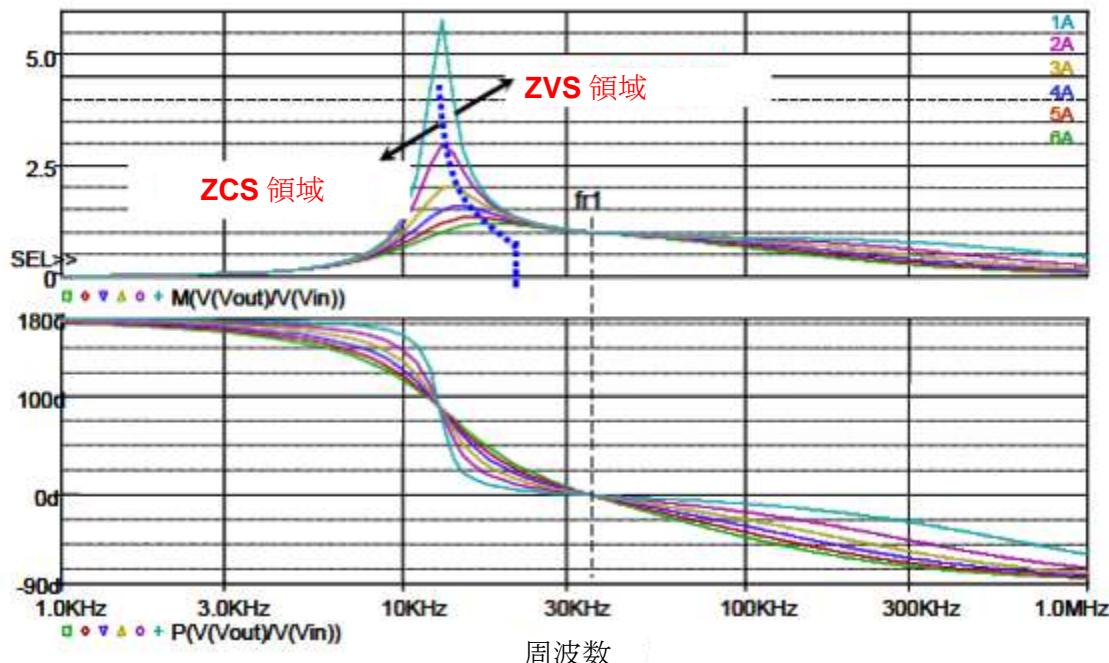

このトポロジーは、 $f_{r1}$  を上回る領域で動作する際は、直列共振コンバータに非常に近い動作をします。LLC タンク共振コンバータの一般的な AC 変換特性<sup>1</sup>を図 4 に示します。

図 4 : LLC 共振コンバータの一般的な周波数特性

LLC 共振コンバータの特性は、3 つの動作モードに応じて、3 つの領域に区別することができます。コンバータ動作は ZCS 領域に入らないようにする必要があります。 $f_{r1}$  を上回る領域では、コンバータは直列共振コンバータに非常に近い動作をします。この動作領域では、 $L_m$  は出力電圧により抑制されており、直列共振タンクの負荷の役割を果たし、共振コンデンサ  $C_r$  と共に共振することは一切ありません。

$f_{r1}$  以下の ZVS 領域では、LLC 共振コンバータ動作はさらに複雑となり、2 つの時間に分けることができます。1 つめの時間で、 $L_r$  は  $C_r$  と  $L_m$  と共に共振し、出力電圧によりクランプされます。共振インダクタ  $L_r$  の電流が、共振して励磁電流と同レベルまで戻ると、 $L_r$  と  $C_r$  の共振は止まります。このときに  $L_m$  が共振動作に加わり、2 つめの時間が始まります。この時共振要素は、 $L_r$  と直列の  $C_r$  と  $L_m$  に変化します。

<sup>1</sup> この AC 解析では、出力への電力変換に貢献するのは、共振ネットワークへの矩形波電圧入力の基本要素のみです。トランス、整流器、フィルターは相当の AC 抵抗  $R_{ac}$  に置き換えています。

## 共振コンバータにおける Dual SmartRectifier™ の動作

IR1168 Dual SmartRectifier™ IC は、同期整流用 MOSFET を最適に駆動することにより、2つの2次側整流器の動作を置き換えることができます。2次側の2つラインの整流電流は、パワーMOSFET の  $R_{DSon}$  をシャント抵抗として検出します。そして MOSFET のゲート・ピンは、図 2 に示す 3 つのしきい値に対して検出される電圧に応じて駆動されます。

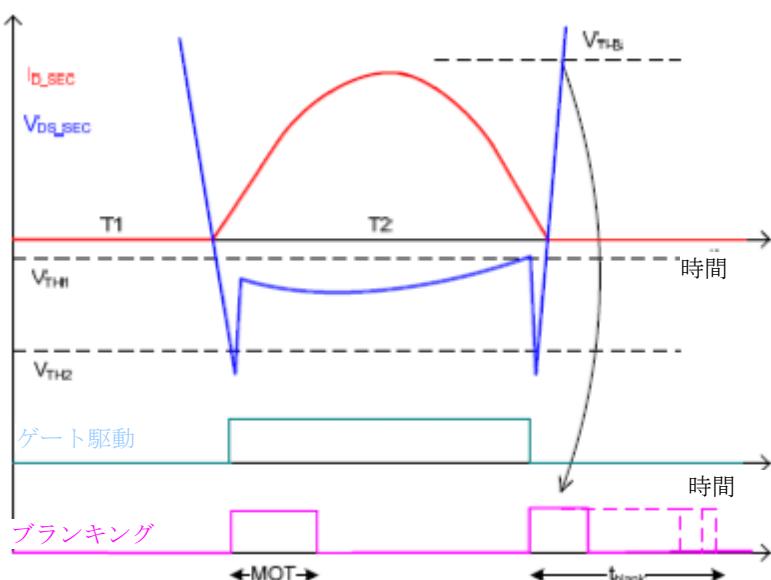

このデバイスの核となるのは、2つの高電圧 (200V) の高速コンパレータで、これらは電流の極性とレベルを判断するために、MOSFET のドレイン\_ソース間電圧を個別に検出します。そして、専用の内部論理回路により、ゼロ電流付近のパワー素子のオン／オフ動作を管理します。これにより PLL や外部タイミングソースを使うことなく、正確な動作が確保されます。さらに、誤ったゲート遷移を防止するために、内部ブランкиング論理回路が採用されており、これにより固定周波数と可変周波数のどちらの動作モードでも動作を確実なものとします。下記図 5 には一般的な波形を示します：

図 5：MOT と  $t_{BLANK}$  機能を示した一般的な動作波形

#### ▽ ターン・オン状態

同期整流用 MOSFET の導通状態が始まると、電流がボディ・ダイオードを流れ始めて、MOSFET の両端に負のドレイン-ソース間電圧  $V_{DS}$  が発生します。ボディ・ダイオードの電圧降下は、一般に MOSFET のオン抵抗で発生する電圧よりも高いため、ターン・オンのしきい電圧  $V_{TH2}$  を超えて、トリガーがかかります。この点で、IR1168 が MOSFET のゲートを駆動してオンさせ、このために導通電圧  $V_{DS}$  が低下します。この電圧降下には、一般に、ある程度のリングングが含まれるため、これによって入力の比較器がオフしてしまうことがあります。このため、固定のミニマムオンタイム (MOT) のブランкиング期間を設けて、この期間は、パワーMOSFET がオン状態を維持するようにします。MOT は MOSFET の最小導通時間も制限し、この場合、コンバータの最大スイッチング周波数で動作します。

#### ▽ ターン・オフ状態

同期整流用 MOSFET がいったんオンすると、整流電流が減少して  $V_{DS}$  がターン・オフのしきい電圧  $V_{TH1}$  を超えるまでオン状態が維持されます。

いったんこのしきい値になりゲートがオフになると、電流は再びボディ・ダイオードを流れ、 $V_{DS}$  電圧が負方向に高まります。残留電流の量により、 $V_{DS}$  が再度ターン・オンしきい値を越えることもあります。そのため、図 5 に示すように、誤ったターン・オンを防止するため、 $V_{TH1}$  の開始後、内部設定ブランкиング時間の間  $V_{TH2}$  のブランкиングが行われます。 $V_{DS}$  が正のしきい値  $V_{TH3}$  を超えると、ブランкиング時間は停止され、IC は次の伝導サイクルが行えるようになります。この状態の時、一次側への交差導通を防止し、スイッチング損失を減らすという意味で、ターン・オフ速度はより重要となります。

MOT とブランкиング時間論理は、各スイッチングサイクルにつき 1 回しか許されていないことに注意してください。これらを再度可能にするためには、 $V_{DS}$  が  $T_{VH3}$  に達する（すなわち次のスイッチングサイクルの準備が整う）必要があります。

## 標準的な周辺回路と受動部品

IR1168 の動作に必要な受動部品 :

- $C_{ds}$  : 電源デカップリング・コンデンサ

必須ではないが、推奨部品 :

- $R_{CC}$  : 電源コンデンサ上の直列抵抗

- $R_{g1,2}$  : 同期 MOSFET ゲート抵抗

コンバータ出力が IC の推奨範囲内にあるときは、IC の供給電圧をそこから直接取り入れることができます。これ以外の場合はすべて、下記のどちらかの手法により専用の電源を設けることが推奨されます :

- トランスの補助巻線

- トランスのメイン巻線タップ

IR1168 の一般的なシステムの形態を下記に示します :

図 6 : コンバータ出力電圧から直接 IC 電源を得る

図 7 : トランスの補助巻線から IC 電源を得る

## 設計手順

システムから得られる基本的な値：

1. 最低 ( $f_{SW\min}$ ) と最大 ( $f_{SW\max}$ ) スイッチング周波数

2. 二次側の最低伝導時間、もしくは SmartRectifier™ 技術でミニマムオンタイム (MOT) と呼ばれる値

3. IR1168 IC が動作する最高環境温度  $T_{ICamb}$  (通常 PCB の最高温度)

4. 供給可能電圧  $V_{supply}$  これはコンバータ出力電圧、もしくは専用電源 (補助巻線)

次の設計手順は同期 MOSFET、ならびに上記システムパラメータがすでに特定されていることを前提とします。これのもととなっているのは、電圧検出をコントローラへの唯一の入力として、整流の理想的な動作に近づける必要があるという考え方です。

### a. IC 消費電流計算

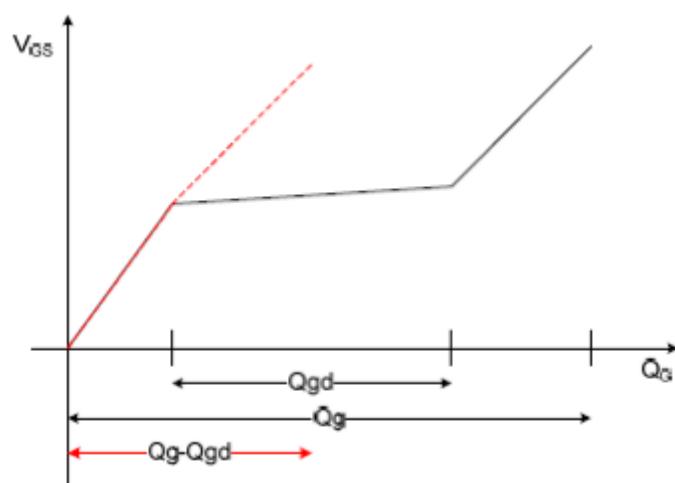

まず、選択した同期整流用 MOSFET の全ゲート電荷  $Q_g$  とゲート-ドレイン間電荷  $Q_{gd}$  と、対応するゲート電圧  $V_{gs}$  とでデータを特定する必要があります。IR1168 が動作モードなので、2 次側の電流は、最初はボディ・ダイオードを流れます。従って、オン時のゲート特性にはミラー電荷が含まれません。図 8 に、ゼロまたは少し負側のドレイン-ソース間電圧 (図中の赤の破線) でスイッチがオンするときに、ゲート特性 (黒の実線) の一般的な変化を示します。

図 8 : SmartRectifier™ 制御駆動による MOSFET ゲート特性

はるかに小さい電荷しか必要とされず、かつ動作はコンデンサ（容量）でモデル化できることは明らかです。

$$C_{sync} = \frac{Q_g - Q_{goff}}{V_{gS}}$$

並列接続するデバイスの数を増やす場合は、上記容量を（デバイスの数）倍します。ICに必要とされる最大電流は、次式で計算できます。

$$I_{cc} = I_{QCC} + 2 \times f_{SW_{max}} C_{sync} V_{ghigh} + 1.18 \times 10^{-8}$$

ここで  $V_{ghigh}$  は、IR1168 のゲート駆動回路の出力電圧で、 $f_{SW_{max}}$  は上記で決定したコンバータの最大スイッチング周波数です。2 項目はすべてが 2 つの同期 MOSFET のゲートドライバによるもので、一方 3 項目は通常動作のときに IC 内部の論理回路で消費される分です。（係数  $1.18 \times 10^{-8}$  は内部論理回路の周波数に依存する電流条件に対応）この項は IC の供給電圧に依存しないことに注意してください。

### b. 電源直列抵抗とゲート抵抗の設計ならびに熱検証

IR1168 は同期整流を採用しているため、ゼロに近い  $V_{DS}$  レベルでスイッチをオン／オフできる利点を備えています。そのため、ゲート抵抗は遷移に影響をあたえないため、独立に設計できます。

ゲート・ループを最適にするためには、通常動作で発振しないようにしなければなりません。ゲート配線パターンのループの全インダクタンスが既知とすると（実際のパターン長の初期の見積もりの値は  $1nH/mm$  とすることができます）、推奨する最小ゲート抵抗  $R_{gloop}$  は、

$$R_{gloop} > 2 \sqrt{\frac{L_g}{C_{iss}}}$$

となります。このとき  $C_{iss}$  はスイッチ入力容量（MOSFET データシートより）です。良好なレイアウト実施によりこの要件を大幅に低減することができることは明らかです。

次に、よく知られた直列RC回路の過渡現象を検討します。抵抗で消費されるエネルギーは、コンデンサに蓄積されるエネルギーと正確に一致します。IR1167Sの内部ゲート駆動回路は、常に外部ゲート抵抗と直列です。これは消費電力を比例して分担していることを意味します。まず、2つの同期整流MOSFETのうちの1つのゲートに蓄積されるエネルギー  $E_g$  を計算しましょう。

$$E_{g1} > \frac{1}{2} C_{sync1} V_{g1high}^2$$

従って、駆動回路のバッファと全ゲート抵抗（両方のゲート駆動回路）で消費される全電力  $P_{dr}$  は、

$$P_{dr} = P_{dr1} + P_{dr2} = 2J_{SW\max} E_{g1} + 2f_{SW\max} E_{g2}$$

となります。駆動回路のバッファと全ゲート抵抗は、次式の関係に従って、この消費電力を比例して分担します。

$$\frac{P_{Rg1}}{P_{dr1}} = \left( \frac{R_{g1}}{R_{g1} + R_{Source}} + \frac{R_{g1}}{R_{g1} + R_{Sink}} \right) \cdot \frac{P_{dr1}}{2}$$

この最後の関係を変形すると、

$$\frac{P_{Rg1}}{P_{dr1}} = \frac{1}{2} \left( \frac{R_{g1}}{R_{g1} + R_{Source}} + \frac{R_{g1}}{R_{g1} + R_{Sink}} \right)$$

さらに、 $R_{g1,2}$ （外部ゲート抵抗とMOSFETの内部ゲート抵抗を含む）について解くと、ゲート抵抗で消費される全駆動電力のパーセント値を縦軸にしたグラフが描けます。これは、ゲート抵抗自体の最適寸法を決めるときにも使えます。IR1168データシートには、プルアップ( $r_{up}$ )とプルダウン( $r_{down}$ )抵抗が指定されています。また、上記計算については、電圧抑制のために若干のエネルギーがさらに消失されることを考慮する意味で  $R_{Sink} - r_{down}$  及び  $R_{Source} = 1.1r_{up}$  を使用します。

最後のステップは、選択した値に対する熱的考察です。MOSFETの接合部と周囲（周囲とはICが動作する環境のことです。きょう体やプリント回路基板などです）との間の最大熱抵抗、最大温度、ICの最大接合部温度を使うと、ICの最大許容消費電力  $P_{ICmax}$  が計算できます。

$$P_{IC_{max}} = \frac{T_{J_{max}} - T_{IC\_amb}}{R_{\theta,JA}}$$

このとき  $R_{\theta,JA}=128^{\circ}\text{C}/\text{W}$  (IR1168 データシートより) です。

下式で  $PRg$  は既知であり、供給電流  $ICC$  は計算済みなので、電源電圧  $VCC$  (すなわち IR1168 の入力電力) を制限することになります。電源電圧の最大値  $V_{CC_{max}}$  は、

$$V_{CC_{max}} = \frac{P_{IC_{max}} + P_{Rg1} + P_{Rg2}}{I_{CC}}$$

となります。

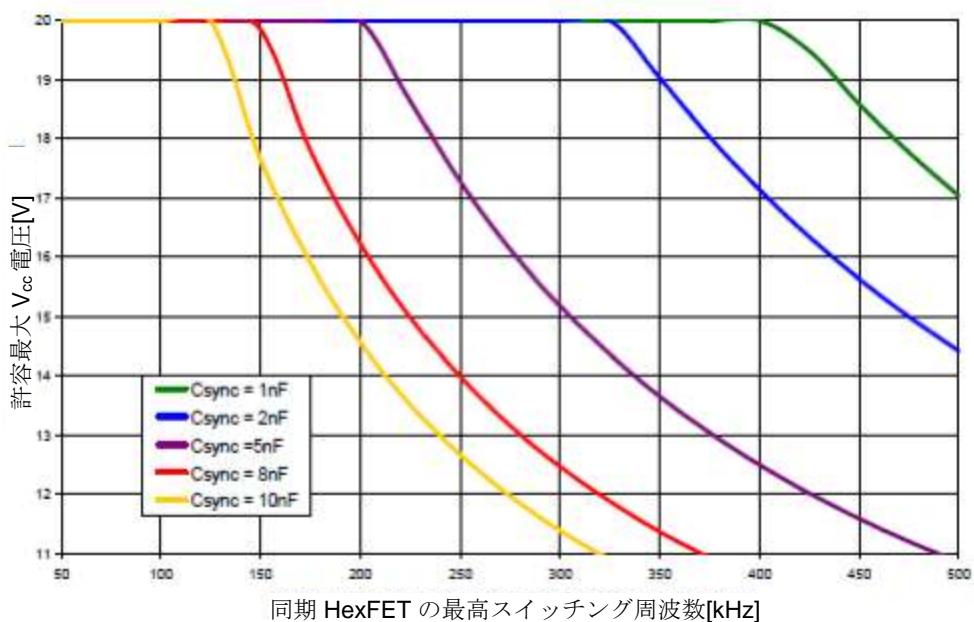

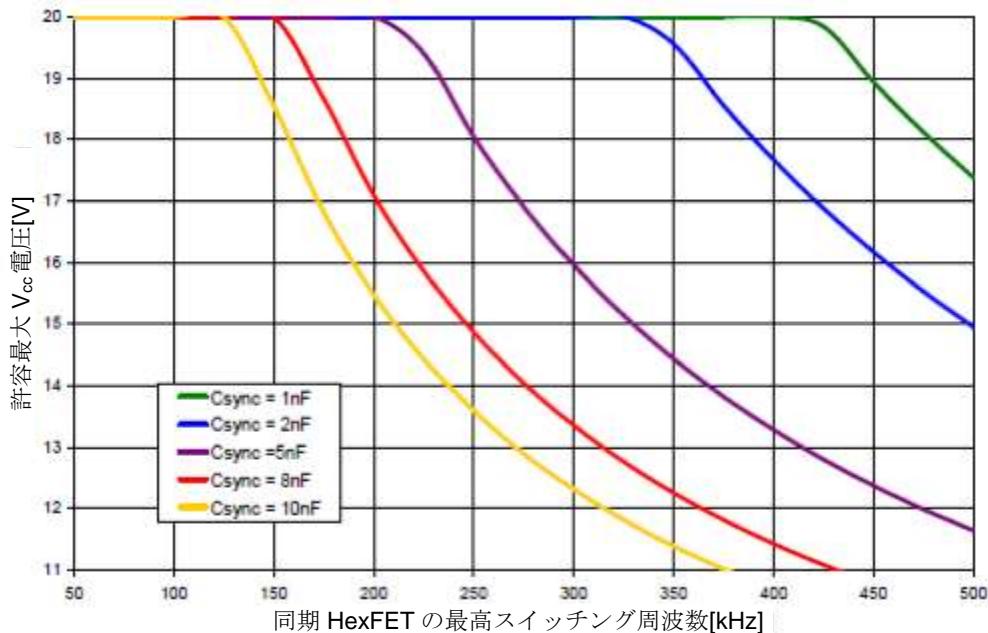

下記のグラフは、最大許容  $V_{CC}$  に対する、さまざまな負荷キャパシタンスにおける最大スイッチング周波数を示したものです。 (このとき  $T_{J_{max}} = 125^{\circ}\text{C}$ 、 $T_{IC\_amb} = 55^{\circ}\text{C}$ 、 $1\Omega$  MOSFET 内部ゲート抵抗と想定します)

図 9：最大  $V_{CC}$  供給電圧に対する  $R_{g1,2} = 3\Omega$  でのスイッチング周波数

図 10：最大  $V_{cc}$  供給電圧に対する  $R_{g1,2} = 4\Omega$  でのスイッチング周波数

上記 2 つグラフから、設計のトレードオフで、電源電圧とゲート抵抗の役割は明確です。多くの民生用システムでは、ループ・ダンピング用の最小ゲート抵抗値は熱的条件を満たすと思われます。満たさない場合は、次のステップから成る手順を繰り返してください。

ステップ 1：次の直列抵抗<sup>2</sup>を使って  $V_{cc}$  をできる限り小さくします。

$$R_{cc} = \frac{V_{supply} - V_{cc}}{I_{cc}}$$

これにより、 $V_{cc}$  が熱的な制限を満たすなら、ゲート抵抗値を設計のままにできます。

<sup>2</sup> 電源に対する直列抵抗を大きくすることには、さらなる利点があります。その場所に配置したデカップリング・コンデンサによるフィルタ機能が強化されることです。出力から電源を受けるシステム（専用の巻線などを使わない）では、スムーズな動作が得られます。

ステップ2：ゲート抵抗値を大きくします。小さな抵抗が使われていた場合には効果的です。

### c. デカップリング・コンデンサ

デカップリング・コンデンサの値の決定には、システム構成や特別な要求に応じてさまざまな技術を使うことができます。一般的な2つの例としては、IR1168が電源を出力から直接得る場合と専用巻線を介して得る場合があります。

最初の場合では、電圧リップルと雑音を減らすために、電源に対して直列抵抗を接続して（熱的理由ですでに使っていない場合）、低域通過フィルタを構成するようにコンデンサの値を決めることがあります。この低域通過フィルタの極の周波数は、最小動作スイッチング周波数（待機状態でないとき）よりも数オクターブ低くしてください。

$$C_{dc\_min} = \frac{2}{\pi \times f_{SW\ min} \times R_{CC}}$$

2つ目の例の補助巻線や巻線タップを使った動作の場合、主電源がないときでも許容電圧リップル $\Delta V_{CC}$ 以内で、スイッチング周期1周期分の動作を可能にするようにデカップリング・コンデンサの値を決めてください。

$$C_{dc\_min} = \frac{I_{CC}}{f_{SW\ min} \times \Delta V_{CC}}$$

#### 設計例

##### システムデータ：

- $f_{SW\ max} = 250\text{ kHz}$

- $f_{SW\ min} = 50\text{ kHz}$

- $T_{ICamb} = 70^\circ\text{C}$

- コンバータ出力圧力 = 19V

同期整流 MOSFET : IRF7855PbF (最大 60V/ $9.4\text{m}\Omega$ )

- $Q_g = 26nC @ V_{gs} = 10V$

- $Q_{gd} = 9.6nC @ V_{gs} = 10V$

- $C_{iss} = 1.56nF$

a. IC の消費電流の計算

$$C_{sync} = \frac{Q_g - Q_{gd}}{V_{gs}} = 1.6nF$$

$$I_{CC} = I_{QCC} + 2 \times f_{SW\max} C_{sync} V_{ghigh} + 1.18 \times 10^{-8} f_{SW\max} = 13.7mA$$

d. 電源の直列抵抗とゲート抵抗の設計、及び熱的考察

ゲート・ループの全パターン長を 15mm (0.6 インチ) と仮定すると、 $L_g \approx 15nH$  だから、

$$R_{loop} > 2 \sqrt{\frac{L_g}{C_{iss}}} = 3.97\Omega$$

IR1168 データシートより、駆動回路のダウン抵抗  $r_{down} = 1.2\Omega$

MOSFET 内部ゲート抵抗が  $1\Omega$  であるものと想定します。

したがって、 $R_g > 1.77\Omega$   $R_{g1,2} = 1.8\Omega$  を選択

ここでシステムを熱的に検証します：

$$P_{dr1} = 2 f_{SW\max} E_g = 46.9mW$$

したがって：

$$P_{Rg1} = \left( \frac{R_{g1}}{R_{g1} + R_{Source}} + \frac{R_{g1}}{R_{g1} + R_{Sink}} \right) \times \frac{P_{dr1}}{2} = 19.9mW$$

IC の許容最大接合部温度を  $100^\circ\text{C}$  と想定すると：

$$P_{IC\max} = \frac{T_{Jmax} - T_{IC\_amb}}{R_{g,JA}} = 234mW$$

最高  $V_{cc}$  電圧を次のように計算することができます：

$$V_{CC\max} = \frac{P_{IC\max} + P_{Rg}}{I_{CC}} = 20V$$

利用可能な供給電圧はこの値よりも低いので、IC 電源はコンバータ出力から直接得ることができます（直列抵抗を推奨）：

$$R_{CC} = 50\Omega$$

この抵抗は  $f_{SWmax}$  において最大で 9.4mW 消費します。

### b. デカップリングコンデンサ

出力からシステムに給電されるため、フィルタ機能は望ましいものになります。従って、

$$C_{dc\_min} = \frac{2}{\pi \times f_{SW\_min} \times R_{CC}} = 255nF$$

規格値  $C_{dc} = 270nF$  を選択します。

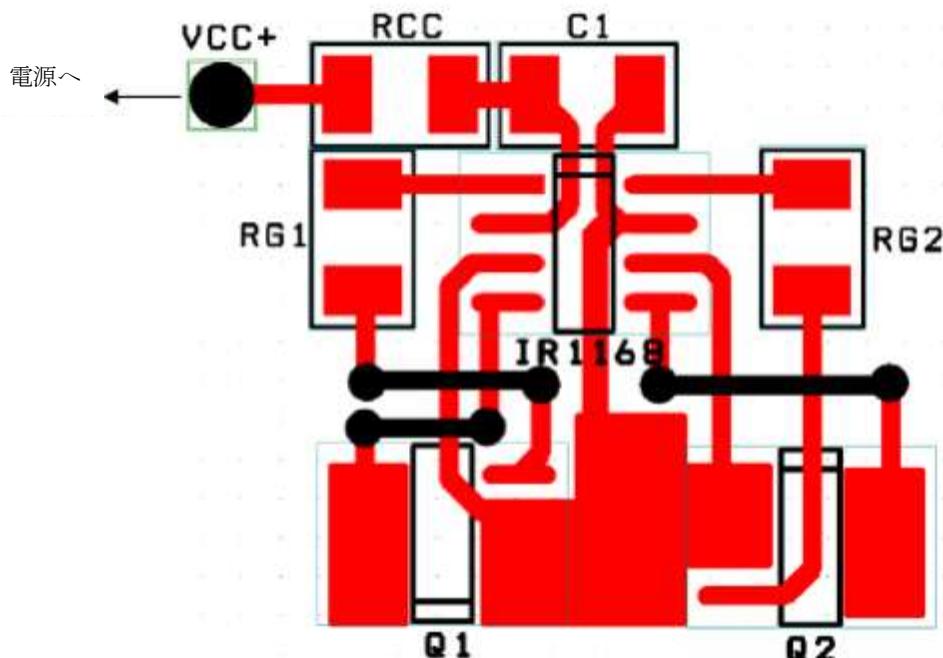

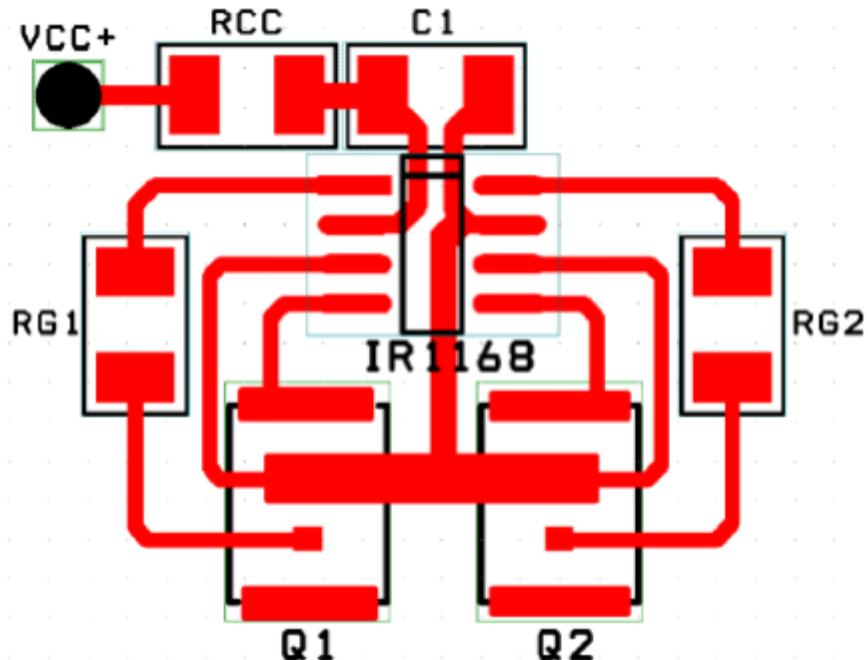

## レイアウトのガイドラインとレイアウト例

### ▽ IC の配置

高速で正確な電圧検出に基づいた制御なので、IR1168 と 2 つの同期整流用 MOSFET をできるだけ近くに配置するように強く推奨します。

### ▽ IC のデカップリング・コンデンサ

適切な IC バイパス機能の重要な要素は、バイパス・コンデンサの位置とコントロール IC の電源ピンとの接続方法です。十分なフィルタ機能を発揮させるためには、コンデンサを  $V_{cc}$  ピンと GND ピンのできるだけ近くに配置して、できる限り短い経路で接続してください。

### ▽ $V_D/V_S$ の差動検出

IR1168 は、両方の同期整流用 MOSFET にかかる差動電圧検出機能を備えています。配線パターン長を最小にして、パワーグランドからできるだけ離してください。MOSFET パッケージ・インダクタンスに関する検出性能の最適化については、付録を参照ください。図 11 に示すように、整流回路の電源ループ内で電流帰還に検出抵抗を使用するとき、検出抵抗を駆動ループ内や検出ループ内に配置しないでください。そうしないと、 $V_{cc}$  に雑音が発生します。この雑音は、デカップリング・コンデンサと  $R_{cc}$  直列抵抗によってフィルタリングされます)。

図 11：出力電流検出抵抗の配置（使用する場合）

▽ ゲート駆動ループ

ゲート駆動ループの長さをできるだけ短くすることで、ループダンピングの要件が減り、システムの堅牢性が高まる。レイアウトを最終決定した後、「大まかに」物理的なループ線の長さ 1mm (1mm = 39.37mils) あたり 1nH と想定して推定をすることができます。これ以外の方法として、測定 (低周波 RCL メーターまたは特定の電圧パルスの電流傾斜) または FEM シミュレーションがあります。

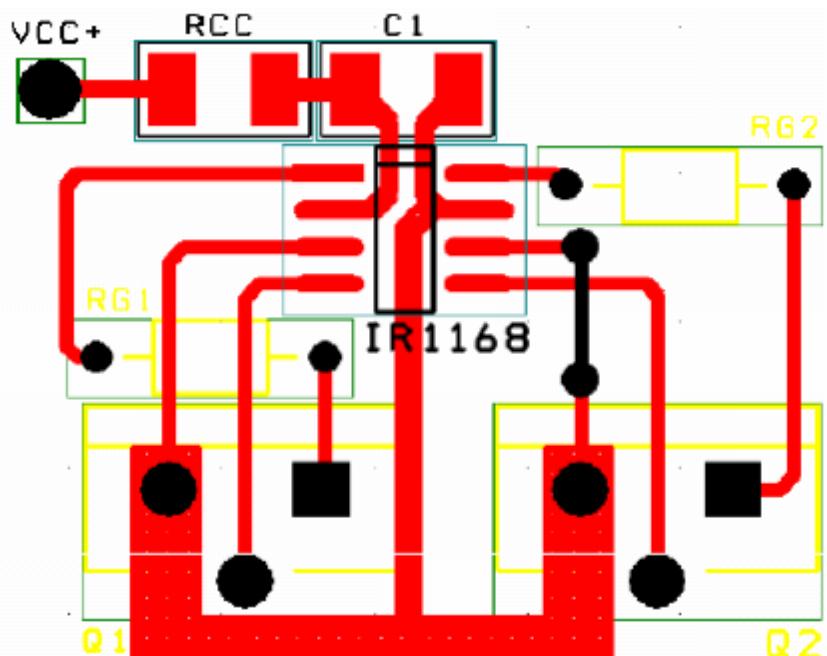

▽ レイアウト例

図 12：単層基板、SO-8 MOSFET 及び表面実装ゲート抵抗

図 13：単層基板、DFET MOSFET 及び表面実装ゲート抵抗

図 14：単層基板、TO-220 MOSFET 及び挿入実装ゲート抵抗

## 付録

### 記号リスト

- $V_{TH1}$  : IR1168 のターン・オフしきい電圧

$V_{TH2}$  : IR1168 のターン・オンしきい電圧

$V_{TH3}$  : IR1168 の周期論理 (リセット) しきい電圧

$R_{AC}$  : 共振タンク AC 解析用の等価 AC 抵抗

$R_{DSon}$  : 同期整流用 MOSFET のチャネルのオン抵抗

$I_D$  : 同期整流用 MOSFET のドレイン電流

$V_{DS}$  : 同期整流用 MOSFET のドレイン-ソース間電圧

MOT : IR1168 のミニマムオンタイムのパラメータ

$t_{blank}$  : IR1168 のターン・オフのブランкиング時間

$C_{dc}$  : IR1168 の  $V_{cc}$  電源デカップリング・コンデンサ

$R_{g1,2}$  : IR1168 に外付けする同期整流用 MOSFET のゲート駆動ループの抵抗値

$R_{CC}$  : 電源の直列抵抗の値 ( $V_{supply}$  と  $V_{cc}$  間)

$f_{SWmax}$  : コンバータの最高動作スイッチング周波数

$f_{SWmin}$  : コンバータの最低動作スイッチング周波数

$Q_g$  : 同期整流用 MOSFET の全ゲート電荷

$Q_{gd}$  : 同期整流用 MOSFET のゲート-ドレイン間電荷 (ミラー電荷)

$V_{gs}$  : 同期整流用 MOSFET のゲート-ソース間電圧

$V_{ghigh}$  : IR1168 のゲート駆動出力電圧

$I_{QCC}$  : IR1168 の静止電流

$L_g$  : ゲート・ループの全寄生インダクタンス

$C_{iss}$  : 同期整流用 MOSFET の入力容量

$E_{g1,2}$  : 各同期整流用 MOSFET のゲートに蓄積したエネルギー

$P_{dr1,2}$  : 各同期整流用 MOSFET のゲート駆動機能の全消費電力

$R_{Source}$  : ゲート駆動のソース (吐き出し) 抵抗

$R_{Sink}$  : ゲート駆動のシンク (吸い込み) 抵抗

$P_{Rg1,2}$  : 各ゲート抵抗で消費される電力

$P_{ICmax}$  : IR1168 の最大消費電力

$T_{IC\_amb}$  : IC の周辺温度 (プリント回路基板の温度)

$R_{θJA}$  : IR1168 の接合部と周囲との間の熱抵抗

$V_{CC}$  : IR1168 のピンの電源電圧

$I_{CC}$  : IR1168 のピンの電源電流

$V_{supply}$  : 同期整流用機能用に使用可能なシステムの電源電圧

$C_{dc\_min}$  : 最小デカップリング・コンデンサの容量値の計算値

$ΔV_{CC}$  : IR1168 の  $V_{cc}$  ピン上のピーク-ピーク間リップル電圧

## References

- [1] IR1168 SmartRectifier™ control IC datasheet, International Rectifier, March 2008.

- [2] “Design of Secondary Side Rectification using IR1167 SmartRectifier™ Control IC” International Rectifier Application Note AN1087, 2006.

- [3] Adnaan Lokhandwala, Maurizio Salato & Marco Soldano “Dual SmartRectifier™ – DirectFET Chipset Solution Overcomes Package Induced Sensing Limitations Allowing High Performance Synchronous Output Rectification in LCD TV Power Supplies”, Proceedings of PCIM China 2007.

- [4] Adnaan Lokhandwala, Maurizio Salato & Marco Soldano “SmartRectifier™ control simplifies output synchronous rectification in DC-DC series resonant converters”, Proceedings of PCIM Europe 2006.