インフィニオンが大学と共同で半導体プロセス欠陥試験チップを開発

独インフィニオンテクノロジーズは、複雑な半導体生産プロセスを試験して改善するための、新しい試験チップ(Test Chip)を製作したと発表しました。これは、独 レーゲンスブルク応用科学大学との数年間に及ぶ緊密な協力の成果です。この試験チップを使えば、以前には超えられなかった精度でプロセス系列を試験でき、また、生産の最中でも測定を行うことによって、マ イクロチップの機能性を最適化できます。その結果、欠陥の発見を早め、生産性を向上させ、生産コストを低減できます。加えて、この試験チップは、め ったに起こらない生産上の問題さえ記録できるほど高い統計的確実性を提供します。

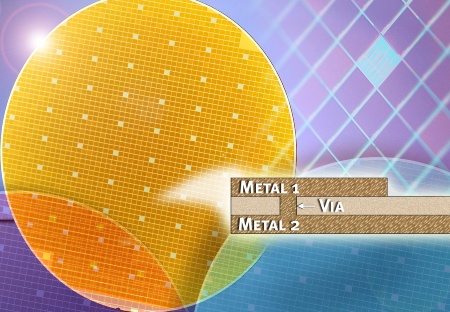

この試験チップは、インフィニオンのレーゲンスブルク工場で開発され、製作され、そこで実地利用されています。このチップは、レ ーゲンスブルク応用科学大学が開発した革新的な回路コンセプトを基にしています。現在、その完全な機能性が実証されつつあります。この試験チップは先ず、レ ーゲンスブルクにあるインフィニオンのウェハ生産施設に採用され、順次、他の生産拠点にも導入される予定です。基本的に言えば、当チップはインテリジェントな汎用アドレス指定回路と、試 験構造を並べたアレイで構成されます。このチップは0.35μm CMOSプロセスを適用し、8インチ・ウェハで作成されます。メモリに類似した構造を持ち、チップ自体は、僅か6平方mmの面積に、1 20万個を超えるトランジスタ機能を含んでいます。

インフィニオンのライナー・ホルマー(レーゲンスブルク、フィラッハおよびミュンヘン工場のCMOS、BICMOSおよびRF技術に対する製品およびプロセス技術責任者)は、「 インフィニオンとレーゲンスブルク応用科学大学は、長年にわたって共同作業を行ってきました。この協力関係では、個 別に編成された研究グループが多様なプロジェクトに業界指向の姿勢で取り組むことに焦点を絞っています。レーゲンスブルク応用科学大学のディーター・コーラート教授の指導の下に行われたこの試験チップの開発は、産 学協同がいかに成果をもたらすかを改めて裏付けます」と、述べました。

試験チップの機能

新開発の試験チップは、2つの金属層間の導電接続部であるバイアの試験に用いられます。先進的なCMOSプロセスにおける、ここで試験しようとするバイアの標準的な故障確率は10~20 ppb( 1ppb=10億分の1)程度にすぎないので、統計的評価を行うには、十分な量の試験データが必要になります。この目的のため、試験チップは512×512個(262,144個)のバイアを並べたアレイと、そ れに所属する、アドレス指定用の選択トランジスタを備えています。1枚のウェハに、試験チップを42個ずつ持つイメージング・ブロックが60個マップされています。従って、ウ ェハ1枚あたりの試験チップ数は2,500個、バイア数は約6億4,000万個にのぼります。各バイアは個別にアドレス指定でき、そのバイアの電気抵抗と電圧降下を正確に測定できます。

意図的に作成したバイア欠陥をテスタで測定することによって、この試験チップの機能性が証明されました。アドレス指定機能のおかげで、チップ上の欠陥箇所が正確に特定されました。従って、このバイア・ アレイ試験チップは、生産プロセスをバイア領域に関して試験するための高感度の試験手段となります。ほんの僅かのプロセス変化によって、バイアの電気特性が影響されます。テスタによる簡単な測定で、そ れを記録できます。この試験チップのコンセプトは、レーゲンスブルク応用科学大学との協力でさらに開発が進められています。その目標は、回路の信頼性と生産性向上を確保するため、チ ップ生産工程でバイア以外のプロセス・ステップを検査できるようにすることです。

インフィニオンについて

インフィニオンテクノロジーズ(Infineon Technologies AG)は、ドイツのミュンヘンに本社を置き、自 動車および産業分野や有線通信市場のアプリケーションへ向けた半導体およびシステムソリューション、セキュア・モバイル・ソリューション、メモリ製品などを供給しています。米国ではカリフォルニア州サンノゼ、ア ジア太平洋地域ではシンガポール、そして日本では東京を拠点として活動しています。2003会計年度(9月決算)の売上高は61億5,000万ユーロ、2003年9月末の従業員数は約32,300名でした。イ ンフィニオンは、フランクフルトとニューヨークの証券取引所に株式上場されています。

Information Number

INFCPR200309.128