インフィニオンテクノロジーズが線幅40~50nmのIC配線技術を公開

独インフィニオンテクノロジーズは、現 在のIC配線技術が2011年から2014年に登場する未来世代のチップにも引き続き使用できることを同社のミュンヘン研究所(コーポレート・リサーチ・ラボ)が実証することに成功した、と発表しました。

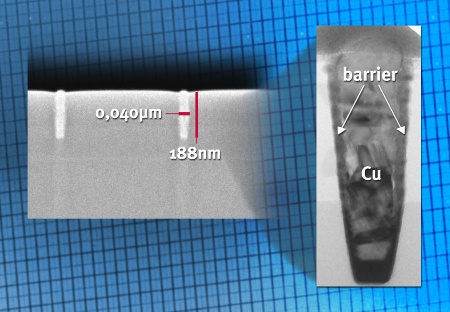

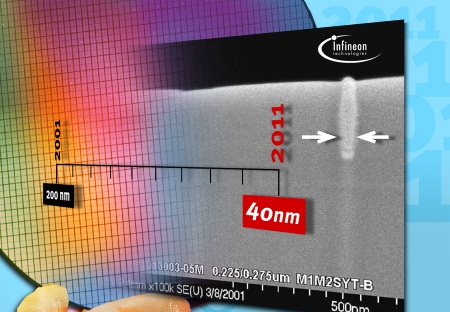

インフィニオンの研究者は、絶縁膜の溝の中に、線幅40nmないし50nmの金属配線を製造することに成功しました。こうした微細な金属配線は、チ ップ中のトランジスタ間を最短距離で電気接続するために使用されます。

この金属配線の電気的評価で、対象としたすべての線長にわたって、十分に低いレベルの電気抵抗が得られることが検証されました。このことは、超微細配線の製造も電気抵抗のいずれも、チ ップ微細化を進める上で、なんら障害とならないことを示しています。

2011~2014年の未来世代チップの製造に必要なリソグラフィ装置は、まだ存在していません。インフィニオンはこの状況を克服するために、スペーサ技術を利用して、パ ターンを絶縁膜へ転写するためのマスクの開口部を狭めました。この技術により、横方向寸法に関して、今日の最先端リソグラフィ装置が本来実現できる線幅をはるかに下回る構造を製造することが可能になります。

今回の成果は、半導体業界における先進チップ配線のための最新のアプローチである、いわゆるダマシン技術が、今後も長期にわたって有効な技術となる可能性を裏付けるものです。ダマシン技術では、ウ エハ上の溝や穿孔を金属で埋め、その後に、埋め込み構造を覆うすべての余分な金属をCMP(化学機械研磨)法によって完全に除去します。この方法は、ダマスク刀剣の装飾のために使用された象嵌技術にちなんで、ダ マシン法と名づけられたものです。

実証用シリコンウエハは、世界の有力半導体メーカーをメンバーとするInternational Sematechのクリーンルーム(テキサス州オースチン)で、線 幅250nmの微細化技術のために開発された今日の標準半導体製造装置とプロセスを使って処理加工されました。

インフィニオン研究所の今回の成果は、今日の配線技術がITRS(半導体のための国際技術ロードマップ)の最終年次である2014年まで使用可能であることを実証しました。未 来世代のICのために必要な技術・材料への要求をまとめたのが、このロードマップです。

インフィニオンの研究者は、絶縁膜の溝の中に、線幅40nmないし50nmの金属配線を製造することに成功しました。こうした微細な金属配線は、チ ップ中のトランジスタ間を最短距離で電気接続するために使用されます。

この金属配線の電気的評価で、対象としたすべての線長にわたって、十分に低いレベルの電気抵抗が得られることが検証されました。このことは、超微細配線の製造も電気抵抗のいずれも、チ ップ微細化を進める上で、なんら障害とならないことを示しています。

2011~2014年の未来世代チップの製造に必要なリソグラフィ装置は、まだ存在していません。インフィニオンはこの状況を克服するために、スペーサ技術を利用して、パ ターンを絶縁膜へ転写するためのマスクの開口部を狭めました。この技術により、横方向寸法に関して、今日の最先端リソグラフィ装置が本来実現できる線幅をはるかに下回る構造を製造することが可能になります。

今回の成果は、半導体業界における先進チップ配線のための最新のアプローチである、いわゆるダマシン技術が、今後も長期にわたって有効な技術となる可能性を裏付けるものです。ダマシン技術では、ウ エハ上の溝や穿孔を金属で埋め、その後に、埋め込み構造を覆うすべての余分な金属をCMP(化学機械研磨)法によって完全に除去します。この方法は、ダマスク刀剣の装飾のために使用された象嵌技術にちなんで、ダ マシン法と名づけられたものです。

実証用シリコンウエハは、世界の有力半導体メーカーをメンバーとするInternational Sematechのクリーンルーム(テキサス州オースチン)で、線 幅250nmの微細化技術のために開発された今日の標準半導体製造装置とプロセスを使って処理加工されました。

インフィニオン研究所の今回の成果は、今日の配線技術がITRS(半導体のための国際技術ロードマップ)の最終年次である2014年まで使用可能であることを実証しました。未 来世代のICのために必要な技術・材料への要求をまとめたのが、このロードマップです。

インフィニオンについて

Information Number

INFCPR200105.072e

Press Photos

-

Infineon Technologies Demonstrates Technique To Shrink Wiring of Integrated Circuits To Widths of 40 - 50 Nanometers; Meeting Requirements For Chip Manufacture Into Next DecadePress Picture

Infineon Technologies Demonstrates Technique To Shrink Wiring of Integrated Circuits To Widths of 40 - 50 Nanometers; Meeting Requirements For Chip Manufacture Into Next DecadePress PictureJPG | 335 kb | 1535 x 1063 px

-

Infineon Technologies Demonstrates Technique To Shrink Wiring of Integrated Circuits To Widths of 40 - 50 Nanometers; Meeting Requirements For Chip Manufacture Into Next DecadePress Picture

Infineon Technologies Demonstrates Technique To Shrink Wiring of Integrated Circuits To Widths of 40 - 50 Nanometers; Meeting Requirements For Chip Manufacture Into Next DecadePress PictureJPG | 428 kb | 1535 x 1063 px