For development support, the partners offer

the FPGA HSSL Starter Kit

Kit description

The logiHSSL-ZU FPGA HSSL Starter Kit designs provides system designers with everything they need to quickly interconnect the Infineon’s AURIX™ microcontrollers with the Xilinx All Programmable FPGA and SoC devices via the Infineon High Speed Serial Link (HSSL). Combinations of these devices solve the rising safety and performance requirements in emerging automotive and industrial designs.

Kit content :

- Combines Infineon's AURIX™ microcontroller and Xilinx's UltraScale+ MPSoC programmable device

- Integrates Infineon High Speed Serial Link (HSSL) optimized for Xilinx FPGA implementations

- Includes complete reference design with the evaluation logiHSSL IP core

- Design is prepared for Xilinx Vivado® Design Suite

- Linked devices can access and control each other's resources

- Complete hardware platform includes:

- 1x Xilinx Zynq UltraScale+ MPSoC ZCU104 Evaluation Kit

- 1x Infineon Aurix Evaluation Board Kit KIT_A2G_TC397_5V_TRB_S

- 1x Xylon FMC board for cable connection

- 1x FireWire cable

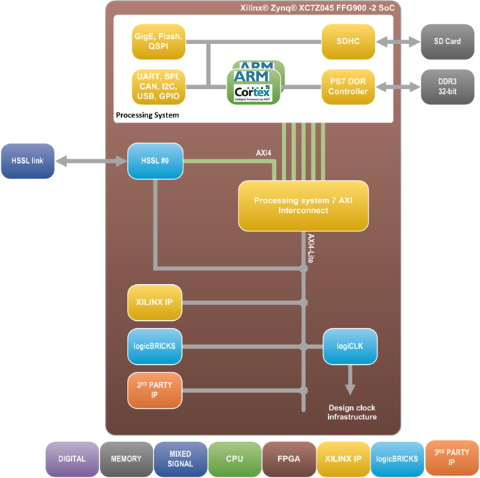

Zynq-7000 SoC Demo Design Example – Block Diagram

- The HSSL IP core (HSSL #0) can access register sets of all SoC IP cores through the PS 7 AXI Interconnect

- The HSSL control module can access internal HSCT, HSSL and BCU register space through the same AXI infrastructure

- HSSL IP core can access PS register space and on-board memory through GP and HP AXI3 ports on PL-PS interface

- Programmable logiCLK IP core changes clocking on the fly and enables HSSL IP core setup to the required baud rate

Documentation and technical Support

Xylon technical support

Infineon technical support

- Please register under myinfineon.com (hyperlink) with your company e-mail address

- Send login name to: AURIX@infineon.com

- Automated update service will be provided for new documents once you are registered

- Full registration process can take up to 24h to be completed (due to different time zones).

Click here to see the step-by-step instructions to get registered.