Infineon demonstrierte erfolgreiche Miniaturisierung von Diffusions-Barrieren in den Nanotechnologie-Bereich: Ein bedeutender Schritt zur Sicherstellung der leistungsfähigen Metallisierung für künftige Chip-Generationen

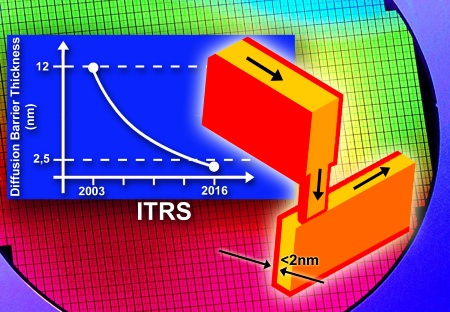

München, 27. Mai 2003 Einem Forschungsteam von Infineon Technologies ist es gelungen, durch die weitere Verkleinerung von so genannten Diffusions-Barrieren in den Bereich von Nanotechnologie-Strukturen, extrem dünne Sperrschichten für die anspruchsvollen Metallisierungstechniken künftiger Chip-Generationen zu fertigen. Die Forschungsergebnisse belegen, dass es möglich ist, ultradünne Diffusions-Sperrschichten zu fertigen, die zur Sicherstellung der Chipfunktionalität von der International Roadmap for Semiconductors (ITRS) bis 2016 gefordert werden. Die ITRS erwartet eine Verringerung der Barrieren-Dicke von derzeit 12 nm (100-nm-Prozess-Technologie, 2003) bis auf nur noch 2,5 nm (22-nm-Technologie, 2016). Wesentliche Zielsetzung der Infineon Forscher war es, die weitere Reduzierung der bisherigen Ta/TaN-Sperrschichten soweit voranzutreiben, dass die Vorgaben der ITRS-Roadmap erfüllt werden können.

Das Forschungsteam von Infineon konnte in einem Demonstrationsaufbau extrem dünne metallische Sperrschichten integrieren, die zur hermetischen Einkapselung der Kupferleiterbahnen in den Metallisierungsebenen künftiger Chips erforderlich sind. Die elektrisch leitenden Schichten trennen die Kupferleitungen von der umgebenden dielektrischen Schicht, die für die Isolation sorgt. Die Einkapselung der Kupferleitung ist notwendig, da sonst das Kupfer in das Dielektrikum diffundiert und sowohl die elektrische Isolation als auch die darunter liegenden Transistorschaltungen zerstören kann.

Um die bestmögliche Chip-Performance bzw. -Geschwindigkeit zu erreichen, müssen die Barrieren so dünn wie möglich sein, und zwar aus zwei Gründen: Sehr dünne Sperrschichten lassen einerseits genug Platz für die leitenden Kupferbahnen. Darüber hinaus muss der Strom bei den vertikalen Verbindungen zwischen den Metallisierungsebenen (über so genannte Vias) auch durch die Sperrschichten fließen können - wobei der elektrische Widerstand direkt proportional zur Dicke der Schicht ist.

Die Untersuchungen von Infineon haben gezeigt, dass auch bei Dicken von weniger als 2 nm keine Kupfer-Diffusion auftritt. Damit sind diese ultradünnen Sperrschichten ebenso zuverlässig wie die derzeit in Produkten verwendeten Diffusions-Barrieren mit Dicken von 50 nm. Darüber hinaus ist der elektrische Widerstand in den Vias durch diese sehr dünnen Schichten ausreichend klein, um die hohen Geschwindigkeitsanforderungen erfüllen zu können, wie sie z.B. Mikroprozessoren haben, die voraussichtlich Mitte des nächsten Jahrzehnts gefertigt werden.

Durch den geringen elektrischen Widerstand und die ausgezeichnete Widerstandsfähigkeit gegenüber Elektromigration bietet Kupfer klare Vorteile für leistungsfähige ICs. Damit Kupfer auch das bevorzugte Material für die Metallisierung in künftigen Chip-Generationen sein kann, muss großes Augenmerk auf die Vermeidung der Kupfer-Diffusion gelegt werden, sagte Prof. Dr. Karl Joachim Ebeling, Forschungsleiter bei Infineon Technologies. Die jetzt erreichten Ergebnisse markieren einen wesentlichen Schritt bei der Bereitstellung der anspruchsvollen Technologien für die Fertigung der nächsten, weiter miniaturisierten Chip-Generationen.

Die Fertigungsgeräte und -einrichtungen für die Produktion der Chipgenerationen in 2010 und später stehen noch nicht zur Verfügung. Für seine Untersuchungen hat Infineon daher bestehende Prozesse und Tools über den heutigen Anwendungsbereich hinaus ausgereizt. Dadurch konnte eine zuverlässige Aufbringung von Diffusions-Barrieren mit weniger als 2 nm Dicke realisiert werden. Derart dünne Schichten sind erforderlich, um die äußerst leistungsfähigen Mikroprozessoren fertigen zu können, wie sie ab 2016 erwartet werden. Die Ergebnisse lassen darüber hinaus auch erwarten, dass die derzeit genutzten Abscheide-Techniken beim Aufbau der Schaltungsstrukturen auch bei künftigen Chip-Generationen angewandt werden können, und neue aufwendige Technologien wie z.B. Atomic-Layer-Deposition erst später als bisher angenommen zum Einsatz kommen werden.

Die Kupferleitungen wurden mit der so genannten Damascene-Technik gefertigt. Benannt nach dem Verfahren, mit dem die Ornamente in den berühmten Damaszenischen Schwertern erstellt wurden - werden hier die geätzten Gräben und Löcher mit Metall aufgefüllt. Nachdem die überstehenden Metallbereiche durch ein chemisch-mechanisches Polierverfahren wieder abgetragen werden, entstehen extrem schmale Metallleitungen. Diese Metallleitungen werden für die sehr schnellen Verbindungen der Schaltungselemente auf zukünftigen Chips verwendet. Die Silizium-Wafer für den Versuchsaufbau wurden in den Reinräumen von Infineon auf Basis von Standard-Prozessen und -Tools gefertigt.

Die Forschungsergebnisse von Infineon zeigen, dass die von der IRTS für 2016 geforderten extrem dünnen Barriere-Schichten den elektrischen und funktionellen Ansprüchen gerecht werden und produzierbar sind. Die ITRS beschreibt die technologischen und Material-Anforderungen an künftige Chip-Generationen. In Bezug auf die Metallisierung sieht die derzeit gültige Version der IRTS die erforderlichen sehr dünnen Diffusions-Barrieren als nicht produzierbar an. Infineon konnte nun demonstrieren, dass diese dünnen Schichten durch Fortschreibung der bestehenden Technologien mit der geforderten Performance gefertigt werden können. Es wird erwartet, dass die nächste Ausgabe der ITRS diese Ergebnisse entsprechend berücksichtigt.

Infineon Technologies AG, München, bietet Halbleiter- und Systemlösungen für die Automobil- und Industrieelektronik, für Anwendungen in der drahtgebundenen Kommunikation, sichere Mobilfunk-Lösungen sowie Speicherbauelemente. Infineon ist weltweit tätig und steuert seine Aktivitäten in den USA aus San Jose, Kalifornien, im asiatisch-pazifischen Raum aus Singapur und in Japan aus Tokio. Mit weltweit rund 30.400 Mitarbeitern erzielte Infineon im Geschäftsjahr 2002 (Ende September) einen Umsatz von 5,21 Milliarden Euro. Das DAX-Unternehmen ist in Frankfurt und New York (NYSE) unter dem Symbol IFX notiert. Weitere Informationen unter http://www.infineon.com.

Das Forschungsteam von Infineon konnte in einem Demonstrationsaufbau extrem dünne metallische Sperrschichten integrieren, die zur hermetischen Einkapselung der Kupferleiterbahnen in den Metallisierungsebenen künftiger Chips erforderlich sind. Die elektrisch leitenden Schichten trennen die Kupferleitungen von der umgebenden dielektrischen Schicht, die für die Isolation sorgt. Die Einkapselung der Kupferleitung ist notwendig, da sonst das Kupfer in das Dielektrikum diffundiert und sowohl die elektrische Isolation als auch die darunter liegenden Transistorschaltungen zerstören kann.

Um die bestmögliche Chip-Performance bzw. -Geschwindigkeit zu erreichen, müssen die Barrieren so dünn wie möglich sein, und zwar aus zwei Gründen: Sehr dünne Sperrschichten lassen einerseits genug Platz für die leitenden Kupferbahnen. Darüber hinaus muss der Strom bei den vertikalen Verbindungen zwischen den Metallisierungsebenen (über so genannte Vias) auch durch die Sperrschichten fließen können - wobei der elektrische Widerstand direkt proportional zur Dicke der Schicht ist.

Die Untersuchungen von Infineon haben gezeigt, dass auch bei Dicken von weniger als 2 nm keine Kupfer-Diffusion auftritt. Damit sind diese ultradünnen Sperrschichten ebenso zuverlässig wie die derzeit in Produkten verwendeten Diffusions-Barrieren mit Dicken von 50 nm. Darüber hinaus ist der elektrische Widerstand in den Vias durch diese sehr dünnen Schichten ausreichend klein, um die hohen Geschwindigkeitsanforderungen erfüllen zu können, wie sie z.B. Mikroprozessoren haben, die voraussichtlich Mitte des nächsten Jahrzehnts gefertigt werden.

Durch den geringen elektrischen Widerstand und die ausgezeichnete Widerstandsfähigkeit gegenüber Elektromigration bietet Kupfer klare Vorteile für leistungsfähige ICs. Damit Kupfer auch das bevorzugte Material für die Metallisierung in künftigen Chip-Generationen sein kann, muss großes Augenmerk auf die Vermeidung der Kupfer-Diffusion gelegt werden, sagte Prof. Dr. Karl Joachim Ebeling, Forschungsleiter bei Infineon Technologies. Die jetzt erreichten Ergebnisse markieren einen wesentlichen Schritt bei der Bereitstellung der anspruchsvollen Technologien für die Fertigung der nächsten, weiter miniaturisierten Chip-Generationen.

Die Fertigungsgeräte und -einrichtungen für die Produktion der Chipgenerationen in 2010 und später stehen noch nicht zur Verfügung. Für seine Untersuchungen hat Infineon daher bestehende Prozesse und Tools über den heutigen Anwendungsbereich hinaus ausgereizt. Dadurch konnte eine zuverlässige Aufbringung von Diffusions-Barrieren mit weniger als 2 nm Dicke realisiert werden. Derart dünne Schichten sind erforderlich, um die äußerst leistungsfähigen Mikroprozessoren fertigen zu können, wie sie ab 2016 erwartet werden. Die Ergebnisse lassen darüber hinaus auch erwarten, dass die derzeit genutzten Abscheide-Techniken beim Aufbau der Schaltungsstrukturen auch bei künftigen Chip-Generationen angewandt werden können, und neue aufwendige Technologien wie z.B. Atomic-Layer-Deposition erst später als bisher angenommen zum Einsatz kommen werden.

Die Kupferleitungen wurden mit der so genannten Damascene-Technik gefertigt. Benannt nach dem Verfahren, mit dem die Ornamente in den berühmten Damaszenischen Schwertern erstellt wurden - werden hier die geätzten Gräben und Löcher mit Metall aufgefüllt. Nachdem die überstehenden Metallbereiche durch ein chemisch-mechanisches Polierverfahren wieder abgetragen werden, entstehen extrem schmale Metallleitungen. Diese Metallleitungen werden für die sehr schnellen Verbindungen der Schaltungselemente auf zukünftigen Chips verwendet. Die Silizium-Wafer für den Versuchsaufbau wurden in den Reinräumen von Infineon auf Basis von Standard-Prozessen und -Tools gefertigt.

Die Forschungsergebnisse von Infineon zeigen, dass die von der IRTS für 2016 geforderten extrem dünnen Barriere-Schichten den elektrischen und funktionellen Ansprüchen gerecht werden und produzierbar sind. Die ITRS beschreibt die technologischen und Material-Anforderungen an künftige Chip-Generationen. In Bezug auf die Metallisierung sieht die derzeit gültige Version der IRTS die erforderlichen sehr dünnen Diffusions-Barrieren als nicht produzierbar an. Infineon konnte nun demonstrieren, dass diese dünnen Schichten durch Fortschreibung der bestehenden Technologien mit der geforderten Performance gefertigt werden können. Es wird erwartet, dass die nächste Ausgabe der ITRS diese Ergebnisse entsprechend berücksichtigt.

Über Infineon

Infineon Technologies AG, München, bietet Halbleiter- und Systemlösungen für die Automobil- und Industrieelektronik, für Anwendungen in der drahtgebundenen Kommunikation, sichere Mobilfunk-Lösungen sowie Speicherbauelemente. Infineon ist weltweit tätig und steuert seine Aktivitäten in den USA aus San Jose, Kalifornien, im asiatisch-pazifischen Raum aus Singapur und in Japan aus Tokio. Mit weltweit rund 30.400 Mitarbeitern erzielte Infineon im Geschäftsjahr 2002 (Ende September) einen Umsatz von 5,21 Milliarden Euro. Das DAX-Unternehmen ist in Frankfurt und New York (NYSE) unter dem Symbol IFX notiert. Weitere Informationen unter http://www.infineon.com.

Informationsnummer

INFCPR200305.083

Pressefotos

-

Infineon Technologies Demonstrates Shrinking of Barrier Films into Nanotechnology Geometries: Milestone to Fulfill Metallization Requirements for Chip Manufacturing into Next DecadeShrinking of Barrier Films

Infineon Technologies Demonstrates Shrinking of Barrier Films into Nanotechnology Geometries: Milestone to Fulfill Metallization Requirements for Chip Manufacturing into Next DecadeShrinking of Barrier FilmsJPG | 402 kb | 1535 x 1063 px

Shrinking of Barrier FilmsJPG | 17 kb | 160 x 111 px