Infineon präsentiert neue konfigurierbare CARMEL DSP-Cores für leistungsfähige 3G-Mobilfunk- und Breitband-Kommunikations-Anwendungen

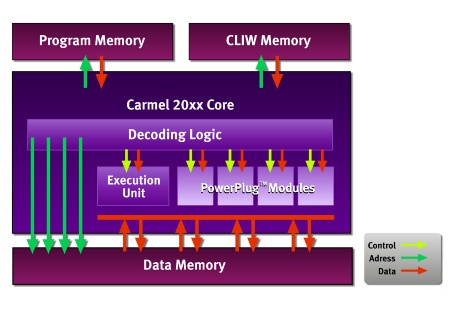

München, 27. März 2000 Zur weiteren Stärkung seiner Position für 3G-(dritte Generation)-Mobilfunk- sowie Breitband-Kommunikations-Anwendungen stellt Infineon Technologies heute eine neue Generation seines 16-Bit-Festkomma-DSP-Cores CARMEL vor. Der 20xx-Core verfügt über einen PowerPlug-Beschleuniger, der es SoC-(System on Chip)-Entwicklern ermöglicht, den Befehlssatz des Cores zu konfigurieren. Damit können rechenintensive Funktionalitäten wie mehrfache Datenraten oder komplexe Modulationen ohne Kompromisse bei der Leistungsaufnahme oder bei den Systemkosten effizient implementiert werden.

Mit den PowerPlug-Modulen von Infineon können Systementwickler mit Hilfe der Neukonfigurierung des Cores die Ausführung von applikationsspezifischen Funktionen erheblich beschleunigen. Diese PowerPlug-Module sind eng gekoppelt mit dem CARMEL DSP-Core und werden von der Software genauso optimal wie die bereits fest eingebauten Ausführungseinheiten im DSP-Datenpfad verwendet. Die Module ermöglichen eine Skalierung von Hard- und Software sowie die Optimierung hinsichtlich Kosten und Geschwindigkeit.

Die PowerPlug-Technologie kombiniert die Preis- und Leistungsvorteile von ASICs mit der Flexibilität eines programmierbaren DSP, sagte Shaul Berger, Vice President DSP Cores von Infineon Technologies. Die skalierbare Architektur des CARMEL DSP 20xx-Cores ermöglicht unseren Kunden, preiswerte 3G-Mobilfunk- und Breitband-Kommunikationsprodukte schneller auf den Markt zu bringen.

Der Befehlssatz des Cores ist eine Obermenge der Befehle des CARMEL DSP 10xx-Cores und nutzt die CLIW-Architektur (Configurable Long Instruction Word). Die CLIW-Technologie kombiniert dabei die Vorteile von VLIW (Very Long Instruction Word) hinsichtlich Geschwindigkeit und flexibler Steuerung mit dem kompakten Code und der geringen Leistungsaufnahme von SIMD (Single Instruction Multiple Data). Die sonst üblichen Einschränkungen bei der Code-Größe und Leistungsaufnahme von anderen VLIW-Architekturen werden damit vermieden.

Der CARMEL DSP20xx-Core bietet an sich schon Frequenzen von bis zu 300 Megahertz. Mit der PowerPlug-Erweiterung kann der Code-effiziente DSP-Core die Performance des Cores verdoppeln, ohne dass sich die Leistungsaufnahme dabei wesentlich erhöht. Die durch die PowerPlug-Technologie erzielbare zusätzliche Verarbeitungsleistung erfüllt die hohen Anforderungen von Mobilfunk- sowie Breitband-Applikationen, wo hohe Datenübertragungsraten und die Integration von Sprache, Daten und Video von Bedeutung ist. Auch bei der Leistungsaufnahme bietet der CARMEL DSP 20xx-Core Möglichkeiten zur Optimierung des Systems, um die Batterie-Lebensdauer zu erhöhen und stromsparende Speicher-Management-Funktionen zu unterstützen. Besonders neue mobile Applikationen im 3G-Bereich werden davon profitieren.

Der CARMEL DSP 20xx-Core wird ab dem vierten Quartal 2000 verfügbar sein. Weitere Informationen über die CARMEL-DSP-Architektur von Infineon sind unter www.infineon.com/dsp verfügbar.

Infineon Technologies AG, München, bietet Halbleiterlösungen für die Anwendungen in der mobilen und drahtgebundenen Kommunikation, für die Automobil- und Industrieelektronik, für Sicherheitssysteme und Chipkarten sowie Speicherbauelemente. Infineon ist weltweit tätig und steuert seine Aktivitäten in den USA aus San Jose, Kalifornien, und im asiatisch-pazifischen Raum aus Singapur. Mit weltweit rund 26.000 Mitarbeitern erzielte Infineon im Geschäftsjahr 1999 (Ende September) einen Umsatz von 4,24 Milliarden Euro. Weitere Informationen unter www.infineon.com

Mit den PowerPlug-Modulen von Infineon können Systementwickler mit Hilfe der Neukonfigurierung des Cores die Ausführung von applikationsspezifischen Funktionen erheblich beschleunigen. Diese PowerPlug-Module sind eng gekoppelt mit dem CARMEL DSP-Core und werden von der Software genauso optimal wie die bereits fest eingebauten Ausführungseinheiten im DSP-Datenpfad verwendet. Die Module ermöglichen eine Skalierung von Hard- und Software sowie die Optimierung hinsichtlich Kosten und Geschwindigkeit.

Die PowerPlug-Technologie kombiniert die Preis- und Leistungsvorteile von ASICs mit der Flexibilität eines programmierbaren DSP, sagte Shaul Berger, Vice President DSP Cores von Infineon Technologies. Die skalierbare Architektur des CARMEL DSP 20xx-Cores ermöglicht unseren Kunden, preiswerte 3G-Mobilfunk- und Breitband-Kommunikationsprodukte schneller auf den Markt zu bringen.

Der Befehlssatz des Cores ist eine Obermenge der Befehle des CARMEL DSP 10xx-Cores und nutzt die CLIW-Architektur (Configurable Long Instruction Word). Die CLIW-Technologie kombiniert dabei die Vorteile von VLIW (Very Long Instruction Word) hinsichtlich Geschwindigkeit und flexibler Steuerung mit dem kompakten Code und der geringen Leistungsaufnahme von SIMD (Single Instruction Multiple Data). Die sonst üblichen Einschränkungen bei der Code-Größe und Leistungsaufnahme von anderen VLIW-Architekturen werden damit vermieden.

Der CARMEL DSP20xx-Core bietet an sich schon Frequenzen von bis zu 300 Megahertz. Mit der PowerPlug-Erweiterung kann der Code-effiziente DSP-Core die Performance des Cores verdoppeln, ohne dass sich die Leistungsaufnahme dabei wesentlich erhöht. Die durch die PowerPlug-Technologie erzielbare zusätzliche Verarbeitungsleistung erfüllt die hohen Anforderungen von Mobilfunk- sowie Breitband-Applikationen, wo hohe Datenübertragungsraten und die Integration von Sprache, Daten und Video von Bedeutung ist. Auch bei der Leistungsaufnahme bietet der CARMEL DSP 20xx-Core Möglichkeiten zur Optimierung des Systems, um die Batterie-Lebensdauer zu erhöhen und stromsparende Speicher-Management-Funktionen zu unterstützen. Besonders neue mobile Applikationen im 3G-Bereich werden davon profitieren.

Der CARMEL DSP 20xx-Core wird ab dem vierten Quartal 2000 verfügbar sein. Weitere Informationen über die CARMEL-DSP-Architektur von Infineon sind unter www.infineon.com/dsp verfügbar.

Über Infineon

Infineon Technologies AG, München, bietet Halbleiterlösungen für die Anwendungen in der mobilen und drahtgebundenen Kommunikation, für die Automobil- und Industrieelektronik, für Sicherheitssysteme und Chipkarten sowie Speicherbauelemente. Infineon ist weltweit tätig und steuert seine Aktivitäten in den USA aus San Jose, Kalifornien, und im asiatisch-pazifischen Raum aus Singapur. Mit weltweit rund 26.000 Mitarbeitern erzielte Infineon im Geschäftsjahr 1999 (Ende September) einen Umsatz von 4,24 Milliarden Euro. Weitere Informationen unter www.infineon.com

Informationsnummer

INFCMD200003.050e

Pressefotos

-

Infineon Technologies Carmel 20xx Architecture, Block Diagram of PowerPlug Module Interface.Press Picture

Infineon Technologies Carmel 20xx Architecture, Block Diagram of PowerPlug Module Interface.Press PictureJPG | 259 kb | 1535 x 1063 px